Fターム[5F033PP12]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065) | プラズマCVD (289)

Fターム[5F033PP12]に分類される特許

41 - 60 / 289

半導体装置の製造方法

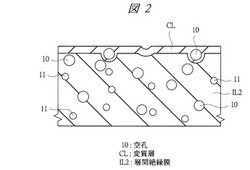

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】プラズマCVD法によって層間絶縁膜IL2を形成する際にCVD装置内に供給するポロジェンの流量を、ポロジェンおよびメチルジエトキシシランの合計の流量の30%以上60%以下とすることで、層間絶縁膜IL2内に形成される空孔10の大きさを小さくし、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

導電性素子およびその製造方法、配線素子、情報入力装置、表示装置、ならびに電子機器

【課題】優れたスループットを実現できる導電性素子を提供する。

【解決手段】導電性素子は、第1の波面および第2の波面を有する基体と、第1の波面上に形成された導電層とを備える。導電層は、導電パターン部を形成し、第1の波面および第2の波面が、0≦(Am1/λm1)<(Am2/λm2)≦1.8(但し、Am1:第1の波面の振動の平均幅、Am2:第2の波面の振動の平均幅、λm1:第1の波面の平均波長、λm2:第2の波面の平均波長)の関係を満たす。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

空隙組込みの構造体及び方法

【課題】 空隙を組み込んだ構造体及びその形成方法を提供する。

【解決手段】 VLSI及びULSI用の空隙含有金属・絶縁体相互接続構造体を、光パターン化可能低k材料を用いて作成する方法、及び形成した空隙含有金属・絶縁体相互接続構造体を開示する。より具体的には、本明細書で説明する方法は、内部に種々異なる深さの空隙がフォトリソグラフィにより画定された光パターン化可能低k材料の内部に構築される相互接続構造体を提供する。本発明の方法においては、空隙を形成するのにエッチ・ステップは必要としない。光パターン化可能低k材料内部の空隙を形成するのに、エッチ・ステップを必要としないで、本発明において開示する方法は、高信頼性の相互接続構造体を提供する。

(もっと読む)

カーボンナノチューブの形成方法及びカーボンナノチューブ成膜装置

【課題】被処理体上のビアホールや配線用溝等の開口部に高密度にカーボンナノチューブ膜を埋め込むことができるカーボンナノチューブの形成方法を提供する。

【解決手段】表面に1又は複数の開口部を有し、当該開口部底面に触媒金属層が形成された被処理体を準備し(STEP1)、触媒金属層に酸素プラズマ処理を施し(STEP2)、酸素プラズマ処理後の触媒金属層に水素含有プラズマ処理を施して、触媒金属層の表面を活性化し(STEP3)、その後、触媒金属層の上にプラズマCVDによりカーボンナノチューブを成長させて、被処理体の開口部内をカーボンナノチューブで充填する(STEP5)。

(もっと読む)

薄膜素子用基板の製造方法、薄膜素子の製造方法、薄膜トランジスタの製造方法、薄膜素子、および薄膜トランジスタ

【課題】本発明は、表面平滑性に優れ、薄膜素子の特性劣化を抑制することが可能な薄膜素子用基板が得られる新規な薄膜素子用基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、金属基材に薬液処理を施す金属基材表面処理工程と、上記金属基材上にポリイミド樹脂組成物を塗布して絶縁層を形成する絶縁層形成工程とを有し、上記絶縁層の表面粗さRaが30nm以下であることを特徴とする薄膜素子用基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

パターン形成体の製造方法、機能性素子の製造方法および半導体素子の製造方法

【課題】本発明は、高精細なパターニングが可能なパターン形成体の効率的な製造方法を提供することを主目的とする。

【解決手段】本発明は、基板上に形成され、表面が疎水性を示す疎水性層上にフォトレジストパターンを形成するフォトレジストパターン形成工程と、上記フォトレジストパターンが形成された上記疎水性層の表面にエネルギーを照射して親水化し、親水性領域を形成する親水化工程と、上記フォトレジストパターンを剥離し、上記疎水性層表面に、上記親水性領域と上記親水化工程にて上記フォトレジストパターンで覆われていた疎水性領域とがパターン状に形成された親疎水パターンを形成するフォトレジストパターン剥離工程とを有することを特徴とするパターン形成体の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

基板の配線方法及び半導体製造装置

【課題】基板上に形成された配線用パターンの底部までCu埋め込みが可能な基板の配線方法を提供する。

【解決手段】真空状態に保持された処理容器100内にて配線用パターンが形成された基板を配線する方法であって、ウエハ上の配線用パターンを所望のクリーニングガスにより洗浄する前工程と、前工程後、クラスタ化された金属ガス(金属ガスクラスタCg)を用いて配線用パターン内に金属ナノ粒子を埋め込む埋め込み工程と、を含むことを特徴とする基板の配線方法が提供される。

(もっと読む)

電子デバイスの製造方法

【課題】カーボン膜の抵抗率を低減することができる電子デバイスの製造方法を提供する。

【解決手段】基板11が載置されたチャンバ4内に炭素を含有する原料ガスを供給する。基板11の周囲からチャンバ4内のアノード1に向けて電子を放出させてチャンバ4内にプラズマ14を発生させ、基板11上にグラファイト、グラフェン等のカーボン膜を形成する。

(もっと読む)

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】従来の領域分割基板と較べて部分領域を引き出し導電領域として利用した場合の抵抗値が小さく、導電性、半導電性または絶縁性の任意の基板材料を用いることができ、適用制限の少ない領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ceに分割され、トレンチ31aによって形成された部分領域Ceの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、導電層35を介して、トレンチ31a内に絶縁体31bが埋め込まれてなる領域分割基板A10とする。

(もっと読む)

半導体装置の製造方法

【課題】銅配線を有する半導体装置において、銅配線の配線抵抗やコンタクトと抵抗を増加することなく信頼性を向上しうる半導体装置の製造方法を提供する。

【解決手段】絶縁膜に形成された開口部内に、銅に対して拡散防止作用を有する第1金属材料を含む第1の膜と、酸素を含有する銅膜を含む第2の膜と、銅と、酸素と結合することにより銅に対して拡散防止作用を有する第2金属材料とを含む第3の膜と、銅を主材料とする第4の膜とを含む配線層を形成した後、熱処理により、絶縁膜と第4の膜との間に、第1金属材料、第2金属材料及び酸素を含むバリア層を形成する。

(もっと読む)

半導体ダイのコンタクト構造および方法

【課題】他の物体によって損傷、剥離、または亀裂を生じることなく、より粗野な処理、運送、および使用を可能にするよりよい緩衝を、半導体デバイスの金属化層に配置された低k誘電体層、ELK誘電体層、および/またはULK誘電体層の半導体ダイのコンタクトを形成するシステム、方法を提供する。

【解決手段】複数の誘電体層および導電層を含む基板101、複数の導電層の最上層115の1つと電気的に接続し、約15,000Åより大きい厚さを有する金属コンタクト105、および金属コンタクトと電気的に接続したコネクタを含む半導体デバイス。

(もっと読む)

成膜方法及びプラズマ処理装置

【課題】シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させることが可能な成膜方法である。

【解決手段】真空排気が可能になされた処理容器22内で被処理体Wの表面に対して薄膜を形成する成膜方法において、原料ガスを用いて処理容器内でプラズマCVD法により薄膜としてチタンを含む金属膜8を形成する金属膜形成工程と、処理容器内で金属膜に対してアニール処理を行うアニール工程とを有する。これにより、シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させる。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

半導体装置およびその製造方法

【課題】グラフェンのバリスティック伝導性を利用した低抵抗配線を備え、配線と配線接続部材の接続部分の構成の複雑化を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、基板と、基板の上方に設けられ、積層された複数のグラフェンナノリボンシート122からなるグラフェンナノリボン層121を含む下層配線12と、複数のグラフェンナノリボンシート122の少なくとも1枚を貫通し、下層配線12と上層配線13とを接続するビア14およびバリアメタル15と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】高密度のカーボンナノチューブを容易に配線に用いることができる半導体装置の製造方法を提供する。

【解決手段】絶縁膜7にビアホール9を形成し、ビアホール9内及び絶縁膜7上に触媒部12を形成する。絶縁膜7上の触媒部12を不活化し、ビアホール9内の触媒部12を起点としてビアホール9内にカーボンナノチューブを成長させる。

(もっと読む)

41 - 60 / 289

[ Back to top ]