Fターム[5F033PP17]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | PVD(物理的気相成長法) (5,261) | スパッタ (4,083) | バイアススパッタ (67)

Fターム[5F033PP17]に分類される特許

41 - 60 / 67

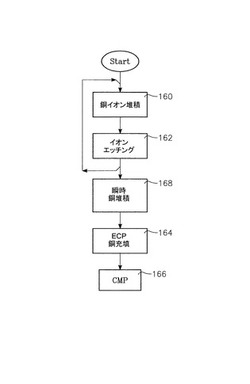

再スパッタされる銅シード層

【課題】段差被覆性に優れた銅シード層の製造方法を提供する。

【解決手段】同じスパッタチャンバ内で実行される堆積された銅のスパッタエッチング162が、銅のスパッタ堆積160の後に続いて実行される。これにより、特に銅の電気めっきの前に、狭いビア内に銅シード層を形成するのに有用な銅堆積プロセスとなる。該堆積は、高い銅イオン化割合及び銅イオンを該ビア内に引き付ける強力なウェーハバイアスを促進する条件下で実行される。該エッチングは、好ましくは、該チャンバの周りのRFコイルによって誘導励起されたアルゴンイオンによって、又は、高いターゲット電力及び極めて強いマグネトロンで形成することができる銅イオンによって、あるいは、RFコイルの使用によって行うことができる。堆積/エッチングの2つ以上のサイクルを実行することができる。最後の瞬時堆積168は、高い銅イオン化及び低いウェーハバイアスで実行することができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体装置の生産性を向上させる。

【解決手段】半導体装置の製造方法において、下層配線上に形成した層間絶縁膜内に、ビアホール及び配線溝を形成し、形成されたビアホール及び配線溝の内壁に、拡散防止膜を形成し、ビアホールの底部に堆積した拡散防止膜をエッチングしながら、下層配線上及び拡散防止膜上にシード層を形成し、形成されたシード層を介してビアホール内及び配線溝内に金属配線を埋設した。このような半導体装置の製造方法によれば、バリア性が高くかつ密着性の良好な拡散防止膜及びバリア層を備えた半導体装置が製造できるので、半導体装置の生産性が向上する。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】Al膜の埋め込み性を向上させた半導体装置の製造方法、及び半導体装置の製造装置を提供するものである。

【解決手段】制御部は、ビアホールVHを有したシリコン基板Sの表面に金属膜BM1(Ti膜)と金属窒化膜BM2(TiN膜)を被覆させ、金属窒化膜BM2に被覆されたビアホールVHの内部にCVD法を用いてAl−CVD膜P1を形成させた。そして、制御部は、Al−CVD膜P1を埋め込む前に、ビアホールVHの底部に位置する金属窒化膜BM2の一部をスパッタし、ビアホールVHの底部の側壁に再付着窒化膜BMrを形成させた。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線材とバリアメタル層の密着性を向上させる。

【解決手段】第1の基板温度で、表面に凹部が形成された層間絶縁膜中及びその表面の酸

化種を放出させ、その後、前記第1の基板温度より低い第2の基板温度で、前記層間絶縁

膜の少なくとも一部と接触するようにして、Ti及びNを含み、酸素(O)及び貴金属成分を除く全成分におけるTi含有量が50at%を超える層を形成する。次いで、前記層上にCu金属層を形成して半導体装置を製造する。

(もっと読む)

成膜方法、成膜装置及び記憶媒体

【課題】バリヤ層や補助シード膜等の成膜プロセス条件を適切に選択して凹部の底部を削り取り、削り込み窪み部の底部の電気抵抗上昇の原因となる層を取り除きつつ側面や上面に薄膜を形成することが可能な成膜方法を提供する。

【解決手段】処理容器34内で金属ターゲット78をイオン化させて金属イオンを含む金属粒子を発生させ、載置台44上に載置した被処理体Wにバイアス電力により引き込んで表面に凹部5が形成されている被処理体の表面に薄膜を形成する成膜方法において、凹部の最下層の底部を削って削り込み窪み部12を形成しつつ凹部内の表面を含む被処理体の表面全体に第1の金属を含む薄膜よりなるバリヤ層10を形成するバリヤ層形成工程と、削り込み窪み部の底部を更に削って凹部内の表面を含む被処理体の表面に第2の金属を含む薄膜よりなるメッキ用の補助シード膜14Aを形成する補助シード膜形成工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】接続孔の開口部および配線溝上部におけるファセットの発生、肩落ちの発生を抑制して、配線信頼性の向上を可能とする。

【解決手段】基板上にストッパ膜15と絶縁膜16とを形成し、絶縁膜16に配線溝17とその底部に接続孔18とを形成し、接続孔18底部を除く配線溝17と接続孔18との内面に第1バリア膜21を形成し、さらに接続孔18底部のストッパ膜15を除去して接続孔18を延長した後、少なくとも接続孔18底部に第2バリア膜22を形成し、この第2バリア膜22と第1バリア膜21とを介して配線材料23を埋め込むことを特徴とする。

(もっと読む)

成膜方法、プラズマ成膜装置及び記憶媒体

【課題】オーバハング部分を生ぜしめることなく凹部の内壁面に十分な厚さのシード膜やバリヤ層等の薄膜を形成することができる成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器24内でプラズマにより金属ターゲット70をイオン化させて金属イオンを発生させ、前記金属イオンを前記処理容器内の載置台34上に載置した表面に凹部2,4を有する被処理体へバイアス電力により引き込んで前記凹部内を含む前記被処理体の表面に薄膜を形成するようにした成膜方法において、前記バイアス電力を、前記被処理体の表面が実質的にスパッタされない領域下にて変化させるようにする。これにより、オーバハング部分を生ぜしめることなく凹部の内壁面に十分な厚さのシード膜やバリヤ層等の薄膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】CuとAlが反応することによる配線抵抗の上昇や、Cuの隆起によるCu配線の信頼性の低下を抑制できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板11上に形成される絶縁膜12と、この絶縁膜の表面に形成された溝内に、第1のバリアメタル層を介在して埋め込まれるCu配線M1A,M1Bと、上記絶縁膜、第1のバリアメタル層及びCu配線上に形成され、上記Cu配線上に対応する位置に開口17A,17Bを有する層間絶縁膜16と、上記層間絶縁膜の開口内において上記Cu配線と電気的に接続されるAl配線20と、少なくとも上記Cu配線とAl配線との間に介在され、CuとAlとの反応を防止するための第2のバリアメタル層18と、上記第2のバリアメタル層に対するAlの流動性を上げるための第3のバリアメタル層19とを含む積層膜とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】キャパシタを有する半導体装置において、漏洩電流の発生を抑制しつつ、形状を均一化し、ショートを発生しにくくする。

【解決手段】円筒状の溝14内のキャパシタ30は、TiNからなる下部電極31と、HfO2からなる容量絶縁膜32と、PVD(physical vapor deposition)法により形成されたTiNからなるPVD−TiN膜33およびCVD法により形成されたTiN膜34からなる上部電極35とを備えている。

(もっと読む)

成膜方法、プラズマ成膜装置及び記憶媒体

【課題】メッキ処理を用いることなくプラズマスパッタだけで微細な凹部を金属によりボイドを発生させることなく埋め込むことができる成膜方法を提供する。

【解決手段】処理容器24内でプラズマにより金属ターゲット70をイオン化させて金属イオンを含む金属粒子を載置台34上に載置した被処理体Wにバイアス電力により引き込んで凹部4を埋め込むようにした成膜方法において、バイアス電力を、被処理体の金属ターゲットに対する対向面に関して、金属粒子による成膜レートとプラズマガスによるスパッタエッチングのエッチングレートとが略均衡するような状態になるように設定して凹部内に金属膜を形成する成膜工程と、金属粒子の供給を停止した状態で被処理体を金属膜の表面拡散が生ずる所定の温度範囲に加熱維持することにより金属膜の原子を凹部の底部に向けて移動させる拡散工程とを交互に複数回繰り返す。

(もっと読む)

絶縁膜の形成方法

【課題】ベースフィルムの剥離工程において、絶縁層の一部が配線層から剥離してしまうことを防ぎ、絶縁層でのリーク電流を無視できる程小さくする半導体装置の層間絶縁膜の形成方法を提供する。

【解決手段】半導体基板10上に、フォトリソグラフィで所望のレジストパターンを形成する工程、レジストパターンに基づいて、配線層となる所定の金属膜15を形成する工程、レジストパターンを保持したまま上記金属膜15上に密着層19aを形成する工程、該密着層19aに所定の熱処理を行う工程のあと、ベースフィルムに塗布形成された未架橋の高分子材料からなる絶縁層19bを加熱して押圧し、上記基板10上に層間絶縁膜19bを形成する。

(もっと読む)

成膜装置および半導体装置の製造方法

【課題】 成膜時の温度上昇を抑制しつつ、多元系膜の組成制御を精度よく行えるようにする。

【解決手段】 チャンバ1内の真空引きを行いながら、ヒータ6にて蒸着源7を加熱し、半導体ウェハWの成膜処理を蒸着にて行うとともに、スパッタガスG1および反応ガスG2をチャンバ1内にそれぞれ供給し、ターゲット2に高周波電圧を印加することにより、チャンバ1内にプラズマPZを発生させ、半導体ウェハWの成膜処理を蒸着にて行いながら、半導体ウェハWの成膜処理をスパッタにて行うことにより、半導体ウェハW上に多元系膜を成膜する。

(もっと読む)

成膜装置および半導体装置の製造方法

【課題】 成膜時の温度上昇を抑制しつつ、多元系膜の組成制御を精度よく行えるようにする。

【解決手段】 ターゲット2、静電チャック4および坩堝5を移動させることにより、ターゲット2、半導体ウェハWおよび蒸着源7の位置関係を調整した後、チャンバ1内の真空引きを行いながら、ヒータ6にて蒸着源7を加熱し、半導体ウェハWの成膜処理を蒸着にて行うとともに、スパッタガスG1および反応ガスG2をチャンバ1内にそれぞれ供給し、ターゲット2に高周波電圧を印加することにより、チャンバ1内にプラズマPZを発生させ、半導体ウェハWの成膜処理を蒸着にて行いながら、半導体ウェハWの成膜処理をスパッタにて行うことにより、半導体ウェハW上に多元系膜を成膜する。

(もっと読む)

金属膜の成膜方法、成膜装置及び記憶媒体

【課題】 凹部の最下層の底部のみを選択的に削り取りつつ凹部内の表面を含む被処理体の表面全域に金属膜を形成することができ、しかも凹部の幅に依存することなく同じ深さだけ底部を削り取って同じ深さの削り込み凹部を形成することができる金属膜の成膜方法を提供する。

【解決手段】 不活性ガスをプラズマ化することにより形成されたプラズマにより真空引き可能になされた処理容器34内で金属ターゲット78をイオン化させて金属イオンを含む金属粒子を発生させ、金属粒子を処理容器内の載置台44上に載置した被処理体Wにバイアス電力により引き込んで表面に凹部5が形成されている被処理体の表面に金属膜10bを形成する成膜方法において、凹部の最下層の底部を削って削り込み凹部12を形成しつつ凹部内の表面を含む被処理体の表面の全体に前記金属膜を形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】配線と配線を接続する接続部のバリア膜の構造を最適化し、エレクトロマイグレーション特性を向上させる。

【解決手段】半導体基板上の第1層配線M1上に形成された層間絶縁膜TH2中に配線溝HM2およびコンタクトホールC2を形成した後、これらの内部にバリア膜PM2aを、コンタクトホールC2の底部の全周に渡ってコンタクトホールC2の底部の中央部から側壁に向かってその膜厚が増加するよう形成し、このバリア膜PM2a上に銅膜(PM2b、PM2c)を形成した後、CMP法により研磨することにより第2層配線M2と接続部(プラグ)P2を形成する。その結果、接続部(プラグ)P2を介して第2層配線M2から第1層配線M1へ流れる電流の幾何学的な最短経路と、電気的に抵抗が最小となるバリア膜PM2aの薄い部分が一致せず、電流経路を分散することができ、電子の集中を起こりにくくできる。

(もっと読む)

半導体装置の製造方法

【課題】 水素によるキャパシタ誘電体膜の劣化を防止することが可能な半導体装置の製造方法を提供すること。

【解決手段】 シリコン(半導体)基板1の上に下地絶縁膜10を形成する工程と、下地絶縁膜10の上に、下部電極11a、キャパシタ誘電体膜12a、及び上部電極13aを順に形成してなるキャパシタQを形成する工程と、キャパシタQを覆う第1層間絶縁膜15を形成する工程と、第1層間絶縁膜15の上に、シリコン基板1にバイアス電圧を印加しないプラズマCVD法により第1保護絶縁膜16を形成する工程と、を有することを特徴とする半導体装置の製造方法による。

(もっと読む)

半導体装置構造および半導体装置の製造方法

【課題】 塗布絶縁膜からの脱ガス反応を押さえ、塗布絶縁膜の変形やクラック等を回避して半導体装置としての信頼性向上をはかる。

【解決手段】 ヒューズ素子の側壁部もしくはそれを覆う絶縁談をテーパ形状に加工することにより、ヒューズ素子の近隣に存在する塗布絶縁膜との距離を大きくすることで塗布絶縁膜へ加わる熱ストレスを緩和し、塗布絶縁談からの脱ガス反応を押さえ塗布絶縁談の変形やクラック等を避ける。また、ヒューズ素子の側壁部もしくはそれを覆う絶縁膜にサイドスペーサを形成し、あるいはヒューズ素子の側壁部とさらにそれを覆う絶縁談にもサイドスペーサを形成することにより、一層、ヒューズ素子の近隣に存在する塗布絶縁膜との距離を大きくする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】絶縁膜に形成された配線溝または接続孔の内部に埋込配線形成用の導体膜を良好に埋め込む。

【解決手段】半導体基板1上の絶縁膜5cに形成された配線溝10b内に埋込配線11bを形成する際、埋込配線11bを構成する導体膜8bを、指向性を有し、かつ、スパッタリング粒子が散乱され難い条件を付加したスパッタリング法で被着した後、埋込配線11bを構成する導体膜8cをメッキ法で被着する。この導体膜8bは、プラチナ、パラジウム、ニッケル、クロム、金または銀の少なくとも1つが添加されている銅を含む導体材料からなる。導体膜8bの被着膜厚が導体膜8cの被着膜厚と等しいか、または導体膜8cの被着膜厚よりも厚い。

(もっと読む)

成膜装置

【課題】 同一チャンバ内で基板ステージ上の処理基板に対し、ALD法による成膜とスパッタリング法による成膜とを行い得るように成膜装置を構成する場合に、ターゲットが、ALD法を行う際に導入する原料ガスや反応ガスによって汚染されないようにする。

【解決手段】 真空チャンバ11内に基板ステージ12を配置し、ターゲットを有するスパッタリング成膜手段4を、ターゲット41aと処理基板とを相互に対向させて設ける。真空チャンバをターゲットが存する第1空間51と基板ステージが存する第2空間52とに仕切る仕切り板5を設け、仕切り板に処理基板が臨む開口部5aを形成し、開口部を覆って第1空間及び第2空間相互の隔絶を可能とする閉位置と、開口部を開放する開位置との間で移動自在な遮蔽手段6を配置する。化学的成膜法により成膜を行い得る化学的成膜手段を第2空間に設ける。

(もっと読む)

製品

【課題】多重チャネルにて曲がり半導体線と交差するゲート信号線の提供。

【解決手段】第一および第二結合点184・186に延びる第一の線180を具備でき、第一および第二結合点184・186にて、第一の線180は他の素子192と電気的に結合する。第一の線180は、半導体材料を含む回路の層にある。別の層にある第二の線182は、ゲート信号を受信するように結合できる。第二の線182は、複数個のチャネル域にて第一の線180と交差し、交差域の各々において、第一の線180はチャネルを具備している。チャネルは、第一および第二結合点184・186の間で直列である。第二の線182は導電性があり、ゲート信号を全部のチャネル域に伝える。第一の線180は、第一および第二結合点184・186のあいだの第一の線180の導電性が、第二の線182によってチャネル域に伝えられるゲート信号によって制御されるように位置決めされる。

(もっと読む)

41 - 60 / 67

[ Back to top ]