Fターム[5F033RR09]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 無機SOG膜(無機物質又は不明な場合) (711)

Fターム[5F033RR09]に分類される特許

701 - 711 / 711

調整可能な反射防止コーティングを含む構造およびその形成方法。

【課題】 調整可能な反射防止コーティングを含む構造およびその形成方法を提供することである。

【解決手段】 調整可能なエッチング耐性反射防止(TERA)コーティングを含む配線工程(BEOL)アプリケーションにおける配線構造が記載される。TERAコーティングは、例えば、シングルダマシン構造またはデュアルダマシン構造の中で取り入れられることができる。TERAコーティングは、配線構造を形成するリソグラフィマスクの一部として役に立つことができ、または、それは、ハードマスクとして、ケミカルメカニカルポリシング(CMP)のストップ層として、またはCMP中の犠牲層として役立つことになる。

(もっと読む)

レーザ除去タングステン・ヒューズ用配線保護要素(電気的構造体および形成方法)

【課題】集束放射線(52)によるヒューズ・リンク除去中に電気的構造体(25)を保護するための構造および対応する形成方法を提供すること。

【解決手段】構造体(1)は、ヒューズ要素(2)と、保護プレート(10)と、第1誘電体層(14)と、第2誘電体層(4)とを含む。構造体(1)は、半導体デバイス(5)内に形成される。保護プレート(10)は、ダマシン・プロセスを使用して第1誘電体層(14)内に形成される。第2誘電体層(4)は、保護プレート(10)および第1誘電体層(14)上に形成される。ヒューズ要素(2)は、第2誘電体層(4)上に形成される。ヒューズ要素(2)は、レーザビーム(52)で切断されるように構成される。第2誘電体層(4)の誘電率は、第1誘電体層(14)の誘電率より大きい。保護プレート(10)は、第1誘電体層(14)をレーザビーム(52)のエネルギーから遮蔽するように構成される。

(もっと読む)

誘電体膜を処理するための方法とシステム

【課題】誘電体膜を処理するための方法とシステムを提供する。

【解決手段】誘電体膜を処理するための方法とシステムは、誘電体膜の少なくとも一つの表面をCxHy含有材料に露出することを有する。xとyはそれぞれ1以上の整数である。エッチプロセスすなわちアッシングの結果、誘電体膜に形成された形態の露出表面は、ダメージを受けるか活性化するかして、汚染物質の保留・湿気の吸収・誘電率の上昇などを引き起こし得る。ダメージを受けた表面は、少なくとも、表面を修復して例えば誘電率を復活させる(すなわち誘電率を減少させる)か、表面を洗浄して汚染物質や湿気や残渣を取り去るかして処理する。さらに、膜中の形態のバリア層とメタリゼーションのための準備は、形態の側壁表面を被覆して、露出した空孔を閉じ、またバリア膜堆積用の表面を提供する処理を含んでもよい。

(もっと読む)

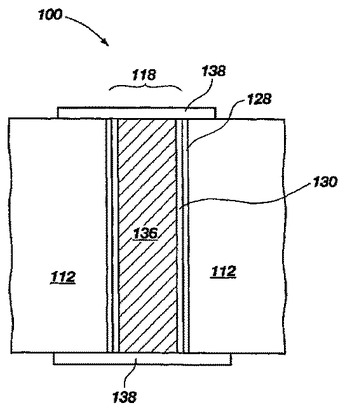

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

集積回路デバイス内の相互接続構造体

【課題】 フォトレジスト汚染の問題に悩まされないデュアル・ダマシン構造体を形成する方法を提供すること。

【解決手段】 本発明は、集積回路デバイス内のデュアル・ダマシン相互接続構造体の製造に関する。具体的には、平坦化材料及び拡散障壁材料を用いて、低kの誘電体薄膜内にシングル又はデュアル・ダマシン構造体を形成するための方法が開示される。この方法の好ましいデュアル・ダマシンの実施形態において、最初に誘電体材料にビアを形成し、次にビア内及び誘電体材料上に平坦化材料を付着させ、平坦化材料上に障壁材料を付着させる。次に、リソグラフィにより像形成材料にトレンチが形成され、障壁材料を通して平坦化材料がエッチングされ、トレンチ・パターンが誘電体材料に転写される。これらのエッチング・ステップの過程の間及び該エッチング・ステップの過程に続いて、像形成材料、障壁材料及び平坦化材料が除去される。次に、結果として得られるデュアル・ダマシン構造を金属化することができる。この方法を用いる場合、層間誘電体材料によるフォトレジスト汚染の問題が軽減される。

(もっと読む)

ライン及びビア導体のための異なる材料を有するデュアル・ダマシン相互接続構造体

【課題】 ライン導体のために用いられるものと異なる、ビア又はスタッドのための材料を用いて、デュアル・ダマシン相互接続構造体を形成する方法を提供すること。

【解決手段】 ライン導体に用いられるものとは異なる、ビア又はスタッドのための材料を用いるか、又はトレンチ・ライナに用いられるものとは異なる、ビア・ライナのための材料を用いるか、或いは該トレンチ・ライナのものと異なるビア・ライナ厚を有する、デュアル・ダマシンのバックエンド・オブ・ライン(back−end−of−line:BEOL)相互接続構造体を形成する方法が開示される。改善された機械的強度のために、ビアに厚い超硬合金を用いる一方で、トレンチに薄い超硬合金だけを用い、抵抗を低くすることが好ましい。

(もっと読む)

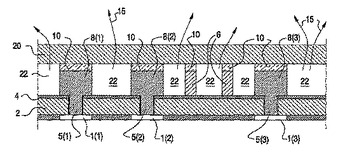

多孔質の誘電体層とエアギャップとを有する基板の製造方法、および基板

金属ライン(8(i))の間および誘電体内にエアギャップを形成する方法である。方法は、デュアルダマシン(dual damascene)構造を得ること、拡散バリア層(10)を、平坦化された面に直接加えること、およびリソグラフィステップを行なうことからなり、これにより、金属ラインを、拡散バリア層の下に遮蔽する。任意として、金属ライン(8(i))間の大きな誘電体領域(6)のいくつかの部分も、遮蔽される。露出した拡散バリア層部分および下にある誘電体がエッチングされる。典型的には150〜450℃の温度に加熱することにより、揮発性成分に分解することができる材料の層が加えられ、エッチングまたはCMPにより平坦化される。分解性生成物に対して透過性である誘電体層(20)が堆積され、その後、基板は加熱される。次いで、使い捨て層が分解し、透過性の誘電体層を通じて消滅し、その後に、金属ライン(8(i))および大きな誘電体領域の間に、エアギャップ(22)を残す。  (もっと読む)

(もっと読む)

多層配線構造の形成方法

【課題】SOG膜のSi原子と有機基(例えばCH3基)やH基の結合がアッシング時に切れるのを抑制して誘電率を低く抑える。

【解決手段】低誘電率の有機又は無機SOG膜にパターン化レジスト膜をマスクとしてエッチングを行って配線溝を形成し、この後、枚葉式ダウンストリーム型のプラズマアッシング装置を用いて、酸素ガスプラズマによるアッシング処理を例えば1.2Torrの圧力雰囲気下で施してレジスト膜を除去し、この後配線溝にバリヤメタル形成後、Cuを電界メッキ法にて埋設して配線を形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】 アルミニウムを主成分とする導体膜パターンを有する半導体集積回路装置の信頼性を向上させる。

【解決手段】 アルミニウムを主成分とする導体膜16dを有する第1層配線L1をドライエッチング法によってパターニングした後、その加工側壁の側壁保護膜18およびエッチングマスクとして使用したフォトレジストパターン17aをプラズマアッシング処理によって除去する。続いて、絶縁膜15bおよび第1層配線L1の表面に付着した塩素成分を、酸素ガスとメタノールガスとの混合ガスを用いたプラズマアッシング処理によって除去する。この際、フォトレジストパターン17a等のアッシング除去処理時は、ウエハの主面温度が相対的に低くなるようにし、塩素成分の除去処理時は、ウエハの主面温度が相対的に高くなるようにする。また、それらのプラズマアッシング処理を別々の処理室で行う。

(もっと読む)

配線構造

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造を提供する。

【解決手段】 半導体素子が形成された基板上に絶縁膜103が多層形成され、絶縁膜103に形成された配線溝およびビアホールに金属配線剤が充填されて、配線および接続プラグが形成された配線構造において、絶縁膜103のうち少なくとも一層が対電子線感光性を有する材料から形成されており、絶縁膜103の層間にはバリア絶縁膜104を有し、前記金属配線剤は銅を含むものである。

(もっと読む)

多層スピンオン多孔性誘電体からなるlow−k配線構造

【課題】その中にマイクロトレンチを含まない低誘電体層間絶縁膜金属導体配線構造およびそのような構造の形成方法を提供する。

【解決手段】導体抵抗に対する制御は、第1の原子組成を有する多孔性の低誘電体層間絶縁膜の線とバイア誘電体層との間に位置する第2の原子組成を有する埋込みエッチング停止層により行われる。本発明の配線構造は、また、二重波形模様タイプの配線構造を形成する際に助けになるハードマスクを含む。第1および第2の組成は、エッチング選択性が少なくとも10:1またはそれ以上になるように選択され、特定の原子組成および他の発見できる量を有する多孔性の低誘電体層間絶縁膜有機材料または無機材料の特定のグルーブから選択される。

(もっと読む)

701 - 711 / 711

[ Back to top ]