Fターム[5F038AC19]の内容

Fターム[5F038AC19]に分類される特許

1 - 20 / 86

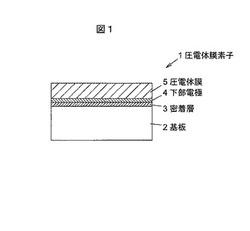

圧電体膜素子の製造方法、圧電体膜素子及び圧電体デバイス

【課題】ドライエッチングにより微細加工を行った場合に、エッチング残渣が少なく、後工程における信頼性が高い非鉛の圧電体膜素子の製造方法、圧電体膜素子及び圧電体デバイスを提供する。

【解決手段】圧電体膜素子1の製造方法は、基板2上に、組成式(K1−xNax)NbO3で表されるペロブスカイト構造を有する非鉛のアルカリニオブ酸化物系化合物からなる圧電体膜5を形成する工程と、圧電体膜5を、フッ素系反応ガスを含む雰囲気中で低圧プラズマを用いてエッチングを行う工程とを含む。

(もっと読む)

半導体集積回路装置

【課題】高周波回路に於いては、トランジスタ等の能動素子間および能動素子と外部端子の間を直流的に遮断する必要がありため、MIMキャパシタ等が多用される。これらのMIMキャパシタのうち、外部端子に接続されたものは、外部からの静電気の影響を受けやすく、静電破壊等の問題を発生しやすい。

【解決手段】本願発明は、半絶縁性化合物半導体基板上に形成された半導体集積回路装置であって、外部パッドに電気的に接続されたMIMキャパシタの第1の電極は前記半絶縁性化合物半導体基板に電気的に接続されており、一方、前記MIMキャパシタの第2の電極は前記半絶縁性化合物半導体基板に電気的に接続されている。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置

【課題】コイル状のアンテナ部の内部に、占有面積が大きい導電層が設けられていると、電源を安定して供給することが困難になっていた。

【解決手段】記憶回路部とコイル状のアンテナ部とを積層して配置することにより、記憶回路部が含む占有面積の大きい導電層に電流が流れてしまうことを防止することができ、省電力化を図ることができる。また、記憶回路部とコイル状のアンテナ部とを積層して配置することにより、スペースを有効に利用することができる。従って、半導体装置の小型化を実現することができる。

(もっと読む)

静電容量素子

【課題】 生産性に優れる温度補償型の静電容量素子を提供する。

【解決手段】 静電容量素子10は、基板20と、該基板20の上に位置する第1コンデンサ30と、基板20の上に位置し且つ第1コンデンサ30と電気的に並列接続されている第2コンデンサ40とを有する。第1コンデンサ30は、第1下部電極31と、第1誘電体32と、第1上部電極33とで構成される。第2コンデンサ40は、第1下部電極31と組成の異なる第2下部電極41と、第1誘電体32と同組成である第2誘電体42と、第2上部電極43とで構成される。第1コンデンサ30の温度が上昇する際に変化する静電容量と、第2コンデンサ40の温度が上昇する際に変化する静電容量とで正負が異なっている。

(もっと読む)

高誘電性ナノシート積層体、高誘電性ナノシート積層体、高誘電体素子、および高誘電体薄膜素子の製造方法

【課題】コンデンサなどに好適な、非常に薄くしても高い誘電率と良好な絶縁特性を同時に実現する高誘電体薄膜を提供する。

【解決手段】上記課題は、ペロブスカイト構造を有する酸化物ナノシートなどの高誘電体により構成される薄膜により達成される。

(もっと読む)

無線通信デバイス、受動素子の製造方法、及び無線通信機器

【課題】高周波回路のワンチップ化を実現し、上層回路と下層回路との間におけるアイソレーション特性を向上し、かつ量産性の高い無線通信デバイスを提供する。

【解決手段】RFICと、キャパシタ32と、インダクタ24とが積層配置され、キャパシタ32の少なくとも一部がRFICとインダクタ24との間に位置するようにして前記RFICに対して積層して実装される受動素子チップ12と、を備えることを特徴とする。このような特徴を有する無線通信デバイスでは、受動素子チップ12は、キャパシタ32の上部電極26を構成する金属パターンとインダクタ24を構成する金属パターンとを横並びに備え、キャパシタ32の下部電極を構成する下層金属パターン18をインダクタ24を構成する金属パターンの下部にまで延設して構成すると良い。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供すること。

【解決手段】トランジスタと、容量素子と、を有し、トランジスタは、第1の酸化物半導体層と、第1の酸化物半導体層と接するソース電極およびドレイン電極と、第1の酸化物半導体層と重なるゲート電極と、第1の酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、容量素子は、ソース電極またはドレイン電極と、ソース電極またはドレイン電極と接する第2の酸化物半導体層と、第2の酸化物半導体層と接する容量素子電極と、を有する半導体装置である。

(もっと読む)

可変容量素子、及び液晶表示装置

【課題】制御性が良く、安定して動作する可変容量素子を提供する。消費電力が少なく、表示品位の良い液晶表示装置を提供する。

【解決手段】印加される電界により、n型またはi型となる半導体、もしくは、p型またはi型となる半導体を用いて可変容量素子を構成する。容量素子を構成する第1の電極と第2の電極の間に、誘電体層として絶縁層と上記半導体層の積層を設ける。第1の電極を誘電体層側に設け、第2の電極を半導体層側に設けた時に、第1の電極と半導体層が重畳する面積C1よりも、第1の電極と半導体層と第2の電極が重畳する面積C2の方を小さくなるようにする。動画像表示と静止画像表示で駆動方法を切り替える液晶表示装置に可変容量素子を適用することで、消費電力が少なく、表示品位の良い液晶表示装置を実現できる。

(もっと読む)

半導体装置の作製方法

【課題】必要十分なキャパシティをもつ保持容量を備えた半導体装置を提供する。

【解決手段】金属表面を有する基板11と、前記金属表面を有する基板上に形成された絶縁膜12と、前記絶縁膜上に形成された画素部とを有する半導体装置において、前記画素部は、TFTと、該TFTと接続する配線21とを有しており、保持容量は、前記金属表面を有する基板、前記絶縁膜および前記配線により構成されている。前記絶縁膜の膜厚が薄いほど、また、前記絶縁膜と前記配線の接する領域の面積が大きいほど、大きなキャパシティを得られるので有利である。

(もっと読む)

容量素子の製造方法

【課題】基板上に耐圧が異なる容量素子を共通の工程で形成する際に、基板上に残渣を残さないようにする。

【解決手段】基板10の上に半導体不純物がドープされた第1ポリシリコン層40を形成し、第1ポリシリコン層40の上にCVD法により第1酸化膜41を層状に堆積する(図2(a))。これにより、1回目の酸化で第1酸化膜41を第1ポリシリコン層40の粒界部に入り込ませないようにする。そして、第1酸化膜41を第1ボトム膜24にパターニングした後(図2(b))、第1ポリシリコン層40の上に第2酸化膜42を形成する(図2(c))。2回目の酸化は短時間で終わるので、第1ポリシリコン層40の増速酸化が進行する前に第2酸化膜42の形成が完了する。このため、第1ポリシリコン層40をエッチングする際に第2酸化膜42の一部がマスクとならないようにすることができる。

(もっと読む)

表示装置及びその製造方法

【課題】絶縁層による光透過率の低下を防止することができる表示装置及びその製造方法を提供する。

【解決手段】表示装置は、第1基板110上に位置する第1絶縁層116と、第1絶縁層116上に位置する下部電極118bと、下部電極118bの上面及び側面を囲むように形成された誘電体層120aと、誘電体層120a上に位置する上部電極122aと、を備える。第1絶縁層116は、誘電体層120aに対してエッチング選択比を有してもよい。第1絶縁層116は、シリコン酸化物を含み、誘電体層120aは、シリコン窒化物を含んでもよい。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】高性能なフレキシブル半導体装置を提供すること。

【解決手段】可撓性を有するフレキシブル半導体装置であって、絶縁膜と、かかる絶縁膜の下面に位置する金属箔をエッチングすることによって形成されたソース電極およびドレイン電極と、絶縁膜の上面の一部に形成された半導体層と、ソース電極およびドレイン電極のそれぞれと、前記半導体層とを電気的に接続する取出し電極パターンと、取出し電極パターンおよび半導体層を封止する封止樹脂層と、封止樹脂層の面のうちソース電極およびドレイン電極が形成された面とは反対側の面に形成されたゲート電極とを備えたフレキシブル半導体装置。

(もっと読む)

レドックスキャパシタ及びその作製方法

【課題】室温で使用可能なレドックスキャパシタ及びその作製方法を提供する。

【解決手段】レドックスキャパシタの電解質として、水素を含む非晶質半導体を用いる。水素を含む非晶質半導体の代表例としては、非晶質シリコン、非晶質シリコンゲルマニウム、または非晶質ゲルマニウム等の半導体元素を有する非晶質半導体がある。また、水素を含む非晶質半導体の他の例としては、水素を含む酸化物半導体があり、代表例としては、酸化亜鉛、酸化チタン、酸化ニッケル、酸化バナジウム、または酸化インジウム等の一元系酸化物半導体を有する非晶質半導体がある。または、水素を含む酸化物半導体の他の例としては多元系酸化物半導体があり、代表的にはInMO3(ZnO)m(m>0、MはGa、Fe、Ni、Mn及びCoから選ばれた一の金属元素または複数の金属元素)がある。

(もっと読む)

電気化学キャパシタ

【課題】容量を高めることが可能な電気化学キャパシタを提案する。

【解決手段】基板の一平面上に正極と負極が形成される電気化学キャパシタである。また、電解質と、電解質の同一平面に接する正極及び負極とを有する。即ち、電解質の一平面上に接する正極活物質及び負極活物質と、正極活物質に接する正極集電体と、負極活物質に接する負極集電体とを有する電気化学キャパシタである。当該構成により、電気化学キャパシタの容量を増大させることができる。

(もっと読む)

薄膜集積回路装置及びその製造方法

【課題】商品の意匠性を低下させないICタグ等を形成することができる薄膜集積回路装置を提供する。

【解決手段】透明基板1上に少なくともTFT素子Aと容量素子B及び/又は抵抗素子Cとを有し、TFT素子Aを構成するゲート電極2A、ゲート絶縁膜3A、半導体膜4、ソース電極6S及びドレイン電極6Dがいずれも透明膜であり、容量素子Cを構成する誘電体膜3Bが前記ゲート絶縁膜3Aと同一材料であり、その誘電体膜3Bを積層方向Zに挟む一方の第1電極2Bが前記ゲート電極2Aと同一材料で、他方の第2電極6Bが前記ソース電極6S及びドレイン電極6Dと同一材料であり、抵抗素子Cを構成する抵抗体膜4Cが前記半導体膜4と同一材料であり、その抵抗体膜4Cを面内方向Xに挟む第3電極6Eと第4電極6Fが前記ソース電極6S及びドレイン電極6Fと同一材料であるようにした薄膜集積回路装置10Aを提供する。

(もっと読む)

薄膜キャパシタ

【課題】バンプ等の外部接続端子に働く鉛直方向の応力が電極層に集中しない構造を有するとともに、等価直列抵抗を所望の値に増加させることが容易な薄膜キャパシタとその製造方法を提供する。

【解決手段】基板と、前記基板上に形成され少なくとも1層の誘電体薄膜と少なくとも2層の電極層からなるキャパシタ部と、前記キャパシタ部の少なくとも一部を覆う保護層と、前記キャパシタ部のいずれかの電極層と電気的に接続する引き出し導体と、前記引き出し導体上に形成されたバンプと、を備え、前記引き出し導体は、前記保護層に形成された開口部内に形成されて前記キャパシタ部のいずれかの電極層と電気的に接続する接続部と、前記保護層上に延伸された引き回し部とからなり、前記バンプは前記引き回し部上に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化によってキャパシタが小型化された場合であっても、キャパシタの実効的なキャパシタ容量の低下を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】下部電極に形成した凹部開口の内周面を含む下部電極上に誘電膜を形成し、凹部開口内を含む誘電膜上に下部電極と対向する上部電極を形成する。さらに、下部電極を、第1導電膜と、絶縁膜と、不純物がドープされた低抵抗の第2導電膜とを順次積層して形成し、第1導電膜と第2導電膜とを接続する。

(もっと読む)

電子素子及びその製造方法、並びに表示装置

【課題】低温プロセスで製造でき、リーク電流が抑制された電子素子を提供する。

【解決手段】基板10上に、端部断面のテーパー角度が60°以下である下部電極22と、前記下部電極22上に配置され、水素原子の含有率が3原子%以下であり、波長650nmにおける屈折率nが1.475以下であるSiO2膜24と、前記SiO2膜24上に配置され、前記下部電極22と重なり部を有する上部電極26と、を有する電子素子である。

(もっと読む)

1 - 20 / 86

[ Back to top ]