Fターム[5F038AV09]の内容

Fターム[5F038AV09]の下位に属するFターム

微調整 (173)

Fターム[5F038AV09]に分類される特許

1 - 20 / 22

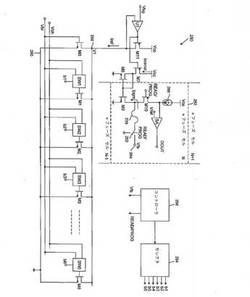

半導体デバイスの電気的にプログラミング可能なヒューズモジュール

【課題】より小型なeヒューズモジュールを提供する。

【解決手段】半導体デバイスが、eヒューズモジュールおよびプログラミング電流生成器を有する。eヒューズモジュールが電気的にプログラミングするeヒューズ素子(226)のアレイを含む。プログラミング電流発生器が、複数の基準トランジスタ素子(M0〜M6)のセットと、基準トランジスタ素子(M0〜M6)を活性化させて、選択された基準電流を生成するセレクタ(254)と、アレイの選択されたeヒューズ素子(226)に、選択された基準電流に応じたプログラミング電流を印加して、eヒューズ素子(226)の抵抗をプログラミングするカレントミラー(M7、M8、M9)とを有する。

(もっと読む)

半導体装置

【課題】アンチフューズにより多数のフューズ設定を切り替えることのできる半導体装置を提供する。

【解決手段】異なる機能または特性を有する機能回路に対応して設けられたn個の機能判定回路41−1〜41−nと、n個のフューズ素子を有し、機能判定回路各々の判定に用いる機能設定情報を格納するフューズ回路31、フューズ回路32と、アンチフューズ素子AF1の導通・非導通状態に応じて、フューズ回路のいずれか1つを選択するアンチフューズ判定回路20と、を備える。

(もっと読む)

集積回路装置

【課題】酸化バナジウムからなるセンサ部材を備えた集積回路装置において、過大な電流によりセンサ部材が破壊されることがなく、信頼性が高い集積回路装置を提供する。

【解決手段】半導体集積回路装置1において、電源電位配線から接地電位配線に向かって、温度モニタ部材R2及びR1を直列に接続すると共に、温度モニタ部材R3及びR4を直列に接続する。温度モニタ部材R1及びR3は酸化バナジウムにより形成し、シート層5に配置する。また、温度モニタ部材R2及びR4はアモルファスシリコンにより形成する。そして、出力端子Vout1及びVout2に接続された差動増幅部を設ける。

(もっと読む)

半導体装置

【課題】動作信頼性を向上させる半導体装置を提供すること。

【解決手段】基板10内に、互いに離隔して形成された第1乃至第3拡散層13と、前記第1拡散層13と前記第2拡散層13との間の前記基板10上に第1絶縁膜14を介在して形成された第1電極15を備え、前記第1拡散層13をソースとし、前記第2拡散層13をドレインとする、第1トランジスタ20と、前記第2拡散層13と前記第3拡散層13との間の前記基板10上に第2絶縁膜14を介在して形成された第2電極15を備え、前記第2拡散層13をドレインとし、前記第3拡散層13をソースとする第2トランジスタ21とを具備し、前記第2トランジスタ21は、前記第2電極15及び前記第3拡散層13に固定電圧が与えられることにより、常時オフ状態とされ、前記第1トランジスタ20の閾値は、前記第2トランジスタ21の閾値よりも小さい。

(もっと読む)

半導体集積回路装置とCMOS回路の高速化方法

【課題】既存のCMOS回路を含んでその高速化が簡単にできる半導体集積回路装置及び高速化方法を提供する。

【解決手段】半導体集積回路装置に設けられた複数の信号伝達経路は、複数の論理ゲート回路がエンハンスメント型MOSFETで構成されて、その信号伝達遅延時間が許容される信号伝達遅延時間以下とされる第1信号伝達経路と、複数の論理ゲート回路のうちエンハンスメント型MOSFETで構成したときに上記許容される信号伝達遅延時間よりも大きな遅延時間を持つものが、ディプレッション型MOSFETに置き換えられることによってその信号伝達遅延時間が上記許容される信号伝達遅延時間以下とされる。複数の論理ゲート回路は、しきい値電圧が互いに異なる5種類のCMOSにより構成される。

【選択図】図5  (もっと読む)

(もっと読む)

半導体装置

【課題】ツェナーザップ等のトリミング用素子を不要とする半導体装置を提供する。

【解決手段】半導体基板1の裏面に形成された絶縁膜2、半導体基板の主面から絶縁膜まで到達するように形成された複数の素子分離領域31〜33、半導体基板において素子分離領域により相互に電気的に分離された少なくも半導体層41、42、半導体層41、42の表面に電気的に接続されるように設けられた電圧印加端子11、12、電圧印加端子11とノードN1との間に直列に接続されたスイッチSW1、電圧印加端子12とノードN2との間に直列に接続されたスイッチSW2、ノードN1、N2からそれぞれの電圧を入力されてこれに応じた出力を行うセレクタ回路SR1、半導体基板の裏面に形成された絶縁膜に接触するように配置された導電層3を備える。

(もっと読む)

アンチヒューズ素子、およびアンチヒューズ素子の設定方法

【課題】2値よりも多い情報を記録可能にしたアンチヒューズ素子を提供する。

【解決手段】複数のMOSトランジスタと、複数のMOSトランジスタのソース電極が共通に接続された第1の電極と、複数のMOSトランジスタのゲート電極が共通に接続された第2の電極と、複数のMOSトランジスタのドレイン電極の少なくとも1つと接続される第3の電極と、ドレイン電極および第3の電極の間に設けられた絶縁膜と、を有する。そして、上記絶縁膜においてドレイン電極に対応して少なくとも1箇所が絶縁破壊されることで、絶縁破壊された部位に対応するドレイン電極と第3の電極とが導通する構成である。

(もっと読む)

アンチヒューズ回路及びこれを備える半導体装置、並びに、アンチヒューズ回路へのアドレス書き込み方法

【課題】アンチヒューズ素子への書き込み処理を高速に行うことが可能なアンチヒューズ回路を提供する。

【解決手段】本発明によるアンチヒューズ回路は、不揮発的にデータを保持するアンチヒューズ素子330と、アンチヒューズ素子330に書き込むべきデータを一時的に保持するラッチ回路320とを備える。ラッチ回路320への書き込みはナノ秒オーダーで実行可能であることから、複数のチップにそれぞれ異なる不良アドレスを書き込む場合であっても、ラッチ回路320への書き込み処理を極めて短時間で完了することができる。これにより、アンチヒューズ素子330への実際の書き込み処理については、複数のチップについて並列に実行することができ、結果的にアンチヒューズ素子330への書き込み処理を高速に行うことが可能となる。

(もっと読む)

フューズ回路および半導体装置

【課題】特殊なレーザー装置を用いずにフューズに対する処理を行うこと。フューズを物理的に破壊せずにフューズに対する処理を行うこと。

【解決手段】信号出力ライン4と電源ライン10の間に第1のPチャネルトランジスタ1が接続され、信号出力ライン4と接地ライン11の間に第2のPチャネルトランジスタ2が接続される。ストレス印加前は、第2のPチャネルトランジスタ2のオフリーク電流が第1のPチャネルトランジスタ1のオフリーク電流よりも大きいので、信号出力ライン4の電位レベルがローとなる。第1のPチャネルトランジスタ1にのみストレスを印加することにより、第1のPチャネルトランジスタ1のリバース方向のオフリーク電流が増加し、第1のPチャネルトランジスタ1のオフリーク電流が第2のPチャネルトランジスタ2のオフリーク電流よりも大きくなるので、信号出力ライン4の電位レベルがハイになる。

(もっと読む)

トリミング回路

【課題】トリミング評価や、半導体メーカからの出荷後等の対応に自由度を持たせ、更に、回路構成の簡単化と回路規模の小型化を図る。

【解決手段】LSI等のトリミング回路において、ヒューズ回路等の制限データ設定手段10と、何度でも可変可能なレジスタ20等の可変データ設定手段との両方を混載し、これらの両手段を、論理回路30等の選択手段により切り替え可能にして、トリミング対象である被トリミング回路40に接続している。

(もっと読む)

半導体装置

【課題】ヒューズ素子は電流溶断の構造上、メモリや論理回路ほど微細化を図ることができず、相対的に面積増の影響が大きくなる。

【解決手段】通常使用状態で使用されるヒューズ素子101と、非通常使用状態で使用されるヒューズ素子111とを1個のヒューズコア120中に設け、いずれか一方のヒューズ素子を切換信号で選択できるようにするとともに、各ヒューズ素子のプログラム(溶断)の開始及び終了を制御するためのフリップフロップ回路124や、各ヒューズ素子にプログラムされた値を読み出すためのリファレンス抵抗105、NMOSトランジスタ106,107、差動アンプ回路108等を両ヒューズ素子で共用する。

(もっと読む)

半導体装置

【課題】冗長ブロックと代替させる通常ブロックを指定することができる半導体装置であって、接続配線数を減らすことができる半導体装置を提供することを課題とする。

【解決手段】複数の通常ブロックと、通常ブロックと代替させるための冗長ブロックと、を有する複数のマクロ(401A〜401D)と、前記複数のマクロのうちの前記代替させるマクロを指定するための第1の代替マクロ情報及び前記代替させる通常ブロックを指定するための第1の代替ブロック情報を記憶する第1の代替情報記憶手段(102,103)と、前記複数のマクロをシリアルに接続する第1の伝達線(SC1)と、前記第1の代替マクロ情報及び前記第1の代替ブロック情報を基に、前記第1の伝達線を介して、前記指定されたマクロ内の前記指定された通常ブロックに代替情報を伝達する代替情報伝達回路とを有することを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置

【課題】多層配線部からAVAI層間絶縁膜に亘る領域にMIM素子およびヒューズを形成し易い構造の半導体装置を得ること。

【解決手段】半導体基板10と、半導体基板に形成された回路素子20,30と、回路素子を覆うようにして半導体基板上に形成された多層配線部50と、多層配線部における最も上の層間絶縁膜45に形成されたヒューズ75と、多層配線部上に形成されたMIM素子70と、多層配線部を覆う最外層間絶縁膜60とを備えた半導体装置100を作製するにあたり、多層配線部における最も上の層間絶縁膜に形成された下部電極62と、下部電極上に形成された電気絶縁膜64と、電気絶縁膜上に形成された上部電極66とによってMIM素子を構成する。

(もっと読む)

半導体装置の過電圧印加監視回路

【課題】半導体装置に過電圧が印加された場合に、その履歴を残すことが可能な半導体装置の過電圧印加監視回路を提供すること。

【解決手段】半導体装置100の入力電圧線11にツェナダイオード13で構成される過電圧検出回路12を接続する。その過電圧検出回路12と直列に、電流が流れたときにその痕跡が残る溶断素子14を接続する。これにより、半導体装置100に過電圧が印加されると、ツェナダイオード13にツェナ電流が流れ、それに伴い溶断素子14にも電流が流れる。従って、その溶断素子14の状態から、半導体装置100に過電圧が印加されたことを確認することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明の目的は、フューズ材料を切断することで、不良ビットを冗長ビットに置き換える機能を有し、特に耐帯電性に優れ、信頼性の高い半導体装置およびその製造方法を提供することである。

【解決手段】本発明の半導体装置においては、特にフューズ材料を切断できるようにフューズ層形成領域の上部に積層される保護層が除去されて形成されるフューズ窓部内に少なくともその一部が露出され、フューズ層形成領域の上部に積層される最上部配線層により形成されるアンテナ部を有することにより、半導体装置が帯電した時に表面に付着する荷電粒子の退避経路を形成する。これにより、従来フューズ切断部から荷電粒子が貫入することにより生じていた当該装置の帯電破損を防止する。

(もっと読む)

半導体装置

【課題】電気フューズのプロセスバラツキに起因する動作不良がほとんど発生しない半導体装置を提供する。

【解決手段】互いに並列接続された電気フューズ11,12を用いる。電気フューズ11,12の一方の端子は、高電位印加線611とグランドとの間に直列に接続されたPチャネルトランジスタ71,72の接続点に接続されるとともに、Pチャネルトランジスタ73に接続される。電気フューズ11,12の他端は、低電位印加線621に接続される。電気フューズ11,12の両端子間に超高電圧を印加すると、電気フューズ11,12の一方または両方に破壊接続が生じ、情報が書き込まれる。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の固有の特性をチップから容易に識別することができる半導体装置及びその製造方法を得る。

【解決手段】 本発明に係る半導体装置は、ロットごとに処理されたウェハをチップごとに分割して製造された半導体装置であって、半導体装置が属するロット名又はウェハ番号を示す識別子がチップの表面に付されている。または、半導体装置の固有の特性を示す識別子がチップの表面に付されている。そして、識別子の抵抗値により情報が識別されるように構成するのが好ましい。

(もっと読む)

可変集積インダクタ

【課題】2個以上の値の間で切替え可能なインダクタンス値を有する可変集積インダクタについて記載する。

【解決手段】好適な実施形態において、可変集積インダクタは、一対の2次インダクタに電磁結合されたマルチループ1次インダクタを含んでいる。2次インダクタは互いに接続されて閉回路を形成しており、その内部で2次インダクタは、マルチループ1次インダクタにより出力されるインダクタンス値を変化させるように直列接続と並列接続との間で切替え可能な可変トポロジを有している。一応用例において、可変集積インダクタは、マルチバンドRF無線トランシーバ(例えば、無線通信装置)で使用可能な種類である電圧制御発振器(VCO)内で用いられる。他の応用例において、可変集積インダクタは、同調増幅器負荷、インピーダンス整合ネットワーク、デジタル制御発振器、または他の任意の種類の周波数選択LCネットワークに利用可能である。

(もっと読む)

電気回路中にて静電気放電保護素子として用いるためのゲート制御されたフィン型抵抗素子、および、電気回路内部を静電気放電から保護するための保護装置

【課題】電気回路中にて静電気放電保護を確実化しながら小型化を実現する。

【解決手段】電気回路において静電気放電保護素子として使用するためのゲート制御されたフィン型抵抗素子は、第1端子領域、第2端子領域、および、第1端子領域と第2端子領域との間に形成されたチャネル領域を有するフィン構造体を備えている。さらに、フィン型抵抗素子は、チャネル領域の上面の一部上に少なくとも形成されたゲート領域を備えている。ゲート領域は、ゲート制御部に電気的に結合されており、ゲート制御部は、ゲート領域に印加される電気的な電位を制御することにより、電気回路が第1動作状態である間は、ゲート制御されたフィン型抵抗素子の電気抵抗を高くし、静電気放電現象の開始によって特徴付けられている第2動作状態では、電気抵抗をより低くする。

(もっと読む)

半導体装置

【課題】 静電保護回路と終端回路を小面積で実現可能な半導体装置を提供する。

【解決手段】 信号端子INから入力バッファBufに至る信号ノードND1と電源電圧ノードVDDとの間に静電保護機能を備えたPMOSトランジスタMP1を設け、更に、PMOSトランジスタMP1のゲートに参照電圧Vrefpを供給する電圧生成回路VG_pを設け、電圧生成回路VG_pによって参照電圧Vrefpを制御し、PMOSトランジスタMP1のソース−ドレイン間の抵抗値を設定する。これによって、PMOSトランジスタMP1は、静電保護機能に加え、信号端子INに接続される伝送線路等の特性インピーダンスに応じて抵抗値を設定可能な終端抵抗として機能させることが可能になる。

(もっと読む)

1 - 20 / 22

[ Back to top ]