Fターム[5F038AV10]の内容

Fターム[5F038AV10]に分類される特許

1 - 20 / 173

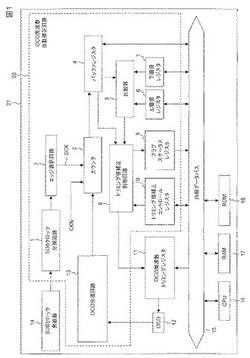

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

半導体装置

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体装置

【課題】トリミング回路を備えた半導体装置において、内部電源の電圧レベルを半導体装置の外部から適切に制御できるようにすること。

【解決手段】半導体装置は、複数のレベルの間で遷移する第1のテストモード信号を受信し、第1のテストモード信号の遷移に応じてカウント動作を行うバイナリカウンタ回路と、バイナリカウンタ回路の所定のビットの値を示すビット信号、および、バイナリカウンタ回路のカウント動作を制御する第2のテストモード信号を受信し、ビット信号および第2のテストモード信号に応じて、第1のテストモード信号を遷移させるか否かを制御する制御回路と、バイナリカウンタ回路のカウント値に応じて、複数の基準電位の中からいずれかの基準電位を選択するセレクタと、セレクタにより選択された基準電位に応じて、内部電源を発生する内部電源発生回路と、を備える。

(もっと読む)

ヒューズ回路及びトリミング良否判定方法

【課題】ヒューズ開口部の端部に必ず切断すべきヒューズを配設することにより、レーザー照射後のその切断/未切断をもって、端部のポリイミド膜の膜厚の良否を容易に判定する。

【解決手段】ヒューズ回路は、ヒューズ開口部FAの、ポリイミド膜の厚さが不本意に厚く残りやすい端部に配設された2つの切断確認用ヒューズ1a,1bと、ポリイミド膜の厚さ変動が端部に比べ少ない領域RAに配設された複数の実使用ヒューズ7a〜7dと、2つの切断確認用ヒューズ1a,1bからの信号を入力して当該ヒューズ1a,1bが確実に切断されているかを判定するヒューズ未切断判定回路2と、を備えている。なお、ヒューズ未切断判定回路2は、更にテストモード信号を入力すると共に、出力回路(例えばDQ回路)に判定結果を出力している。

(もっと読む)

半導体装置

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

半導体装置

【課題】回路規模が増大化する。

【解決手段】抵抗値が順に小さい値となって直列接続される複数のヒューズを備えるヒューズ部と、前記ヒューズ部の複数のヒューズのそれぞれ一端と、第1の電源電圧との間に接続される複数の選択スイッチと、前記第1の電源電圧から所定の電位差を有するヒューズ溶断用電圧を、前記ヒューズ部の最も小さい抵抗値のヒューズ側に出力するヒューズ溶融電圧出力回路と、ヒューズ溶断時に、前記ヒューズ溶融電圧出力回路が前記ヒューズ溶断用電圧を出力し、前記ヒューズ部の最も大きい抵抗値のヒューズに接続される選択スイッチから最も小さい抵抗値のヒューズに接続される選択スイッチまでを順に導通させる制御回路と、を備える半導体装置。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

半導体ウェハ、半導体装置、及び半導体装置の製造方法

【課題】ヒューズメモリを利用したトリミングを行う半導体ウェハにおける各半導体チップの回路面積を小さくする。

【解決手段】半導体ウェハ10におけるシリコン基板上は、複数個のチップ領域TARとこの領域TARを囲むスクライブ領域SARとに区画されている。チップ領域TARには、トリミング対象回路11と、ヒューズ素子Fm(m=1〜2M)と、ヒューズ素子Fm(m=1〜2M)が断線状態であるか否かを検出する検出回路としての役割を果たす定電流源IPm(m=1〜2M)及びインバータINm(m=1〜2M)とが形成されている。スクライブ領域SARには、制御信号に応じてON/OFFが切り換わり、ONとなることによりヒューズ素子Fm(m=1〜2M)を断線させる電流を発生するNチャネル電界効果トランジスタTSm(m=1〜2M)がある。

(もっと読む)

可変容量回路

【課題】キャパシタが破壊されずAC信号が歪まないようにした可変容量回路を提供する。

【解決手段】可変容量回路は,基準電位を中心とする交流信号が印加される所定ノードと,所定ノードに接続される第1のキャパシタと,第1のキャパシタと基準電位との間に接続された第2のキャパシタと,第2のキャパシタと第1のキャパシタとの間の第1のノードと基準電位との間に設けられた第3のキャパシタ及び容量制御用のトランジスタと,第3のキャパシタとトランジスタとの間の第2のノードに第1のバイアス電圧を印加するバイアス回路とを有する。

(もっと読む)

垂直集積システム

【課題】コストのかかる空間をとらずに電子部品内に個別パッシブ部品を組み込むことが可能な垂直集積システムを提供する。

【解決手段】集積回路システム100は、半導体ダイ110の前面上に製造された第一のアクティブ層と、半導体ダイ110の裏面上の第二の予め製造された層とを含み、その第二の予め製造された層は、その中に埋め込まれた電気部品を有し、その電子部品は、少なくとも一つの個別パッシブ部品140を含む。また、集積システム100は、第一のアクティブ層及び第二の予め製造された層を結合する少なくとも一つの電気経路150も含む。

(もっと読む)

抵抗分割回路及び電圧検出回路

【課題】スイッチ素子のオン抵抗の影響を排除することにより、トリミングの誤差が特定の条件において大きくなることを回避することができる抵抗分割回路、さらには精度がよい電圧検出回路を提供する。

【解決手段】直列接続した抵抗値に重み付けをした複数の抵抗素子と、抵抗素子とそれぞれ並列に接続されたスイッチ素子とを備えた抵抗分割回路で、対応する抵抗素子の抵抗値とスイッチ素子がショート状態のときの抵抗値との比を一定となるように構成した。

(もっと読む)

半導体装置の製造方法

【課題】積層したMIMキャパシタの静電容量の合計値を所望の静電容量に近づけることができる半導体装置の製造方法を得る。

【解決手段】半導体基板1上に、下地金属膜2、下層絶縁膜4、及び中間金属膜5を順に積層する。下層絶縁膜4の厚みを測定する。下層絶縁膜4の厚みを測定した後に、中間金属膜5上に上層絶縁膜7、及び上地金属膜8を順に積層する。下地金属膜2、下層絶縁膜4、及び中間金属膜5から第1のMIMキャパシタが構成される。中間金属膜5、上層絶縁膜7、及び上地金属膜8から第2のMIMキャパシタが構成される。第1のMIMキャパシタの静電容量と第2のMIMキャパシタの静電容量の合計値が所望の静電容量に近づくように、測定した下層絶縁膜4の厚みに基づいて、上層絶縁膜7及び上地金属膜8の少なくとも一方の設計条件を調整する。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

半導体装置

【課題】半導体装置に損傷を与えることなく、単体の抵抗素子自体の抵抗値を精度良く微調整する。

【解決手段】P型の半導体基板10上にN型の半導体層11が形成されている。半導体層11の表面には薄い第2の絶縁膜13が形成され、第1の絶縁膜12及び第2の絶縁膜13上にフローティングポリシリコン層14が形成されている。フローティングポリシリコン層14は第3の絶縁膜15に覆われている。第3の絶縁膜15によって覆われたフローティングポリシリコン層14上にはポリシリコン抵抗層16が形成されている。そして、半導体層11とポリシリコン抵抗層16との間に電圧を印加することにより、第2の絶縁膜13を通してフローティングポリシリコン層14の中に電子が注入され、ポリシリコン抵抗層16の中に正孔蓄積層16Aが形成される。

(もっと読む)

保護素子およびそれを備えた半導体装置

【課題】被保護素子に接続されることにより、被保護素子の破壊を未然に防止できる保護素子を提供すること。

【解決手段】アノード電極15とカソード電極16との間に主たる電流を流す被保護素子に対して、電気的に並列に接続される保護素子1であって、GaN層13よりもバンドギャップの大きなAlGaN層14が形成され、AlGaN層14の表面に離間してアノード電極15とカソード電極16とが形成され、アノード電極15とカソード電極と16の間の2次元電子ガス層13Aを流れる電流のオンオフを制御する制御電極19を備えたオンオフ可能領域21を備え、制御電極19が所定の抵抗体20を介してアノード電極15に接続されてなり、アノード電極15が被保護素子のアノード電極15と接続され、カソード電極16が被保護素子のカソード電極16と接続され、被保護素子より耐圧が低く設定されている。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスからの検出信号の精度の高いA/D変換を実現できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、電源電圧VDDAを生成する電源回路60と、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAに基づいて動作し、電源電圧VDDAにより規定されるA/D変換範囲で、センサーデバイス30からの検出信号に対応する信号についてのA/D変換を行うA/D変換器ADCと、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAをセンサーデバイス30に供給する電源端子PVDAを含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上にザッピング素子1のヒューズ層12を形成し、ヒューズ層12を覆う第1の絶縁膜13を形成する。第1の絶縁膜13上にはヒューズ層12を覆うエッチングストッパー膜14を形成し、エッチングストッパー膜14を覆う第2の絶縁膜16を形成する。他の工程を経た後、第1のエッチング工程として、ヒューズ層12上で、第2の絶縁膜16をエッチングストッパー膜14に対して選択的にエッチングすることにより、エッチングストッパー膜14の表面を露出させる。次に、第2のエッチング工程として、ヒューズ層12上で、エッチングストッパー膜14を第1の絶縁膜13に対して選択的にエッチングすることにより、第1の絶縁膜13の表面を露出させる。

(もっと読む)

半導体装置

【課題】高周波動作向けの半導体装置を高性能化させる。

【解決手段】シリコン基板S1上に形成された抵抗素子TDR1および不揮発性メモリNVM1を有する半導体装置であって、不揮発性メモリNVM1は、シリコン基板S1上に埋め込み酸化層BOX1を介して配置されたシリコン層SOI1に形成されている。特に、抵抗素子TDR1と不揮発性メモリNVM1とは互いに電気的に接続され、不揮発性メモリNVM1のオン状態またはオフ状態により、抵抗素子TDR1の導通状態または非導通状態が切り替わる。

(もっと読む)

半導体装置、及びその設計方法

【課題】小さいチップサイズで、ノイズを低減することできる半導体装置、及びその設計方法を提供すること。

【解決手段】本発明の一態様に係る半導体装置は、入力に応じて容量が変化する素子13を備え、所定の機能を有する機能マクロ11と、機能マクロ11の不使用時において、素子13によって機能マクロ11の容量を制御するものである。これにより、小さいチップサイズで、ノイズを低減することできる半導体装置、及びその設計方法を提供することができる。

(もっと読む)

1 - 20 / 173

[ Back to top ]