Fターム[5F038BB06]の内容

Fターム[5F038BB06]に分類される特許

1 - 20 / 51

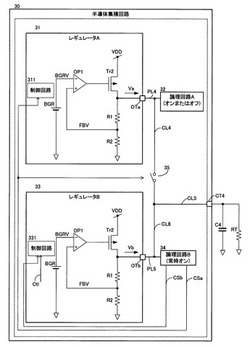

半導体集積回路

【課題】本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減する。

【解決手段】

半導体集積回路30は,第1,第2の出力端OTa,OTbと,外部容量C4に接続する外部接続端子CT4との間に設けられたスイッチ回路35を有し,

スイッチ回路35の一端は第1の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4および第2の出力端OTbに接続され,

スイッチ回路35は,第1のレギュレータA31が第1の電源電圧Vaを第1の論理回路A32に対して供給する期間はオンし,第1のレギュレータA31が第1の論理回路A32に対する電源電圧供給を停止する期間はオフする。

(もっと読む)

縦構造キャパシタを備える半導体装置

【課題】縦構造キャパシタの剥離を防止し、チップサイズの増加を抑制した半導体装置を提供する。

【解決手段】半導体装置には、第1の回路の機能素子として使用される第1の縦構造キャパシタと、第2の回路の機能素子として使用され、第1の縦構造キャパシタよりも容量値の大きい第2の縦構造キャパシタと、が含まれている。半導体装置では、第1の縦構造キャパシタを、第2の縦構造キャパシタに隣接、又は、包含させるようにレイアウトする。

(もっと読む)

半導体装置及びその駆動方法

【課題】2つの電位の誤差を増幅して出力する半導体装置におけるスタンバイ状態からの復帰に際して生じる動作遅延を抑制する。

【解決手段】チャネルが酸化物半導体層に形成されるトランジスタによって、トランスコンダクタンスアンプの出力端子とキャパシタの一方の電極の電気的な接続を制御する。よって、トランスコンダクタンスアンプがスタンバイ状態となる場合であっても、当該トランジスタをオフ状態とすることでキャパシタの一方の電極において長期に渡って電荷の保持を行うことが可能となる。また、トランスコンダクタンスアンプをスタンバイ状態から復帰する際には、当該トランジスタをオン状態とすることで、キャパシタの充放電を早期に収束させることができる。これにより、早期に当該半導体装置の動作を定常状態とすることが可能となる。

(もっと読む)

集積回路装置及び電子機器

【課題】簡素な構成で、電圧発生回路の電源電圧が上昇した場合でも出力電圧の変動を精度よく抑制できる集積回路装置及び電子機器等を提供する。

【解決手段】集積回路装置100は、ソース同士が接続された第1の入力トランジスター及び第2の入力トランジスターにより構成される入力差動対と、第1の入力トランジスターのドレイン電圧に基づいてゲート電圧を制御される出力トランジスターと、第1の入力トランジスターのドレイン電流と第2の入力トランジスターのドレイン電流との差の電流を出力トランジスターのゲートに供給するカレントミラー回路と、出力トランジスターのゲート及びドレインの間に挿入される第1の容量と、入力差動対を構成するトランジスターの少なくとも一方のソース・ドレイン間に流れる電荷量に対して、第2の電圧に対する第1の電圧の上昇分に対応した電荷量を増加させる電圧変動抑制回路とを含む。

(もっと読む)

電磁気干渉ノイズ低減回路

【課題】ドライバICでのEMIノイズを低減するためのEMIノイズ低減用電源回路を提供することである。

【解決手段】本発明の回路は、入力ポートと、少なくとも1つの出力ポートとを備えて外部機器を駆動するドライバICで、前記出力ポートに流入するEMIノイズを低減するためのものであって、前記ドライバICの前記少なくとも1つの出力ポートと、前記外部機器を接続する出力端との間に、それぞれ直列に配置される、少なくとも1つの抵抗を含む。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】複数の基準電位を要する半導体装置、及び半導体装置の駆動において、より消費電力を軽減する。

【解決手段】電源線に直列に接続された複数の抵抗素子により、電源線に供給された電位を抵抗分割し、電源線と電気的に接続するスイッチトランジスタを介して所望の分割された電位を出力する電位分割回路を有する半導体装置であり、スイッチトランジスタのドレイン端子は出力側の回路に設けられたトランジスタのゲート端子(又は容量素子の一方の端子)と電気的に接続しノードを構成する。

(もっと読む)

半導体装置及びその内部回路の制御方法

【課題】従来の半導体装置は、チップ面積を抑制しながら内部電源電圧の変動を抑制することができなかった。

【解決手段】本発明の半導体装置は、電源電圧の電圧値を他の電圧値に変換して内部電源電圧を生成する第1の電源回路PWR0、第2の電源回路PWR1と、第1の配線MT02を介して第1の電源回路PWR0から内部電源電圧VDL0の供給を受ける第1の内部回路MA0と、第2の配線MT12を介して第2の電源回路PWR1から内部電源電圧VDL1の供給を受ける第2の内部回路MA1と、第1の配線MT02と第2の配線MT12とを互いに接続するブロック間配線MT3と、第1の内部回路MA0と第2の内部回路MA1が同時に動作する期間の長さを制御する制御回路CNT0、CNT1と、を有する。

(もっと読む)

電圧レギュレータを有する集積回路装置

【課題】集積回路装置のモード端子の数を低減する。

【解決手段】第1の電源端子VCCに接続され第1の電源電圧VDDEを供給する第1の電源配線11と,第1の電源電圧VDDEから第2の電源電圧VDDIを生成し第2の電源配線13に出力する電圧レギュレータ12と,電圧レギュレータの出力に接続され外部キャパシタが接続されるキャパシタ端子Cと,キャパシタ端子に印加される電圧に従い第1の状態と第2の状態とを判定する判定回路21とを有する。この判定回路は、キャパシタ端子Cに第3の電源電圧が印加されないで電圧レギュレータが動作する第1の動作モードと,キャパシタ端子Cに第3の電源電圧が印加されると共に電圧レギュレータが停止する第2の動作モードとを切り換えるので、モード端子数を削減することができる。

(もっと読む)

インバータ回路

【課題】1チップ化しつつ、高温化による誤動作を抑制し、かつ、半導体パワー素子に流れる電流を低減し、チップサイズの増大を抑制することができるインバータ回路を提供する。

【解決手段】コンバータ電源回路部2の電源供給ライン8中、例えば、IPD20におけるパワーMOSFET220のハイサイド側に電流制限抵抗240を備える。この電流制限抵抗240によって電源供給ライン8に流れる電流の電流値を制限することができるため、パワーMOSFET220での発熱を抑制することが可能となる。したがって、インバータ回路1内の素子の定格温度を超えることを防止することが可能となり、誤動作が生じることを抑制できる。これにより、インバータ回路1の信頼性の向上を図ることが可能となる。また、パワーMOSFET220として必要な能力を軽減することが可能となり、大面積な素子としなくても済む。

(もっと読む)

昇圧回路、昇圧装置及び半導体集積回路

【課題】電源ノイズ及び接地ノイズを低減することができる昇圧回路を提供すること。

【解決手段】本発明は、MOS容量C1、駆動回路10及びトランジスタ3を備える。MOS容量C1のゲートは出力端子VOUTと接続され、正の電荷が蓄積される。駆動回路10は、入力信号に応じて、MOS容量C1の一端に電源電圧VCCを出力し、又はMOS容量C1の他端にグランド電圧GNDを出力する。トランジスタ3は、出力端子VOUTと電源電圧VCCとの間に接続される。駆動回路10がMOS容量C1に電源電圧VCCを出力する場合は、トランジスタ3はOFFとなる。一方、駆動回路10がMOS容量C1にグランド電圧GNDを出力する場合は、トランジスタ3はONとなる。

(もっと読む)

半導体装置

【課題】昇圧回路の出力側に抵抗を挿入しつつも、内部電源電圧として十分な電圧を確保するとともに、抵抗での消費電力を削減する。

【解決手段】

半導体装置1aは、外部電源電圧VDDに応じた昇圧幅で内部電源電圧VCCを昇圧する昇圧回路10aと、外部電源電圧VDDと所定のリファレンス電圧VREF1とを比較する外部電圧レベル比較回路21aと、昇圧回路10aの出力端子に接続された可変抵抗を有する可変抵抗回路20aとを備え、可変抵抗回路20aは、外部電圧レベル比較回路21aの比較結果に応じて可変抵抗の抵抗値を制御する。

(もっと読む)

半導体装置および電子機器

【課題】電源電圧除去比の低減化を図ることが可能な半導体チップを提供する。

【解決手段】この音声信号処理装置は、半導体集積回路装置3の2個の外部ピンP4,P5にコンデンサ2の一方電極を接続し、コンデンサ2の他方電極を接地し、VR2発生回路14で生成した参照電圧VR2を保護回路10、外部ピンP5,P4、保護回路9を介してD/A変換器13の参照電圧ノード13aに与える。したがって、外部ピンP4を使用せず、VR2発生回路14の出力のノード14aをD/A変換器13の参照電圧ノード13aに接続していた従来に比べ、電源電圧除去比が小さくなる。

(もっと読む)

半導体装置

【課題】所定レベルの電圧を早期に生成するとともに、回路規模の増大を防ぐことが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1の電源電圧が供給される第1電源ノードと第1の電源電圧よりも低い第2の電源電圧が供給される第2電源ノードとの間に接続され、第1電源ノードからキャパシタCが電気的に接続されるべき基準ノードへ電流を流すことにより、キャパシタCを充電し、基準ノードの電位を所定電圧レベルにするための基準電圧生成回路11と、第1電源ノードと基準ノードとの間に直列接続された抵抗およびスイッチ、または第1電源ノードと基準ノードとの間に接続されたトランジスタを含み、第1電源ノードから基準ノード経由でキャパシタCへ電流を流すことにより、基準電圧生成回路11よりも速くキャパシタCを充電することが可能な充電加速回路10とを備える。

(もっと読む)

半導体集積回路装置

【課題】

本発明は、外部電源の立ち上げ時にあっても安定した基準電位が得られる半導体集積回路装置を提供する。

【解決手段】

入力される第1の信号vbgrと第2の信号との電位差に応じて第3の信号を出力する第1の出力部を備える差動対と、第3の信号がゲートに入力されるトランジスタP3、トランジスタP3のドレインと接地電位との間に接続される抵抗R1,R2,VR、トランジスタP3のドレインから第4の信号vrefを出力する第2の出力部及び抵抗R1,R2,VRによって第4の信号vrefを分圧した第2の信号を出力する第3の出力部を備えるバイアス回路と、第1の出力部と第2の出力部との間に設けられ、差動対とバイアス回路に接続されるキャパシタC1と、少なくともキャパシタC1と差動対との間又はキャパシタC1とバイアス回路との接続を開閉する開閉部とを含む電位調整回路を備えることを特徴とする半導体集積回路装置。

(もっと読む)

2トランジスタ方式による基準電圧発生器

進歩した電圧基準発生器が提供される。電圧基準発生器は、第1のトランジスタであって、第1のトランジスタを弱い反転モードに置くようにバイアスされたゲート電極を有する第1のトランジスタと、前記第1のトランジスタと直列に接続された第2のトランジスタであって、第2のトランジスタを弱い反転モードに置くようにバイアスされたゲート電極を有する第2のトランジスタとを含み、第1のトランジスタのスレッショルド電圧が第2のトランジスタのスレッショルド電圧よりも小さく、また第2のトランジスタのゲート電極が第2のトランジスタのドレイン電極および第1のトランジスタのソース電極に電気的につながれて基準電圧の出力を構成するようになっている。  (もっと読む)

(もっと読む)

半導体集積回路装置及び電源供給回路

【課題】低消費電流化を実現しつつ、多様な機能回路の各々に対して個別に適切な電源電圧の制御を可能とする半導体集積回路装置及び電源供給回路を提供する。

【解決手段】半導体集積回路装置は電源供給回路と少なくとも1つの機能回路とを含み、前記電源供給回路は、外部電源電圧から降圧電圧を生成する少なくとも1つの降圧回路と、前記外部電源電圧と少なくとも1つの比較電圧とを比較し、比較結果に応じて、前記機能回路に前記外部電源電圧及び前記降圧電圧のうちの何れかの電圧を選択してこれを前記機能回路に供給する。

(もっと読む)

ドライバIC、電気光学装置及び電子機器

【課題】パネルへの接続のための信号線引き回しが少なく、かつチップサイズの縮小を図ったドライバIC等を提供する。

【解決手段】ドライバIC100の長手方向にて三分割し、中央の第1領域100Aにはデータ線ドライバ130を、第2領域100Bには第1走査線ドライバ142Aを、第3領域100Cには第2走査線ドライバ142Bを、それぞれドライバICの長辺100Dに沿って配置し、他の長辺100Eに沿ってインターフェース領域102を配置する。第1領域には、昇圧回路140AとRAM110とを配置する。第2領域には、第1電源回路140Bを配置する。第3領域には、第2電源回路140Cを配置する。第1領域に配置した第1電源回路からの内部基準電位Vrefを、第2領域を経由して、第3領域に配置した第2電源回路内の内部電源電位生成回路140Fに伝送する。内部基準電位は、ボルテージフォロアを介して電源配線層に供給する。

(もっと読む)

半導体装置

【課題】無線通信によりデータの交信が可能な半導体装置において、ノイズの影響を抑える。またノイズが抑制された定電圧を用いて、受信電力が大きい場合において、正常な通信を行う。

【解決手段】交流信号から直流電圧を生成する入力回路と、前記直流電圧以下の定電圧を生成する回路と、前記定電圧が供給される回路部と、フィルタと、前記定電圧を生成する回路から入力される前記定電圧によりインピーダンスが変化するフィードバック回路と、を有し、前記フィルタは前記入力回路と前記定電圧を生成する回路との間に電気的に接続されている。

(もっと読む)

半導体装置

【課題】本発明は、配線抵抗成分をセンス抵抗として利用しながら、過電流保護回路の検出精度を向上することが可能な半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、監視対象となる電流ラインの配線抵抗成分であるセンス抵抗Rsと、センス抵抗Rsでの降下電圧と所定の閾値電圧を比較して過電流保護信号Socpを生成する過電流保護回路OCPと、前記電流ラインの形成工程と同一の工程により、他の回路要素から電気的に分離して形成されたダミーラインの配線抵抗成分であって、センス抵抗Rsよりも大きな抵抗値を有するダミー抵抗Rdと;ダミー抵抗Rdの両端に各々接続されたダミーパッドT1、T2と;を集積化して成り、過電流保護回路OCPは、前記閾値電圧を調整するための閾値電圧調整部を有する構成とされている。

(もっと読む)

バススイッチおよび電子スイッチ

【課題】バスに異常が発生したとしても当該異常状態を回避して通常動作を維持できるようにする。スイッチング素子をオフしたときにも生じる寄生素子によるリーク電流の発生を抑制して正常な切断を可能にする。

【解決手段】ハイサイドスイッチSWHが高電位側バスDnHの入力端子INHと出力端子OUTHとの間に接続されていると共に、ロウサイドスイッチSWLが低電位側バスDnLの入力端子INLと出力端子OUTLとの間に接続されているため、当該スイッチSWHおよびSWLが共にオフすることでモジュール間のバス接続を確実に切断することができ、たとえバスに異常が発生したとしても安定した動作を保持できる。ロウサイドスイッチSWLおよびハイサイドスイッチSWHは、MOSトランジスタM1、M2がソース共通で直列接続されているため寄生素子が発生しにくく、ゲート‐ソース間が抵抗接続されているため幅広い電圧範囲に対して確実にバス接続を切断することができる。

(もっと読む)

1 - 20 / 51

[ Back to top ]