Fターム[5F038BE05]の内容

Fターム[5F038BE05]に分類される特許

1 - 20 / 119

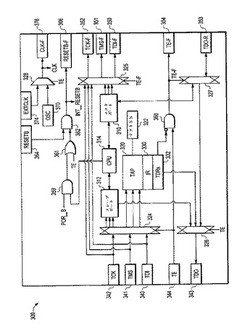

マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

(もっと読む)

半導体装置

【課題】

実施形態は、解析が簡便な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、内部信号を伝送可能な第1配線101と、第1配線101

と電気的に接続された測定電極100と、測定電極100と隣接するように配置され、内

部信号を計測するときに接地電位VSSが印加され、内部信号を計測する以外のときに所

望の電圧が印加されたダミー電極102,103とを備える。

例えば、測定電極100は、環状に形成されており、ダミー電極は、第1電極102と

第2電極103とを有し、第1電極102は、測定電極100の内側に形成された空間に

隣接するように配置され、第2電極103は、測定電極100の外側に隣接するように配

置される。

(もっと読む)

温度検出回路

【課題】 消費電流を抑えるため間欠動作するようにした温度検出用半導体集積回路において、外部端子を増加させることなく回路の評価および検査が行えるようにする。

【解決手段】 発振回路(16)を備え、消費電流を抑えるため間欠動作する温度検出用半導体集積回路において、温度検出回路(11)の出力と基準電圧とを比較する電圧比較回路(13)の出力に対応した信号を出力する外部端子(DET)と、該外部端子に負電位が印加されたことを検出した場合に、温度検出回路と基準電圧回路と電圧比較回路を活性化させる信号を生成する制御回路(17)と、制御回路が活性化信号を出力しかつ温度検出回路の出力が基準電圧を超えたと電圧比較回路(13)が判定した場合に電流を流す電流回路(SW1,R0,SW2)とを設けるようにした。

(もっと読む)

半導体集積回路

【課題】不揮発性メモリを搭載した半導体集積回路において、外部端子を通して不揮発性メモリの特性テストを実施し、更に、その外部端子にサージ電圧が印加された場合であっても、そのサージ電圧が不揮発性メモリに伝わることを防止する。

【解決手段】半導体集積回路は、不揮発性メモリと、不揮発性メモリに対するデータ書き込み時、書き込み電圧が印加される書き込み制御線と、書き込み制御線に接続された第1ノードと、第1スイッチ回路を介して第1ノードに接続された外部端子と、スイッチ回路を介さずに外部端子に接続された第1ESD保護回路と、動作モードに応じて第1スイッチ回路をON/OFF制御する制御回路と、を備える。動作モードは、外部端子を用いて不揮発性メモリの特性テストを行うテストモードと、外部端子を使用しないユーザモードと、を含む。テストモードにおいて、制御回路は、第1スイッチ回路をONする。ユーザモードにおいて、制御回路は、第1スイッチ回路をOFFする。

(もっと読む)

半導体装置

【課題】複数の半導体チップの各々の信号端子が共通の外部端子に接続される場合であっても、半導体装置のオープン不良を検出する。

【解決手段】半導体装置は、複数の半導体チップと、外部と接続される電源端子、第1及び第2の外部端子と、を備え、複数の半導体チップのそれぞれは、第1の信号端子(第1の信号パッドT1)に供給される信号に基づくクロック信号によって計数を行うカウンタ部42と、複数の半導体チップの中で自己の半導体チップを固定的に識別し、識別情報を出力する識別情報認識部と、カウンタ部42の出力と識別情報を比較し、比較した比較結果に基づいて、第2の信号端子(第2の信号パッドT2)と電源端子との導通/非導通状態を制御する比較回路43と、を有し、複数の半導体チップの各々の第1の信号端子は、共通の第1の外部端子に接続され、複数の半導体チップの各々の第2の信号端子は、共通の第2の外部端子に接続される。

(もっと読む)

半導体装置

【課題】兼用パッドのサイズを専用パッドよりも大きくするとともに、半導体装置のサイズ増大を抑制する。

【解決手段】半導体装置は、第1の方向に延伸された第1のエッジE1と、第1の方向と実質的に直交する第2の方向に延伸された第2のエッジE2とを含む半導体チップ10と、半導体チップ上に形成され、互いに第2の方向に沿った長さが実質的に等しい複数の第1グループパッドGP1と、半導体チップ上に形成され、第2の方向に沿った長さが、複数の第1グループパッドの第2の方向に沿った長さよりも長い、第2グループパッドGP2と、を備える。複数の第1グループパッドと第2グループパッドとは、第2グループパッドと第2のエッジとの間に複数の第1グループパッドのいずれをも含まずに、第1の方向に沿って一列に並んで配置されている。

(もっと読む)

半導体集積回路およびその検査方法

【課題】半導体集積回路に内蔵されたアナログ/デジタル変換器をテストするためのテスト信号発生器として半導体集積回路に内蔵されたデジタル/アナログ変換器を使用する際に、デジタル/アナログ変換器が正常なデジタル/アナログ変換動作を実行可能であるか否か動作検証することを可能とすること。

【解決手段】半導体集積回路1は、アナログ/デジタル変換器(ADC)5とデジタル/アナログ変換器(DAC)6とを内蔵する。DAC6は、ADC5をテストするためのテスト信号生成器として使用可能とされる。半導体集積回路1は、DAC6の出力端子とADC5の入力端子の間に入力端子と出力端子とが接続されたバッファ増幅器7を更に具備する。バッファ増幅器7の出力端子とADC5の入力端子のいずれか一方は、半導体集積回路1の外部端子(T1、T2)として外部に導出される。

(もっと読む)

マルチチャネル半導体装置及びそれを具備したディスプレイ装置

【課題】別途のプローブ接続用パッドなしに、出力チャネルの個数より少ない個数のプローブを接続して多数の出力チャネルの出力信号をモニタリングすることができるマルチチャネル半導体装置及びそれを具備するディスプレイ装置を提供する。

【解決手段】少なくとも1つの出力バッファを具備する複数のバッファ・グループ;少なくとも1つの出力パッドを具備する複数のパッド・グループ、及び複数のバッファ・グループ;複数のパッド・グループとの連結を制御するチャネル・スイッチング部;を含むマルチチャネル半導体装置であり、該複数のパッド・グループのうち1つのパッド・グループは、第1動作モードで、対応するバッファ・グループの出力信号を出力し、第2動作モードで、複数のバッファ・グループの出力信号を順次に出力する。

(もっと読む)

テストモード設定回路

【課題】端子数の少ないテストモード設定回路を提供する。

【解決手段】半導体装置のテストモードを制御するテスト端子に、低閾値電圧のディテクタと高閾値電圧のディテクタを設け、低閾値電圧のディテクタによって論理回路のリセットを解除し、高閾値電圧のディテクタでテストモードを切替え制御するような構成にした。従って、テスト端子とリセット端子とテストモード制御端子が共通になり、端子の数を大幅に削減することが可能である。

(もっと読む)

テスト回路、及び、シリアルI/F回路、半導体装置

【課題】半導体パッケージにテストモード時にのみ使用される端子を設けなくても、テストモードの設定及びテストモード設定後のテスト信号入力ができるテスト回路を提供する。

【解決手段】複数の電圧レベルを含むパルスパターンを有するテストモード用電圧と基準電圧とを比較して、トリガー信号及びデータ信号を含むパルス信号をそれぞれ出力する複数の比較器6a〜6cと、トリガー信号に基づいてデータ信号をシリアル/パラレル変換してテスト信号を生成し、テスト信号を被テスト回路9に供給するテスト信号生成回路5とによってテスト回路を構成する。

(もっと読む)

半導体装置

【課題】パッケージのピン数が変更された場合でも設計変更を必要としない半導体装置を提供する。

【解決手段】半導体装置に設けられた第1の選択部50は、機能ブロック群23と複数のパッド33との間の信号の経路に設けられ、各パッドごとに、標準設定として割当てられた複数の信号うち1つの信号を選択する。レジスタ61は、少なくとも第1または第2のデータを保持する。第2の選択部51は、第1の選択部50と複数のパッド33との間の信号の経路に設けられる。第2の選択部51は、レジスタ61に第1のデータが保持されたときに、第1の選択部50によって選択された各信号を標準設定のパッドを介して外部との間で入出力可能にし、レジスタ61に第2のデータが保持されたとき、第1の選択部によって選択された複数の信号のうち少なくとも一部の信号を標準設定と異なるパッドを介して外部との間で入出力可能にする。

(もっと読む)

電圧レギュレータを有する集積回路装置

【課題】集積回路装置のモード端子の数を低減する。

【解決手段】第1の電源端子VCCに接続され第1の電源電圧VDDEを供給する第1の電源配線11と,第1の電源電圧VDDEから第2の電源電圧VDDIを生成し第2の電源配線13に出力する電圧レギュレータ12と,電圧レギュレータの出力に接続され外部キャパシタが接続されるキャパシタ端子Cと,キャパシタ端子に印加される電圧に従い第1の状態と第2の状態とを判定する判定回路21とを有する。この判定回路は、キャパシタ端子Cに第3の電源電圧が印加されないで電圧レギュレータが動作する第1の動作モードと,キャパシタ端子Cに第3の電源電圧が印加されると共に電圧レギュレータが停止する第2の動作モードとを切り換えるので、モード端子数を削減することができる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の検査方法

【課題】レギュレータ回路の検査用端子と他の機能端子との兼用を可能とする。

【解決手段】負荷電流印加回路は、スイッチ経路選択信号に基づいて負荷電流印加端子から負荷回路に検査用負荷電流を印加する。レギュレータ回路駆動用回路は、複数のスイッチ回路を備え、ゲート制御信号に基づいて負荷回路に供給する電流量を制御する。差動増幅器は、レギュレータ回路駆動用回路から出力される負荷電源電圧と、基準電圧とを比較する。ゲート制御信号選択回路は、差動増幅器の出力に基づいて、負荷電源電圧が所定の電圧になるようにゲート制御信号を生成してレギュレータ回路駆動用回路に出力する。検査するとき、ゲート制御信号選択回路は、複数のスイッチ回路のうちの所定のスイッチ回路を差動増幅器の出力に基づいて動作させ、他のスイッチ回路をオフ状態にするゲート制御信号を出力する。

(もっと読む)

TSVベースの3次元積層ICのためのテストアーキテクチャ

テスト回路

【課題】レイアウトが複雑になることを抑える。

【解決手段】テスト対象とされる複数の出力バッファ11のそれぞれに対応してサブテスト回路1aを備える。それぞれのサブテスト回路1aは、前段のサブテスト回路1aの出力が後段のサブテスト回路1aの入力に接続されてチェーン構成をなし、初段のサブテスト回路1aの入力には信号TDIを入力し、最終段のサブテスト回路1aの出力から信号TDOを出力する。サブテスト回路1aは、対応する出力バッファ11の出力値と入力における入力値とが異なる場合に、出力に信号TDIの論理値とは異なる論理値を出力する。

(もっと読む)

半導体装置および半導体装置の制御方法

【課題】簡単な構成により、用途が異なるパッドを同一のパッドで兼用することができる半導体装置および半導体装置の制御方法を提供する。

【解決手段】半導体装置100は、共用パッド120と、電源電位を生成する内部発生電源部110と、共用パッド120と内部発生電源110との間を接続状態または非接続状態にするNMOSスイッチ140と、共用パッド120に電源電位と異なる特定電位が供給された場合には、NMOSスイッチ140を非接続状態にするとともに、特定機能を指示する特定指示信号を出力し、共用パッド120に特定電位が供給されない場合には、NMOSスイッチ140を接続状態にする制御部130と、を含む。

(もっと読む)

半導体装置、半導体装置の試験方法、及びデータ処理システム

【課題】インターフェースチップを用いるタイプの半導体装置において、インターフェースチップとコアチップ間の複数の貫通電極にそれぞれ関する複数の電流パスで大きなAC特性の差がないことの確認試験を行えるようにする。

【解決手段】インターフェースチップ及びコアチップと、これらを電気的に接続するそれぞれが貫通電極を含む測定対象信号線130及び基準信号線131と、を備え、インターフェースチップは、信号発生回路100が発生したテストクロックをコアチップへ送出し、コアチップは、信号発生回路101がテストクロックから所定の測定信号を発生し、且つ所定の測定信号を測定対象信号線130及び基準信号線131へ同時に送出し、更に、インターフェースチップは、更に、測定対象信号線130及び基準信号線131を介して入力した複数の所定の測定信号の位相差をオペアンプ117によって検出し、判定回路102が試験結果を出力する。

(もっと読む)

電気回路

【課題】本発明は、端子数を低減した電気回路を提供することを目的とする。

【解決手段】第一回路と、該第一回路に接続された第一端子と、該第一回路と同時使用されない第二回路と、該第二回路に接続された第二端子と、該第一回路および該第二回路に接続された第三端子と、該第一回路および該第二回路に印加される電源電圧と所定の基準電圧とを比較し、該電源電圧と該基準電圧の大小に応じて該第一回路または該第二回路のいずれか一方を停止させる切り替え手段とを備える。そして、該切り替え手段により該第一回路を停止させた場合には該第二回路が該第二端子と該第三端子により信号の入出力を行い、該切り替え手段により該第二回路を停止させた場合には該第一回路が該第一端子と該第三端子により信号の入出力を行うことを特徴とする。

(もっと読む)

半導体集積回路

【課題】熱保護回路を備えたICにおいて、ICの端子数を削減してICチップの面積を小さくする。また、樹脂封止後においても熱保護回路の動作テストの実施を可能にする。

【解決手段】半導体集積回路100は、パワーアンプ15と、パワーアンプ15の異常発熱を検知してパワーアンプ15を保護する熱保護回路と、テスト電圧を印加するテスト端子を有し、テスト電圧に応じて熱保護回路の動作テストを行うテスト回路10と、制御電圧を印加する制御端子を有し、制御電圧に応じて内部回路の制御を行う制御回路16と、を備える。そして、テスト端子と制御端子とを1つの共通端子KPに共通化した。

(もっと読む)

半導体素子およびそれを用いた半導体装置ならびに半導体素子の検査方法

【課題】非接触結合回路を備えた半導体素子においては、検査にかかるコストが増大し、かかる半導体素子を有する半導体装置の製造コストが増大する。

【解決手段】本発明の半導体素子は、通信部と、検査用通信部を有し、通信部は、非接触で信号伝送を行う第1の非接触結合部を備え、検査用通信部は、第1の非接触結合部と非接触結合する第2の非接触結合部を備える。

(もっと読む)

1 - 20 / 119

[ Back to top ]