Fターム[5F038BG00]の内容

半導体集積回路 (75,215) | 電圧発生、昇圧 (1,671)

Fターム[5F038BG00]の下位に属するFターム

Fターム[5F038BG00]に分類される特許

1 - 14 / 14

半導体装置

【課題】信頼性に優れた半導体装置を提供する。

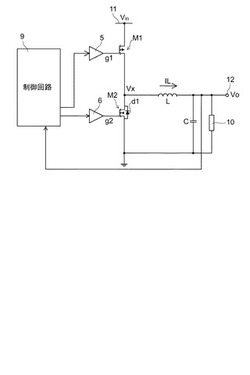

【解決手段】実施形態によれば、半導体装置は、入力電圧ラインと誘導性負荷との間に接続される第1のスイッチング素子と、誘導性負荷と基準電圧ラインとの間に並列接続される第2のスイッチング素子とを備えている。0<(第2のスイッチング素子の閾値電圧)<(第2のスイッチング素子の内蔵ダイオードのオン電圧)である。第2のスイッチング素子のゲート電圧が基準電位の場合に、第1のスイッチング素子と第2のスイッチング素子との接続点の電位が、−(第2のスイッチング素子の閾値電圧)より大きくなると第2のスイッチング素子はオフし、接続点の電位が、−(第2のスイッチング素子の閾値電圧)より小さくなると第2のスイッチング素子はオンする。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置のESD耐量を向上する。

【解決手段】半導体集積回路装置70には、電源回路1、内部回路2、電流源3、2入力NAND回路4、コンデンサC1、ダイオードD1、出力トランジスタMDT1、端子Pin、端子Pvcc、端子Pvo、及び端子Pvssが設けられる。電流源3、コンデンサC1、及び2入力NAND回路4は、端子PVoに(+)ESDが印加されたとき、2入力NAND回路4の出力側のノードN3の信号レベルを“High”レベルにして、出力トランジスタMDT1をオンさせてESDの電荷を低電位側電源Vss側に逃がす。

(もっと読む)

電子回路装置、回路システム、集積回路装置および電子機器

【課題】 汎用性が高く、回路システムが誤動作してしまうことを確実に抑制することができる電子回路装置、この電子回路装置を用いた回路システム、集積回路装置および電子機器を提供する。

【解決手段】 処理回路装置59と、電圧検知回路51とは、異なる電源供給線路に接続されて、各電源供給線路からそれぞれ電力が供給されて動作する。第2の電源供給線路66は、バッテリ63に接続および切断可能に設けられているが、第1の電源供給線路62は、バッテリ63に常時接続されている。電圧検知回路51は、第2の電源供給線路66がバッテリ63に接続されている状態から、バッテリ63から切断された状態に遷移したときに、ハイレベルおよびローベルの信号のうち、ローレベルの信号を出力する。これによって、処理回路装置59に保護ダイオード93が接続されていても、第2の電源供給線路66に電圧検知回路51から電流が流れ込んでしまうことが抑制される。

(もっと読む)

半導体装置

【課題】スクリーニング処が正常に完了したか否かを確認可能な半導体装置を提供する。

【解決手段】マイコンチップ4が、スクリーニング電圧発生開始制御信号とスクリーニング電圧発生開始制御信号がそれぞれ入力されたタイミングを利用してスクリーニングが開始されてから終了するまでの時間を計測し、計測された時間情報をスクリーニング時間としてメモリ12内に記憶する。これにより、スクリーニング完了後にメモリ12内に記憶されているスクリーニング時間を読み出し、読み出されたスクリーニング時間が所定時間であるか否かを判別することにより、スクリーニングが正常に完了したか否かを判別できるので、半導体製造業者又は半導体装置の利用者は半導体装置の初期不良品である確率の高いものを容易に発見できる。

(もっと読む)

半導体集積回路

【課題】本発明は、降圧電圧生成回路におけるパワーダウン時における電流消費を削減することを具体的な目的とする。

【解決手段】半導体集積回路は、所定の電圧を生成する電圧生成回路と、電圧生成回路が出力する所定の電圧をゲート端に受け取り、外部電源電圧をドレイン端に受け取り、外部電源電圧を所定の電圧に応じて降圧してソース端に降圧電圧を生成するNMOSトランジスタと、NMOSトランジスタのドレイン端と外部電源電圧との間に設けられパワーダウンモードを指示するパワーダウン信号をゲート端に受け取るPMOSトランジスタを含むことを特徴とする。

(もっと読む)

半導体装置

【課題】任意の安定な電源電位を容易に生成することが可能なRFID等の半導体装置を提供する。

【解決手段】半導体装置を構成する回路を任意の安定な電源電位が必要か否かによって分類する。任意の安定な電源電位が必要な回路には、レギュレータを介してアンテナより受信した無線信号からアンテナ及び整流回路を用いて生成された電源電位を供給する。一方、任意の安定な電源電位が必要な回路以外の回路には整流回路で生成した電源電位を供給する。よって、レイアウト面積が小さい、設計が容易なレギュレータ回路を有する半導体装置を提供することができ、当該半導体装置は任意の安定な電源電位を容易に生成することが可能となる。

(もっと読む)

半導体装置

【課題】出力トランジスタのオン抵抗を小さくして定電圧回路における入出力電圧差を小さくすることができ、しきい値電圧の小さいトランジスタを使用したりリプル除去率等の特性を劣化させることなく、小型で高速応答が可能な定電圧回路を有する半導体装置を得る。

【解決手段】誤差増幅回路12の出力端からは、入力電圧Viから、負電圧発生回路3から供給された負電圧Vssまで変化する電圧が出力され、入力電圧Viと負電圧Vssとの電圧差を出力トランジスタM1のゲート−ソース間電圧の絶対最大定格値よりも少し小さい電圧になるように設定することにより、出力トランジスタM1を破壊することなく、しかもオン抵抗が最小近くになるように出力トランジスタM1を駆動するようにした。

(もっと読む)

電子基板、半導体装置および電子機器

【課題】伝送効率の低下を防止することが可能な電子基板1を提供する。

【解決手段】基体10の能動面側に、相互にインダクタンス値または適用可能周波数のる第1インダクタ素子80および第2インダクタ素子40が形成されている。また基体10の能動面側にも、相互にインダクタンス値または適用可能周波数の異なる第1インダクタ素子85および第2インダクタ素子45が形成されている。第1インダクタ素子80,85は外部との電力伝送に使用され、第2インダクタ素子40,45は外部との通信に使用される。この電子基板1を積層すれば、電磁シールド性を有する基体10を介して電磁波を送受信する必要がなく、伝送効率の低下を防止することができる。

(もっと読む)

集積回路装置

【課題】 集積回路装置が静電気雑音により誤って初期化されるのを効果的に防止する。

【解決手段】 集積回路装置である制御用LSI100において、入出力回路用電源電圧発生回路130は、コア回路110用の電源電圧VDD1から入出力回路120用の電源電圧VDD2を発生する。パワーオン時、電源電圧VDD2は電源電圧VDD1より遅れて立ち上がり、これによりリセット信号発生回路140は、リセット信号RES2をコア回路110の制御回路112に供給する。その後は、マイクロコンピュータ200からのリセットコマンドのみにより制御回路112の初期化が行われる。

(もっと読む)

半導体装置

【課題】 抵抗素子の形成された絶縁膜に加わる電界を緩和し、前記絶縁膜の破壊を防止する。

【解決手段】 スイッチングレギュレータの高電圧部を含む半導体装置であり、メインスイッチ用FET及び前記メインスイッチ用FETのスタータースイッチ用FETの周辺を複数のフィールド・リミッティング・リングで多重に囲み、前記フィールド・リミッティング・リング上にフィールド絶縁膜を形成し、前記フィールド絶縁膜上に、前記FETのゲートと同層で、かつ前記スタータースイッチ用FETのドレイン及びゲートと電気的に接続された抵抗素子と、前記抵抗素子を被う層間絶縁膜と、前記層間絶縁膜上に形成され、前記FETのゲートおよびソースとそれぞれ電気的に接続される複数の配線と、前記半導体基板の裏面に形成され、前記メインスイッチ用FETおよびスタータースイッチ用FETのドレインと電気的に接続される裏面電極を含む半導体装置。

(もっと読む)

半導体装置、半導体装置の検査方法及び無線チップの検査方法

【課題】無線によりテストプログラムを受信する半導体装置の検査方法を提供する。

【解決手段】半導体装置の検査方法として、テストプログラムを通信信号として、テスト毎に送信する。動作テスト時に、テストプログラムを通信信号として、無線により送信することで、テスト内容を必要に応じて変化させる。これにより、テストプログラムの変更が容易になり、且つ、検査回路等が不要となる。このようにして無線チップ生産時の製造コストを削減することができる。

(もっと読む)

半導体装置

【課題】内部回路が受けるノイズの影響を小さくすることができる半導体装置を提供することである。

【解決手段】

DC−DCコンバータ401は、第1の内部電位を内部電源配線505に供給し、微小電流用DC−DCコンバータ501は、第2の内部電位を、ノイズの影響を受ける安定回路23と接続された内部電源配線505に供給する。スイッチ503は、内部電源配線505および507の一方を内部回路21と接続する。スイッチ503は、半導体装置の状態に応じて、内部回路21と、内部電源配線505または507との接続を制御する。

(もっと読む)

DC−DCコンバータのラッチアップ防止回路

【課題】ラッチアップを防止できるDC−DCコンバータのラッチアップ防止回路を提供すること。

【解決手段】入力電圧Vinが印加されて正電圧及び負電圧をそれぞれ生成する第1及び第2DC−DCコンバータ(111、112)が1つのチップ内で互いに結合され、1つのPNPトランジスタ及び1つのNPNトランジスタから構成されるラッチアップ発生部を備えたDC−DCコンバータにおいて、正電圧が生成される時点で、PNPトランジスタがターンオンされ、NPNトランジスタがターンオンしない範囲の電流が第1DC−DCコンバータ(111)に流入するように、入力電流の大きさを制限する第1経路部(121)と、正電圧及び負電圧がそれぞれ目標の電圧値まで達した時点で、入力電流を第1DC−DCコンバータ(111)にそのまま流入させる第2経路部(122)とを備える。

(もっと読む)

半導体装置、設計装置、レイアウト設計方法、プログラム及び記録媒体

【課題】 本発明は、チップ面積を縮小した半導体装置、及びチップ面積を縮小することが出来る設計装置、レイアウト設計方法、プログラム及び記録媒体を提供することを課題とする。

【解決手段】 レギュレータの配置位置を決定する際に、電源線に要する面積を縮小されるよう原電端子近傍でハードマクロへの電源線が短くなる配置位置候補を求め、各配置位置候補での面積を求め、最も小さくなる位置にレギュレータを配置する。またレギュレータを複数に分割して配置した場合の面積を求め、最も小さくなる位置にレギュレータを配置する。これにより、電源線に要する面積が少なくなり、その分チップ面積を小さくすることが出来る。

(もっと読む)

1 - 14 / 14

[ Back to top ]