Fターム[5F038BH07]の内容

Fターム[5F038BH07]に分類される特許

1 - 20 / 976

半導体集積回路

ESD保護回路およびこれを備えた半導体装置

ESD保護回路

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

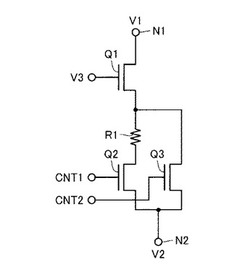

【課題】性能のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された第1のスイッチング素子(高耐圧のトランジスタQ1)および第2のスイッチング素子(抵抗素子R1および低耐圧のトランジスタQ2)と、第2のスイッチング素子に並列接続された第3のスイッチング素子(低耐圧のトランジスタQ3)とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、オン抵抗値の高い第1のスイッチング素子をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

半導体集積回路装置

【課題】突入電流を抑制できるとともに、チップ面積の増大を抑制することのできる半導体集積回路装置を提供する。

【解決手段】本実施形態の半導体集積回路装置は、ソースが入力電源線に接続され、ドレインが出力電源線に接続され、ゲートが第1制御線に接続された少なくとも1つの第1トランジスタと、ソースが前記入力電源線に接続され、ドレインが前記出力電源線に接続され、ゲートが第2制御線に接続された少なくとも1つの第2トランジスタと、前記第1制御線を駆動する第1バッファと、前記第1制御線を介して入力される制御信号を受け、前記第2制御線を駆動する第2バッファと、前記第1制御線を複数個に分割しかつこれらの分割された第1制御線間を接続するように設けられた複数のトランスファゲートと、を備えている。

(もっと読む)

集積回路

【課題】静電破壊に対する耐性を向上させることが可能な集積回路を提供する。

【解決手段】バイアス回路4は、増幅トランジスタM1が増幅を行えるようにバイアス電圧BA1を設定し、静電保護回路2は、増幅トランジスタM1にかかる電圧に基づいて、増幅トランジスタM1がオフするように増幅トランジスタM1のバイアス電圧BA1を設定し、切替回路3は、電源の供給状態に基づいて、増幅トランジスタM1のバイアス電圧BA1を切り替える。

(もっと読む)

ESD耐量検証方法及びESD耐量検証装置

【課題】 ESD耐量の低いパス及びその原因素子を安易且つ良好に特定できる検証方法及び検証装置を提供する。

【解決手段】 設計用回路データから2つの検証対象端子とその間に接続される検証対象素子を特定し、電流方向を設定し、検証対象素子の夫々を識別情報、電流方向別の特性情報及び耐量情報を記憶した素子シンボル情報を備える素子シンボルで表した等価回路データを作成し、2ノード間の特性情報及び耐量情報を記憶可能な分岐点シンボルを用い、検証対象端子に対応する分岐点シンボルを頂点とし、等価回路データをツリー構造データに変換し、素子シンボル情報に基づいて分岐点シンボル情報を作成し、頂点の分岐点シンボルの耐量情報が基準耐量以下の場合に、耐量情報に基づいて耐性が最も低い最低耐量経路と耐量制限シンボルを特定し、当該耐量制限シンボルに対応する設計用回路データの素子を特定する。

(もっと読む)

半導体装置

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】複数の出力トランジスタが並列接続された構成を備え、出力トランジスタを含む各電流経路間で分担電流を高精度に均一に揃えることができる半導体装置、および当該半導体装置の駆動方法を提供する。

【解決手段】互いに並列に接続された複数の出力トランジスタを備える半導体装置であって、出力トランジスタごとに設けられ第1の制御信号を供給する駆動回路と、第1の制御信号に含める出力トランジスタのコンダクタンスの情報を有するデータを記憶するメモリと、メモリにデータを入力するための第1の外部入力端子と、各駆動回路に出力トランジスタを1つずつ入れ替わり導通させる第2の制御信号を入力するための第2の外部入力端子とを備え、各駆動回路は、メモリに記憶されている駆動対象の出力トランジスタについてのデータを読み出して、コンダクタンスの情報を含む第1の制御信号を生成する。

(もっと読む)

半導体装置

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置に負電流が流れた場合でも、回路素子を構成する深い半導体層の電位に対して、半導体基板の電位が低くなるのを抑制して寄生素子を作動させず、半導体装置の誤動作を防止する。

【解決手段】本発明は、n型の半導体基板3と、半導体基板3の一面に形成し、接続する負荷に電力を供給する電力素子1と、n型のソース・ドレイン領域を有するMOSトランジスタ2cを少なくとも1つ含む回路素子2と、電力素子1および回路素子2に対し独立して配置したp型の半導体層4と、半導体基板3および半導体層4と接続する外部回路とを備えている。外部回路は、電源と、電源に一端を接続する抵抗素子と、抵抗素子の他端にアノード電極を接続し、カソード電極をGND接地するダイオードとを有し、抵抗素子の他端に半導体層4を接続する。

(もっと読む)

半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、入力電圧ラインと誘導性負荷との間に接続される第1のスイッチング素子と、誘導性負荷と基準電圧ラインとの間に並列接続される第2のスイッチング素子とを備えている。0<(第2のスイッチング素子の閾値電圧)<(第2のスイッチング素子の内蔵ダイオードのオン電圧)である。第2のスイッチング素子のゲート電圧が基準電位の場合に、第1のスイッチング素子と第2のスイッチング素子との接続点の電位が、−(第2のスイッチング素子の閾値電圧)より大きくなると第2のスイッチング素子はオフし、接続点の電位が、−(第2のスイッチング素子の閾値電圧)より小さくなると第2のスイッチング素子はオンする。

(もっと読む)

半導体回路

【課題】耐放射線特性の優れた半導体回路を提供することを目的とする。

【解決手段】複数のpMOSトランジスタ11,12を直列に接続した第1の回路ブロック1と、複数のnMOSトランジスタ21,22を直列に接続した第2の回路ブロック2とを備え、少なくとも1つの前記pMOSトランジスタ12のゲート及び/又は少なくとも1つの前記nMOSトランジスタ21のゲートを入力端子Vinに接続し、少なくとも1つの他のpMOSトランジスタ11のゲート及び/又は少なくとも1つの他のnMOSトランジスタ22のゲートに、オン電圧を印加する半導体回路。

(もっと読む)

静電気検出回路

【課題】本発明は、静電気検出回路を提供することを目的とする。

【解決手段】本発明の静電気検出回路は、電源線と接地線との間に直列に接続されているレジスター及びスイッチユニットを備え、前記電源線に静電気が存在する場合、前記スイッチユニットはオンされて、前記レジスターの両端に検出電圧が生じ、前記検出電圧は、静電気保護回路を動作させて静電気を除去するか、又は制御回路を動作させてデータを保存する。

(もっと読む)

保護回路、及び半導体装置

【課題】ESDの影響を効果的に抑制する保護回路を提供すること。またESDの影響が効果的に抑制された半導体装置を提供すること。

【解決手段】保護回路は、少なくとも2つの保護ダイオードを有し、当該保護ダイオードを、チャネルを形成する半導体層を挟んで対向する2つのゲートを有するトランジスタで構成する。さらに当該トランジスタのゲートの一方に、固定電位が入力される構成とすればよい。

(もっと読む)

半導体装置

【課題】静電気放電が印加されたときの熱破壊を抑制すること。

【解決手段】半導体装置1の半導体活性層16には、n型領域23とp型領域26とn型の埋込み領域30が形成されている。n型領域23は、カソード電極Kに電気的に接続している。p型領域26は、アノード電極Aに電気的に接続している。埋込み領域30は、半導体活性層16のうちのp型領域26の裏面側の少なくも一部を含むように形成されており、p型領域26の裏面に接触しているとともに、不純物濃度が半導体活性層16の不純物濃度よりも濃い。

(もっと読む)

安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路を備える半導体装置を提供する。

【解決手段】基板10と、基板上に配置され、ガン発振である高周波負性抵抗発振の発振周波数において負性抵抗を生ずる能動素子140と、基板上に配置され、能動素子のドレイン端子電極と出力端子との間に接続され、負性抵抗の絶対値に等しい抵抗値を有する抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とからなる安定化回路120とを備え、安定化回路120は、発振周波数に、インダクタンスLとキャパシタンスCからなる共振周波数を同調することによって、発振周波数において、抵抗Rによって負性抵抗をキャンセルする半導体装置。

(もっと読む)

半導体集積回路装置

【課題】過電流に対して内部回路を保護する半導体集積回路装置を提供することを目的としている。

【解決手段】多層配線構造を有する半導体集積回路装置であって、半導体集積回路装置の内部にある内部回路と半導体集積回路装置の外部にある外部回路とを接続するために半導体集積回路装置の内部に設けられたパッドパターンにおいて、第1の配線層と、第1の配線層が形成されている層とは別の層に形成されている第2の配線層と、第1の配線層と第2の配線層を接続するビアと、を備え、第2の配線層にヒューズパターンが形成されており、ヒューズパターンを経由して内部回路と外部回路とを電気的に接続する。

(もっと読む)

半導体装置

【課題】低消費電力化及び回路面積の削減を図れるようにした半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、電源端子と接地端子の間に接続されたMOSトランジスタと、MOSトランジスタのドレインとゲートの間に接続された第1のダイオードと、MOSトランジスタのドレインとゲートの間に第1のダイオードと互いの順方向が逆向きに直列に接続された第2のダイオードと、MOSトランジスタのドレインとゲートの間に第1及び第2のダイオードと直列に接続されたキャパシタとを備えている。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

1 - 20 / 976

[ Back to top ]