Fターム[5F038BH08]の内容

Fターム[5F038BH08]に分類される特許

1 - 20 / 22

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

電気回路中にて静電気放電保護素子として用いるためのゲート制御されたフィン型抵抗素子、および、電気回路内部を静電気放電から保護するための保護装置

【課題】電気回路中にて静電気放電保護を確実化しながら小型化を実現する。

【解決手段】電気回路において静電気放電保護素子として使用するためのゲート制御されたフィン型抵抗素子は、第1端子領域、第2端子領域、および、第1端子領域と第2端子領域との間に形成されたチャネル領域を有するフィン構造体を備えている。さらに、フィン型抵抗素子は、チャネル領域の上面の一部上に少なくとも形成されたゲート領域を備えている。ゲート領域は、ゲート制御部に電気的に結合されており、ゲート制御部は、ゲート領域に印加される電気的な電位を制御することにより、電気回路が第1動作状態である間は、ゲート制御されたフィン型抵抗素子の電気抵抗を高くし、静電気放電現象の開始によって特徴付けられている第2動作状態では、電気抵抗をより低くする。

(もっと読む)

電流量を制御するシステム

【課題】

電源が切れた状態のp形FETで、不所望の電流が流れるのを防ぐ。

【解決手段】

第1のデバイスのチャネルがp形であり、該第1のデバイスの第2の端子が電源に接続されており、第1のデバイスの基板に接続される第1の端子および第1のデバイスの第2の端子に接続される第2の端子を有するメカニズムを備え、電源がオフのとき、第1のデバイスの第1の端子および基板がpnダイオードを形成し、前記メカニズムの第1の端子および基板が、前記ダイオードに直列接続である少なくとも1つのダイオード要素を構成し、前記直列接続の閾値電圧が前記電流に関連する電圧を上回り、前記電流が流れるのを防ぐようにしたシステムを構成することにより、第1のデバイスの第1の端子から基板に電流が流れるのを制御する。

(もっと読む)

半導体装置

【課題】起動回路と周辺回路とを併せて集積化し得る半導体装置を提供する。

【解決手段】領域411においては、素子分離領域により規定されるドレイン領域121にボディ領域が形成され、ボディ領域にN型のソース領域が形成される。ドレイン領域121とN型のソース領域との間に第1のゲート電極20が配置される。素子分離領域は開口部133が形成されたループ状部と、開口部133を介してドレイン領域121に接続された延在領域122を規定する部分とを備える。延在領域122に、N型のソース引出領域が形成される。内部回路412においては、ドレイン領域121にP型のボディ領域が形成され、P型のボディ領域にN型のソース領域が形成され、ドレイン領域121とN型のソース領域との間に第2のゲート電極331が形成される。

(もっと読む)

接合型電界効果トランジスタ

【課題】 基板が低濃度の半導体基板のみからなるJ−FETは、静電破壊耐量は高いが、ノイズ電圧が大きく、ノイズ特性のばらつきも大きい問題があった。一方、ノイズ対策として、高濃度の半導体基板に低濃度の半導体層を積層した基板構造のJ−FETでは、ゲート抵抗の低減によりノイズ電圧を小さくできノイズ特性も安定する反面、静電破壊耐量が劣化する問題があった。

【解決手段】 高濃度半導体基板に低濃度の第1半導体層と、第1半導体層より高濃度の第2半導体層を積層する基板構造とする。これにより静電破壊耐量を劣化させない範囲でノイズ特性のばらつきを抑え、ノイズ電圧を小さくすることができる。また同時にノイズ特性に影響を与えない範囲で静電破壊耐量を向上させることができる。従って、従来構造と比較して市場要求に比較的柔軟に対応できるJ−FETを提供できる。

(もっと読む)

半導体装置、及び該半導体装置を用いたエネルギー伝達装置

【課題】ドレイン電極をソース電極に対して負バイアスすることがあっても、半導体集積回路においてラッチアップが発生することを防止できるエネルギー伝達装置、及び該エネルギー伝達装置を実現可能な半導体装置を提供する。

【解決手段】第1の半導体基板に形成された半導体装置24と、第2の半導体基板の表面に形成された第2導電型の逆電流防止層、及び第2の半導体基板中に形成され逆電流防止層を覆う第1導電型のウェル層を含む逆電流防止ダイオード41を備えた半導体集積回路48と、直流電圧源52と、変圧器60とを備え、変圧器60は、半導体装置24及び直流電圧源52と直列に接続される一次巻線53と、負荷と接続される第1二次巻線54とを含み、変圧器60の第1二次巻線54から負荷へ電力が供給されるように構成されている。半導体装置24の第2ドレイン電極(TAP電極)は、半導体集積回路48の逆電流防止層と電気的に接続している。

(もっと読む)

静電保護回路、静電保護素子および半導体装置

【課題】サージ電圧によって自身が破壊されるのを防止した静電保護回路を提供する。

【解決手段】pMOSトランジスタ20のゲート電極25が、接合ゲート型電界効果トランジスタ30のソース電極、ソース電位取出領域34、チャネル領域32、ドレイン電位取出領域35およびドレイン電極を介して参照電位線路L4に電気的に接続されている。pMOSトランジスタ20のソース電極とボディ電極とがそれぞれ信号線路L1に電気的に接続されている。これにより、信号線路L1にサージ電圧が印加され、サージ電圧がボディ領域21とソース領域22とに伝わり、ボディ領域21とソース領域22とがサージ電圧となった場合には、ボディ領域21のうちゲート電極25直下の部分にp型チャネル(図示せず)が形成され、ソース領域22のサージ電圧がp型チャネルを介してドレイン領域23に伝わり、参照電位線路L4へ放電される。

(もっと読む)

過電流および過電圧の保護装置を含む可変速駆動装置

【課題】損傷を伴わずに、配電網の擾乱を吸収できる可変速駆動装置を提供することを可能にする。

【解決手段】本発明の可変速駆動装置は、入力側において、電源網Aから得られる交流電圧から、直流電圧を電力バス10、11で発生させるための整流モジュール12と、前記電力バスのプラス線とマイナス線間に接続されたバスコンデンサCbと、前記電力バスから電力が供給され、電気負荷2に交流電圧を供給するように制御されるインバータモジュール13と、JFETトランジスタタイプの第一電子スイッチT1および電力バス上にJFETトランジスタT1と並列に設けられた第二電子スイッチT2から構成された可変速駆動装置の保護装置14と、を備えている。

(もっと読む)

半導体装置

【課題】過電流保護機能と過熱保護機能を兼ね備えた半導体装置において、メインデバイスの過電流と過熱を感度良く検出し、制御回路チップとメインデバイスチップとの間の接続を削減する。

【解決手段】パワー半導体素子(IGBT)を備えた半導体装置101において、パワー半導体素子と同一基板上に形成したパワー半導体素子に流れる電流を検出するための電流検出抵抗(センス抵抗)RSと、パワー半導体素子の過熱を検出するための電流をセンス抵抗RSに印加する過熱検出用電流生成回路105と、センス抵抗RSに生ずる電圧に対応して過電流または過熱を検出する異常検出回路106と、異常検出回路106の出力信号を入力してパワー半導体素子を駆動制御するドライブ制御回路104とを備えることで、制御回路チップ103とメインデバイスチップ102との間の接続を削減できる。

(もっと読む)

炭化ケイ素静電誘導トランジスタの制御装置及び制御方法

【課題】電力用変換器の過電流においてオン抵抗損失の著しい増大を抑制して、電力用変換器の小型・軽量化および低価格化をはかる。

【解決手段】定格電流容量の5倍ないし20倍のサージ電流が流れる電力用変換器に炭化ケイ素を素材とした静電誘導トランジスタを適用するにあたり、該静電誘導トランジスタのオン時のゲート電圧を定格電流以下の正常動作時にはゲート接合のビルトイン電圧以下として高速、低損失、高効率の電力変換を行い、定格を超える過電流が流れた場合にかぎりゲート電圧をビルトイン電圧以上に昇圧することにより過電流による素子破壊を防止する制御方法によって変換器に使用される炭化ケイ素静電誘導トランジスタの電流容量を変換のそれを大幅に超えない小容量とする。

(もっと読む)

保護素子

【課題】立ち上りが急峻で高電圧のESDやサージが印加された場合であっても、従来に較べてサージ電流のIC回路へ流れ込みをより抑制することのできる保護素子を提供する。

【解決手段】IC回路への入力ラインに挿入され、IC回路をサージから保護するための保護素子であって、グランドラインと入力ライン間で逆方向接続されるツェナーダイオード10と、PN接合構造からなり、入力ラインに挿入されるピンチ抵抗体20とを有してなり、ツェナーダイオード10の耐圧が、ピンチ抵抗体20の耐圧より低く設定され、ピンチ抵抗体20が、入力ラインにおけるIC回路とツェナーダイオード10の間に配置されて、ピンチ抵抗体20の制御電極Sが、入力ラインのIC回路側またはグランドラインに接続されてなる保護素子100とする。

(もっと読む)

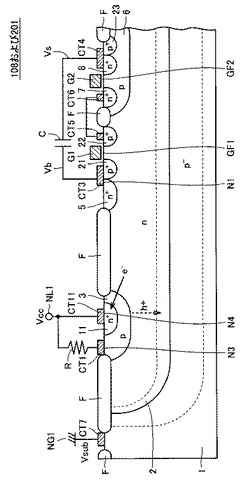

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置であって、半導体装置は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN2とを有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電位ノードNL1に結合される第3ノードN3を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第3ノードN3から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

半導体装置、半導体集積回路、スイッチング電源用制御ICおよびスイッチング電源装置

【課題】高耐圧高抵抗素子を有するスイッチング電源装置の部品コストや組み立てコストの低減と、小型化を図ること。

【解決手段】拡散層を用いた耐圧構造の上に抵抗体を配置して高耐圧高抵抗素子を実現する。または、ゲート領域102、ソース領域104、ドレイン領域105およびドリフト領域103上の層間絶縁膜に、渦巻き状の高耐圧高抵抗素子121を埋め込む。高耐圧高抵抗素子121の一端をドレイン電極配線110に接続し、他端を第1の抵抗接続配線122を介して接地する。この抵抗素子121の中間点を第2の抵抗接続配線123を介して制御ICの電圧比較器に接続する。高耐圧高抵抗素子121において、ドレイン電極配線110との接続点から第2の抵抗接続配線123との接続点までの部分、および第2の抵抗接続配線123との接続点から第1の抵抗接続配線122との接続点までの部分が、それぞれ、1次側電圧が印加される側の抵抗、および接地される側の抵抗となる。

(もっと読む)

化合物半導体素子および回路のための静電放電保護回路

静電放電保護回路を化合物半導体素子および回路に提供するための装置および方法が開示される。静電放電保護回路は、第1の端子および第2の端子を備える。静電放電保護回路は、第1の端子と第2の端子との間に動作可能に連結されたトランジスタ分路要素であって、第1の端子と第2の端子との間に双方向性の放電経路を提供することができるトランジスタ分路要素をさらに備える。静電放電保護回路は、第2の端子に動作可能に連結された遮断要素であって、トランジスタ分路要素をターンオフの状態に維持することができる遮断要素をさらに備える。  (もっと読む)

(もっと読む)

半導体装置

【課題】高電圧が印加されている時の電力損失を低減した電圧検出回路を備えた半導体装置を提供することにある。

【解決手段】入力電圧Vinを入力する入力端子11と、検出電圧Vdを出力する出力端子12との間に電流制限素子(JFET素子)13が接続され、電流制限素子13は、半導体基板21中に形成されたPN接合を有する拡散層22、23で構成され、かつ、拡散層の入力端子11側の一端に印加される電圧が規定電圧以上になると、PN接合の空乏化により拡散層を流れる電流が制限される特性を有している。検出電圧Vdは、規定電圧以下になるように設定され、入力電圧Vinが上昇し、検出電圧Vdが基準電圧Vrを越えた後は、入力電圧Vinの上昇に伴う電力損失が抑制される。

(もっと読む)

半導体装置

【課題】マイクロホン等に使用されるMOSFETを備える半導体装置において、ドレイン電流の過渡特性の改善と、MOSFETのS/Nの改善の双方を、同時に実現する。

【解決手段】主たるMOSFET(100)のゲート・ソース間に、可変インピーダンス素子としてのMOSFET(210)を接続する。ドレイン電圧印可直後の過渡期には、MOSFET(210)のチャネルインピーダンスが低く、過渡的なドレイン電流を速やかに吸収することができる。一方、ドレイン電流が定常状態となった後は、MOSFET(210)のチャネルインピーダンスが高インピーダンス化し、信号成分のリーク(と無駄な放電)が低減され、低ノイズ化が達成される。

(もっと読む)

高耐圧縦型MOSトランジスタ及び高耐圧縦型MOSトランジスタを用いたスイッチング電源装置

【課題】 電圧制御回路へ電力を供給するための高耐圧で高電力型の抵抗を用いずに、交流電源の投入時に必要な起動用のバイアス電圧を供給することを目的とする。

【解決手段】 第1の導電型の半導体基板10を介して第1の導電型のドリフト領域20と接続する第1のドレイン領域110と第2の導電型の半導体領域に挟まれた第1の導電型のドリフト領域20に形成された第2のドレイン領域331とを備える高耐圧接合型FET284を介して高耐圧縦型MOSトランジスタと電圧制御回路とを接続することにより、高耐圧縦型MOSトランジスタから電圧制御回路に印加される電圧を高耐圧接合型FET284のピンチオフ電圧以下に制御することができるため、電圧制御回路へ電力を供給するための高耐圧で高電力型の抵抗を用いずに、交流電源の投入時に必要な起動用のバイアス電圧を供給することができる。

(もっと読む)

電気回路中にて静電気放電保護素子として用いるためのゲート制御されたフィン型抵抗素子、および、電気回路内部を静電気放電から保護するための保護装置

【課題】電気回路中にて静電気放電保護を確実化しながら小型化を実現する。

【解決手段】電気回路において静電気放電保護素子として使用するためのゲート制御されたフィン型抵抗素子は、第1端子領域、第2端子領域、および、第1端子領域と第2端子領域との間に形成されたチャネル領域を有するフィン構造体を備えている。さらに、フィン型抵抗素子は、チャネル領域の上面の一部上に少なくとも形成されたゲート領域を備えている。ゲート領域は、ゲート制御部に電気的に結合されており、ゲート制御部は、ゲート領域に印加される電気的な電位を制御することにより、電気回路が第1動作状態である間は、ゲート制御されたフィン型抵抗素子の電気抵抗を高くし、静電気放電現象の開始によって特徴付けられている第2動作状態では、電気抵抗をより低くする。

(もっと読む)

太陽電池モジュール用の保護回路装置

【課題】本発明は、通常動作で動作するものと陰になった場合に動作するものとを含む、複数の太陽電池を直列に接続した太陽電池モジュール用の回路遮断器に関する。

【解決手段】少なくとも1つの制御された電気スイッチ素子がバイパス素子として作用し、その電流路が複数の太陽電池に並列に接続する。供給回路は、バイパス素子の制御電極を制御する制御電圧を提供する。通常動作時には遮断回路がバイパス素子の接点ギャップに加えられる電圧をブロックし、少なくとも1つの太陽電池が陰になった場合には、接点ギャップに加えられる電圧を供給回路に切り替える。

(もっと読む)

半導体装置および入力保護回路

【課題】静電気等の高電圧による破壊からMOSFETを保護する、SOI構造を有する入力保護回路を提供する。

【解決手段】シリコン基板1の上に形成された埋込酸化膜2と、該埋込酸化膜の上に、シリコン層に不純物が注入されて形成されたp+拡散層10と、このp+拡散層10とPN接合によって接続されるn+ポリシリコン層8と、n+ポリシリコン層8に接続され、かつその一方端が入力パッドに接続され、その他方端が内部回路に接続された配線4と、n+ポリシリコン層8と離されて設けられ、かつp+拡散層10に接続されるように設けられた配線14とを備える。

(もっと読む)

1 - 20 / 22

[ Back to top ]