Fターム[5F038BH10]の内容

Fターム[5F038BH10]に分類される特許

161 - 180 / 400

クロストーク防止回路

【課題】 微細化、集積度向上に影響を与えない方法で、クロストークを減少または除去する回路を提供する。

【解決手段】 クロストーク防止回路は、ほぼ平行して形成されている少なくとも2本の信号線、たとえば、マスタスロック用線とスレーブクロック用線l1,l2の間に、これら2本の信号線の少なくとも一方に印加される信号が存在しないとき、たとえば、テスト用信号が印加され、前記2本の信号線に信号が印加されるとき接地状態になる第3の信号線l3を生成する。好ましくは、第3の信号線にドライバ回路を接続し、該ドライバ回路の出力トランジスタのNチャネルトランジスタとPチャネルトランジスタの電流駆動能力の比率をほぼ2:1にする。

(もっと読む)

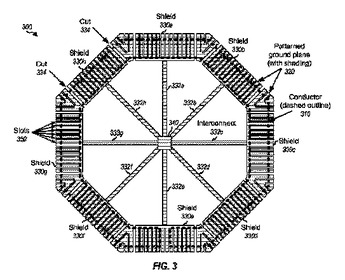

パターン化された接地平面を有するインダクタ

パターン化された接地平面を有するインダクタが、説明される。一設計においては、インダクタは、第1の層上に形成された導体と、その導体の下の第2の層上に形成されたパターン化された接地平面と、を含む。パターン化された接地平面は、オープンな中心エリアと、導体の形状に整合した形状と、を有する。パターン化された接地平面は、複数のシールド、例えば、八角形の形状の導体の8つの辺についての8つのシールド、を含んでいる。各シールドは、導体に垂直に形成された複数のスロットを有する。パターン化された接地平面を別個のシールドへと分割することと、各シールド上にスロットを形成することとは、パターン化された接地平面上の渦電流の流れを防止するのに役立ち、これは、インダクタのQを改善することができる。複数の相互接続は、複数のシールドを回路接地へと結合し、この回路接地は、導体の中心に位置することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】プラズマプロセスによるゲート絶縁膜へのプラズマチャージを緩和させることができる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、基板上にゲート絶縁膜4及びゲート電極5を順に形成し、第1の層間絶縁膜8を形成後、コンタクトホール11a、11b及び11cと溝11を形成し、そこにWプラグ9a、9b、9c及び9を埋め込み、Al配線10a、10b及び10cを形成し、ゲート電極及び保護ダイオードを囲むAlシールド用配線10を形成し、第2の層間絶縁膜12を形成し、viaホール15及び15aを形成し、Wプラグ13及び13aを埋め込み、Al配線14を形成する工程を具備し、Wプラグ13とWプラグ13aは第3の配線14によって電気的に接続されていることを特徴とする。

(もっと読む)

半導体装置

【課題】高圧側浮遊オフセット電圧VSの負変動に起因する誤動作及びラッチアップ破壊を回避し得る半導体装置を得る。

【解決手段】NMOS14とPMOS15との間において、n型不純物領域28の上面内には、p型ウェル29に接するようにp+型不純物領域33が形成されている。p+型不純物領域33上には電極41が形成されており、電極41は高圧側浮遊オフセット電圧VSに接続されている。p+型不純物領域33の不純物濃度はp型ウェル29の不純物濃度よりも高く、また、p+型不純物領域33はp型ウェル29よりも浅く形成されている。p+型不純物領域33とPMOS15との間において、n型不純物領域28の上面内には、n+型不純物領域32が形成されている。n+型不純物領域32上には電極40が形成されており、電極40は高圧側浮遊供給絶対電圧VBに接続されている。

(もっと読む)

半導体装置

【課題】信号配線を高密度に配置しつつ、ノイズの影響を確実に抑えるシールド構造を小さい面積で実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置10は、拡散層12が形成される半導体基板11の上部に少なくとも2層の配線層M2、M3が積層され、所定電位を保持する信号を伝送するために2層の配線層M2、M3に形成された信号配線20、30と、信号配線20,30を遮蔽するために一定の電位に固定され2層の配線層M2、M3に信号配線20、30と隣接して形成されたシールド配線21、31と、半導体基板11の上部に絶縁膜を挟んで形成されるゲート電極13とを備え、下層の配線層M2に形成された信号配線20が、積層方向に対向するゲート電極13と電気的に接続されている。

(もっと読む)

半導体装置

【課題】抵抗値が大きく、また、磁力線が回路に悪影響を及ぼすおそれがあった。

【解決手段】(1)(1a)渦巻状の巻線本体と、(1b)前記巻線本体の両端部のうち中心側の端部の近傍を起点として外側に向けて延在する配線と、(1c)前記巻線本体の前記中心側の端部と前記配線の中心側の端部とを斜めに接続するビアと、を有するインダクタと、(2)前記巻線本体により規定される仮想平面と平行に、かつ、前記巻線本体の下方に設けられている、複数の遮蔽板片からなる遮蔽板と、を含む。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】半導体基板1上に、配線M1〜M5の櫛型形状の金属パターンで電極を形成したMIM型の容量素子が形成される。容量素子の下方には、CMP工程のディッシング防止のためのダミーのゲートパターンである導体パターン8bと、ダミーの活性領域である活性領域1bとが配置され、これらは配線M1〜M5からなるシールド用の金属パターンに接続されて固定電位に接続されている。そして、導体パターン8bおよび活性領域1bは、配線M1〜M5の櫛型形状の金属パターンと平面的に重ならないように配置される。

(もっと読む)

クロック配線構造、半導体装置、及び半導体装置の製造方法

【課題】配線形状のばらつきを効果的に抑制することのできる配線構造、半導体装置、及び半導体装置の製造方法を提供すること

【解決手段】本発明にかかる配線構造は、クロック配線11と、クロック配線11と同層において、クロック配線11に沿ってその両側に設けられた一対の第1シールド配線12と、クロック配線11と絶縁層を介した異なる層において、クロック配線11及び一対の第1シールド配線12の対向する領域を覆うように設けられた第2シールド配線13と、一対の電極(上部電極17、下部電極18)が絶縁層を介して対向配置されたMIM容量30と、を備え、MIM容量30の一対の電極のうち少なくとも一方が、第2シールド配線13と同層に設けられているものである。

(もっと読む)

サンプルホールド回路、集積回路装置、電気光学装置及び電子機器

【課題】回路の大規模化を抑えながら適正なサンプルホールド動作を実現できるサンプルホールド回路、集積回路装置、電気光学装置及び電子機器の提供。

【解決手段】サンプルホールド回路は、演算増幅器と、サンプルホールド回路の入力ノードと演算増幅器の第1の入力端子のノードであるサミングノードとの間に設けられたサンプリング用キャパシタと、演算増幅器の出力端子とサミングノードとの間に設けられ、トランスファーゲートにより構成される帰還用スイッチ素子を含む。帰還用スイッチ素子は、サミングノードラインLNEGがそのドレインに電気的に接続される帰還用P型トランジスタTFPと帰還用N型トランジスタTFNを含む。帰還用P型トランジスタTFP、帰還用N型トランジスタTFNのドレインコンタクトCDP、CDNとソースコンタクトCSP、CSNとの間の領域に、シールドパターンSLA1が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、異なる種類の複数のヒューズを積層した構成や、当該構成に対する具体的な救済及び半導体装置の識別付与の製造方法を提供することを目的とする。

【解決手段】

本発明の1つの実施形態では、所定の電圧値を印加、又は所定の電流値以上を流すことで切断される第1ヒューズと、レーザ光を照射することで切断される第2ヒューズと、レーザ光を反射するリフレクタ層とを備える半導体装置である、さらに、本発明の1つの実施形態に係る半導体装置では、第1ヒューズ上に絶縁層を介してリフレクタ層を積層し、リフレクタ層上に絶縁層を介して第2ヒューズを積層する。

(もっと読む)

半導体集積回路

【課題】遅延時間を調整するために信号用回路を変更した場合に外部配線によって遅延時間が変化させられることを回避することが可能な半導体集積回路を提供すること。

【解決手段】この半導体集積回路は、信号用回路10Bを含む。信号用回路10Bは、入力端子INから入力信号が入力されることにより、その入力信号に応じた出力信号を出力端子OUTから出力する。信号用回路10Bは、入力信号に対して出力信号が遅延している時間である遅延時間を調整するために変更される調整用変更部AJ1〜AJ3を有する。半導体集積回路は、信号用回路10B以外の回路を構成する外部配線31,32と調整用変更部AJ1〜AJ3との間に配置されたシールド用導体12c,12dを備える。

(もっと読む)

半導体集積回路

【課題】面積が小さく、かつコストの低い半導体集積回路を提供する。

【解決手段】半導体基板1上に積層された複数の配線層と、2GHzの周波数帯域に対応して、複数の配線層のうちの1つの配線層に形成された2G用インダクタ4と、2GHzの周波数帯域よりも高い5GHzの周波数帯域に対応して、2G用インダクタ4が形成された配線層と同一の配線層に形成された5G用インダクタ5とを備え、5G用インダクタ5は、2G用インダクタ4の開口部の内側に形成されるものである。

(もっと読む)

インダクタ用シールドおよびシールド付きインダクタ

【課題】 占有面積が小さいけれども、インダクタ間の磁気的な結合を抑制してクロストークを抑制する効果に優れたインダクタ用シールドを提供する。

【解決手段】 3つの配線層の各々に半導体基板の上方から見てインダクタLの周りを略一周回するように形成された周回配線W1、W2、W3を有している。周回配線W1、W2、W3同士は、巻回方向が不変の一連のコイルを形成するようにビアによって直列に接続されている。このコイルの両端は、ビアAによって互いに接続されている。

(もっと読む)

半導体装置

【課題】複数の回路を搭載する場合において、回路間のノイズ伝播などの誤動作を抑制することが可能な半導体装置を提供すること。

【解決手段】支持基板と、前記支持基板上に設けられた絶縁層と、前記絶縁層上に設けられ第1回路を有する第1半導体層と、前記絶縁層上に設けられ、前記第1半導体層と絶縁され、第2回路を有する第2半導体層と、前記絶縁層上のうち前記第1半導体層と前記第2半導体層との間に設けられ、前記第1半導体層及び前記第2半導体層とそれぞれ絶縁された分離層と、前記分離層との間で静電容量を保持するように前記分離層の上層に設けられ、電気的に接地された容量層とを備える。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間に配置される絶縁膜(例えば、BOX)にて構成される寄生容量を充放電する変位電流が発生することを抑制し、回路の誤動作を防止する。

【解決手段】低電位基準回路部LVに形成されたシールド層3bをGND電位とし、高電位基準回路部HVに形成されたシールド層3bを仮想GND電位とする。これにより、変位電流が発生した場合には、高電位基準回路部HVの仮想GND配線17bから変位電流引抜き層19およびシールド層3bを通じて支持基板2に至ったのち、低電位基準回路部LVのシールド層3bおよび変位電流引抜き層19を通じてGND配線17aに流れる。したがって、変位電流が低電位基準回路部LVに備えられた各種回路に流れることを防止でき、回路が誤動作してしまうことを防止することが可能となる。

(もっと読む)

サンプルホールド回路、集積回路装置、電気光学装置及び電子機器

【課題】回路特性の悪化防止や回路の小規模化を図れるサンプルホールド回路等の提供。

【解決手段】サンプルホールド回路は演算増幅器OP1とサンプリング用スイッチ素子SSとサンプリング用キャパシタと帰還用スイッチ素子とフリップアラウンド用スイッチ素子SAを含む。サンプリング用スイッチ素子SSのオン・オフを制御するサンプリング用制御信号を供給ためのサンプリング用制御ラインLSP、LSNが、サミングノードラインLNEGの第3の方向D1において第2の方向D2に沿って配線され、フリップアラウンド用スイッチ素子SAのオン・オフを制御するフリップアラウンド用制御信号を供給するためのフリップアラウンド用制御ラインLAP、LANが、サミングノードラインLNEGの第1の方向D3において第2の方向D2に沿って配線される。

(もっと読む)

サンプルホールド回路、集積回路装置、電気光学装置及び電子機器

【課題】回路特性の悪化防止や回路の小規模化を図れるサンプルホールド回路等の提供。

【解決手段】サンプルホールド回路は演算増幅器OP1とサンプリング用スイッチ素子SSとサンプリング用キャパシタと帰還用スイッチ素子とフリップアラウンド用スイッチ素子SAを含む。演算増幅器OP1を構成するN型トランジスタは第1のP型ウェルPWL1に形成され、P型トランジスタは第1のN型ウェルNWL1に形成される。サンプリング用及びフリップアラウンド用スイッチ素子SS、SAを構成するN型トランジスタは第1のP型ウェルPWL1と分離された第2のP型ウェルPWL2に形成され、P型トランジスタは第1のN型ウェルNL1と分離された第2のN型ウェルNWL2に形成される。

(もっと読む)

サンプルホールド回路、集積回路装置、電気光学装置及び電子機器

【課題】回路特性の悪化防止と回路の小規模化を図れるサンプルホールド回路等の提供。

【解決手段】サンプルホールド回路は、演算増幅器(OP1)と、演算増幅器の第1の入力端子のノードであるサミングノード(NEG)にその一端が接続される第1のキャパシタ(C1)と、サミングノードにその一端が接続される第2のキャパシタ(C2)を含む。第1のキャパシタと第2のキャパシタは、演算増幅器の第2の方向(D2)において第1の方向(D1)に沿って配置され、サミングノードライン(LNEG)が、第1のキャパシタと第2のキャパシタの間の領域であるキャパシタ間領域において、第2の方向に沿って配線される。

(もっと読む)

半導体装置

【課題】 抵抗値変動が少なく安定的で出力電圧精度が高く、半導体製造工程に関わるプラズマチャージや熱・応力などの影響を抑制し、多結晶シリコン抵抗体からなる抵抗回路を提供する。

【解決手段】 抵抗回路を構成する多結晶シリコン抵抗体からなる複数の抵抗群のそれぞれの上に金属電極を形成し、その金属電極を、別の配線層を介して抵抗体の一端に接続する。そうすることで金属電極が受ける半導体プロセスの外的影響が直接抵抗体に作用することを防ぎ、抵抗値ばらつきを抑制する。

(もっと読む)

テラヘルツ波を検出するためのモノリシック集積アンテナおよび受信器回路

本発明は、ソース、ドレイン、ゲート、ゲート・ソース接点、ソース・ドレイン・チャネルおよびゲート・ドレイン接点を有する少なくとも1つの電界効果トランジスタを含む、ミリメートル波を検出するための装置に関する。簡素な装置と比べて、本発明によって対処する課題は、THz周波数範囲の電磁放射の電力および/または位相を検出するための電界効果トランジスタを提供することを可能にする装置を提供することである。そのような装置を得るために、本発明によれば、アンテナ構造体を有し、前記電界効果トランジスタは、前記アンテナ構造体によって受信された前記THz周波数範囲の電磁気信号が前記ゲート・ソース接点によって前記電界効果トランジスタに供給されるように、前記アンテナ構造体に接続され、前記電界効果トランジスタと前記アンテナ構造体が、単一基板上に配列される装置が提供される。 (もっと読む)

161 - 180 / 400

[ Back to top ]