Fターム[5F038BH10]の内容

Fターム[5F038BH10]に分類される特許

81 - 100 / 400

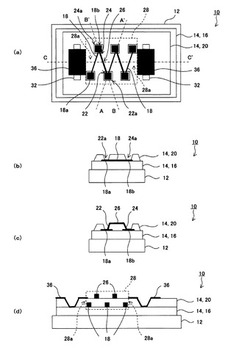

チップ一体型パッケージ、半導体装置

【課題】チップ一体型パッケージ、半導体装置を提供する。

【解決手段】半導体基板12上に積層した絶縁層14と、前記絶縁層14に横倒しに埋め

込んだ態様で形成され、前記半導体基板12に形成された回路または外部回路と電気的に

接続するソレノイド型のインダクタ28と、前記絶縁層14において前記インダクタ28

の両端の開口部28aを塞ぐ位置に埋め込んだ態様で形成した一対の磁性部材(磁性板3

5、磁性膜36、磁性樹脂38)と、を有することを特徴とする。

(もっと読む)

半導体装置および携帯機器

【課題】差動信号の伝送特性に優れ、かつ、簡易な構成の半導体装置を提供する。

【解決手段】半導体装置100、一対の差動伝送線路26を含む配線層12と、電位が固定された導電層であって、電気的に連続した導体によって形成された連続領域を有する導電層16と、半導体基板24と、半導体基板24と導電層16との間に設けられ、電気的に浮いている導体を有する阻止層20と、配線層12と導電層16と阻止層20と半導体基板24との間に設けられた絶縁層と、を備える。一対の差動伝送線路26は、積層方向から見て導電層16の導体と交差し、阻止層20は、導電層16の導体と交差する複数の間隙が形成されている。

(もっと読む)

半導体チップ用受動層、半導体装置

【課題】チップ一体型パッケージ、半導体装置を提供する。

【解決手段】半導体基板12上に積層した絶縁層14と、前記絶縁層14に横倒しに埋め

込んだ態様で形成され、前記半導体基板12に形成された回路または外部回路と電気的に

接続するソレノイド型のインダクタ28と、前記絶縁層14において前記インダクタ28

の両端の開口部28aを塞ぐ位置に埋め込んだ態様で形成した一対の金属部材(金属膜3

4、金属板35)と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】 入出力部の電源配線の近傍にバイパスコンデンサを配置する場合、LSIの端子数が多くなると、バイパスコンデンサを配置するための領域を確保することが困難になる。

【解決手段】 半導体基板の表面に、電子回路素子が形成されている電子回路領域が画定される。半導体基板の上に、一方に基準電位が印加され、他方に電源電圧が印加される第1及び第2の配線が配置される。シールリングが、電子回路領域を取り囲むように、半導体基板の上に配置される。シールリングは、第1の配線に電気的に接続される。第1の不純物拡散領域が、シールリングよりも内側において、半導体基板の表層部に形成される。第1の不純物拡散領域の上に誘電体膜が配置される。誘電体膜の上に、シールリングに電気的に接続され、導電材料で形成されたキャパシタ導電膜が配置される。

(もっと読む)

相互誘導回路

【課題】専有面積の小さいトランス素子を提供すること。

【解決手段】トランス素子1は、半導体基板上において上下方向に平行な第1及び第2の配線層を使って形成され、第1のインダクタンス2及び第2のインダクタンス3を備える。第1及び第2のインダクタンス2及び3は、鉛直上方向及び鉛直下方向の一方から第1の配線層及び第2の配線層の一方に投影した時に、投影された外形線が予め定められた基準面を基準として対称な形状を有し、かつ投影された外形線が第1の配線層及び第2の配線層の一方上で交差し合う部分については、第1の配線層及び第2の配線層を使って交差しないよう構成される。

(もっと読む)

集積回路装置及び電子機器

【課題】レイアウト面積の小面積化を図りながら表示制御用の信号を電気光学装置に供給できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置10は、集積回路装置10にスタックされる画像メモリー120のチップの第1のチップ辺SC1に沿って配置される第1のメモリーパッド群PMG1に接続される第1のパッド群PG1と、第3のチップ辺SC3に沿って配置される第2のメモリーパッド群PMG2に接続される第2のパッド群PG2と、電気光学装置の表示制御を行う制御部30と、表示制御用のデータ信号及び制御信号が出力される第3のパッド群PG3を含む。第1のパッド群PG1は、集積回路装置10の第1の辺SD1に沿って配置され、第2のパッド群PG2は、第1の辺SD1に対向する第3の辺SD3に沿って配置され、第3のパッド群PG3は、第1の辺SD1及び第3の辺SD3に交差する第2の辺SD2に沿って配置される。

(もっと読む)

半導体装置

【課題】ヒューズ用開口部からガードリング外への水分等の伝達をより強固に防止する。

【解決手段】下地絶縁膜3上に第1シリコン膜パターンからなるシリコンヒューズとシリコン配線パターン7が形成されている。第1シリコン膜パターンとは別途形成された第2シリコン膜パターンからなり、上方から見てヒューズ5の周囲を取り囲み、一部分がシリコン配線パターン7上を跨いで下地絶縁膜上に環状に形成されたシリコンガードリング11が形成されている。シリコンガードリング11と交差している部分のシリコン配線パターン7表面にシリコン表面絶縁膜9が形成されている。シリコン配線パターン7とシリコンガードリング11はシリコン表面絶縁膜9により互いに絶縁されている。シリコンガードリング11上に金属材料からなる環状のガードリング17,19,25,27が上方から見てヒューズ5の周囲を取り囲んで形成されている。

(もっと読む)

半導体装置

【課題】内部回路の状態を正確に判定することができる、半導体装置を提供すること。

【解決手段】半導体装置1は、基板11上に複数の絶縁層121A〜121Jからなる絶縁層群12が積層されるとともに、回路形成領域Aが形成されている。この半導体装置1は、複数の絶縁層121A〜121H中に形成され、前記回路形成領域Aを囲むように設けられた第一のシールリング13と、この第一のシールリング13の外側に設けられたビアチェーン14と、ビアチェーン14の外側に設けられるとともに、前記複数の絶縁層121A〜121J中に形成され、前記回路形成領域Aを囲むように設けられた第二のシールリング15とを備える。

(もっと読む)

半導体集積回路

【課題】機能マクロセルの周辺において、配線を形成するための領域を十分に確保する。

【解決手段】半導体集積回路100は、機能マクロセル110に形成される機能マクロセル用電源配線181と、機能マクロセル110の内部に形成される電源配線261と、機能マクロセル110の内部に形成され、機能マクロセル用電源配線181と電源配線261とを電気的に接続するコンタクト170と、コンタクト170と、論理セルとを電気的に接続する電源配線とを備える。機能マクロセル用電源配線181は、論理セル電圧を、コンタクト170および電源配線を介して、論理セルへ供給する。

(もっと読む)

半導体集積回路装置

【課題】面積の大幅な増大なくレファレンス電圧生成回路を低消費電流化するとともに通常動作モード時とスタンバイモード時においてレファレンス電圧精度の大幅な劣化を抑制する。

【解決手段】スタンバイモード時に、分周制御回路14は発振回路5が生成したクロックから、基準電圧発生回路3、基準電圧生成回路4、容量充電レギュレータ11のON/OFFを決めるイネーブル信号VREFONと基準電圧発生回路3、基準電圧生成回路4、ならびに容量充電レギュレータ11がONの際に、保持容量回路6内の保持容量CHに充電し、OFF期間に保持容量CHに対してリーク電流パス以外は存在しないように制御するサンプリング/ホールド信号CHOLDSWを生成する。消費電流の大きい基準電圧発生回路3、基準電圧生成回路4、容量充電レギュレータ11を間欠動作させて低消費電流化を図る。

(もっと読む)

半導体装置

【課題】デジタル領域とアナログ領域とが混載された半導体装置におけるデジタル領域からアナログ領域へのノイズ伝搬を効果的に抑制する。

【解決手段】デジタル領域120とアナログ領域130とが混載された半導体装置100は、平面視でデジタル領域120およびアナログ領域130の外周を取り囲む環状のシールリング140と、シールリング140で囲まれた領域内で、デジタル領域120とアナログ領域130との間に設けられ、アナログ領域130をデジタル領域120から隔離するとともに、シールリング140に電気的に接続されたガードリング150と、ガードリング150と当該ガードリング近傍で電気的に接続された電極パッド160aとを含む。電極パッド160aは、外部の接地端子(180a)に接続されて接地電位とされている。

(もっと読む)

半導体装置およびその製造方法

【課題】製造プロセス中に磁性体膜の材料の拡散を防止しながら、高い磁気シールド効果を有するヘテロ構造磁気シールドを備えた半導体装置を提供する。

【解決手段】半導体装置10は、半導体基板20、半導体基板20の主面上に形成され、かつ多層配線層11Bを含む半導体素子12、および半導体素子12を被覆するヘテロ構造磁気シールド170を含む。ヘテロ構造磁気シールド170は、第一の磁気シールド積層構造16Aと磁気シールド積層構造16Aを覆う第二の磁気シールド積層構造16Bを含む。第一および第二の磁気シールド積層構造16Aおよび16Bは、いずれも、半導体素子12を被覆する磁性体からなる磁気シールド膜および半導体素子12と磁気シールド膜との間に介在し磁性体の拡散を防止するバッファ膜とを有する。

(もっと読む)

アナログディジタル変換器

【課題】アナログディジタル変換器が半導体基板上で占める面積の低減する。また、アナログディジタル変換器の高精度化を図る。

【解決手段】半導体基板200上には、Pチャネルトランジスタ104aを有するアナログスイッチが形成されている。アナログスイッチの上層には、アナログスイッチに重なる領域に、櫛形電極401・402・501・502が形成され、キャパシタが構成されている。

(もっと読む)

半導体装置

【課題】スイッチ回路部で生じる高周波輻射が論理回路部へ悪影響を及ぼすことを抑制でき、かつ、小型化、低コスト化を犠牲にすることのない半導体装置を得る。

【解決手段】スイッチ回路部を論理回路部にてスイッチング動作させる半導体装置(アンテナスイッチ)。スイッチ回路部と論理回路部とが単一の半導体基板20上に形成されており、論理回路部の直上にシールド導体30が配置されている。シールド導体30はエアブリッジ構造とされ、グランド端子GND3に接続されている。

(もっと読む)

デジタル−アナログ変換器及びこれを用いたアナログ−デジタル変換器

【課題】本発明は、コンデンサの電圧依存による誤差を補正することができるデジタル−アナログ変換器及びこれを用いたアナログ−デジタル変換器を提供することを目的とする。

【解決手段】個別に入力用金属配線52が接続され、該入力用金属配線から入力信号が入力される入力電極20と、該入力電極と対向して配置され、出力信号が出力される出力電極30、30c、30d、20a、20bとを含む単位容量80を複数有するキャパシタアレイ90を備えたデジタル−アナログ変換器100であって、

前記入力用金属配線は、前記出力電極又は前記出力電極に接続された出力用金属配線53を上面視的に囲むか、又は上方から覆うように配置されたガード配線部60を有し、

該ガード配線部と、前記出力電極又は前記出力金属配線との間で形成される寄生静電容量Cp1を各単位容量で調整し、前記キャパシタアレイが有する積分非直線性誤差を補正することを特徴とする。

(もっと読む)

半導体装置

【課題】パワーデバイス駆動回路において、高電位側基準電位(仮想接地電位VS)に発生する負電圧のアンダーシュートによる高電位側電源電圧の低下を確実に抑制する。

【解決手段】共通接地ノード(COM)と仮想接地ノード(VS)の間に高耐圧ダイオードD3を高電圧制御回路(HVIC)内部に共通の基板領域を利用して設ける。

(もっと読む)

スタンダードセルおよび半導体装置

【課題】回路動作に必要な配線を形成するための領域が広く、回路の高速動作が可能なスタンダードセルを提供する。

【解決手段】第1のMOS素子および第2のMOS素子に信号を供給するための信号線が、電源配線および接地配線の2つの配線と平行に設けられ、これら2つの配線に挟まれ、かつ、第1の導電型MOS素子および第2の導電型MOS素子のそれぞれから等しい距離に配置されている構成である。

(もっと読む)

半導体装置、及び、半導体測定システム

【課題】キャリブレーション用の測定パターンを必要とせずに、半導体容量を正確に測定できる半導体装置を提供すること。

【解決手段】第1導電型の半導体基板100の表面部には、第2導電型のウェル106が形成されている。第2導電型のウェル106の表面部には、金属層107−1、第1導電型の拡散層107−2、第2導電型の拡散層108が形成されている。金属層107−1、第1導電型の拡散層107−2、第2導電型の拡散層108上には、それぞれコンタクト103−1〜103−3が形成されている。コンタクト103−1〜103−3上には、それぞれ金属配線層101−1〜101−3が形成されている。寄生容量111〜114を除く容量109をメータ110によって測定するために、金属配線層101−1〜101−3には、それぞれメータ110の接地端子GND、低電圧端子Low、高電圧端子Highが接続される。

(もっと読む)

固体撮像装置

【課題】貫通電極を有する半導体基板の電極から供給する電源の劣化や、半導体基板側から発生する電源ノイズによる影響を低減できる固体撮像装置を提供する。

【解決手段】半導体基板10の第1の主面に形成された撮像素子21と、基板10の第1の主面に対向する第2の主面上に形成されたハンダボール18と、基板10に空けられた貫通孔内に形成された絶縁膜35と、貫通孔内の絶縁膜35上に形成された貫通電極37と、基板10の第1の主面の貫通電極37上に形成された内部電極32とを備える。基板10の第1の主面に対して垂直な方向から見たとき、絶縁膜35と基板10が接する外形は、内部電極32の外形より大きい。

(もっと読む)

増幅回路

【課題】回路構成を複雑にすることなく、所望の周波数帯域において利得を向上させる増幅回路を提供する。

【解決手段】本発明の増幅回路は、半導体基板3と、前記半導体基板3上に形成され、高周波信号を増幅するトランジスタ1と、前記トランジスタ1のソース電極10sに接続された誘導性リアクタンス素子とを有し、前記誘導性リアクタンス素子は、前記半導体基板1の上方に形成され、有機物で構成される有機誘電体層6と、前記有機誘電体層6の前記半導体基板3側と反対側の面上に形成された配線を有する金属再配線層7とを含み、前記配線の一端は、前記トランジスタ1のソース電極10sに接続され、前記配線の他端は接地され、前記誘導性リアクタンス素子のリアクタンス値は、前記高周波信号の周波数帯域の中心周波数において10Ω以下である。

(もっと読む)

81 - 100 / 400

[ Back to top ]