Fターム[5F038BH10]の内容

Fターム[5F038BH10]に分類される特許

61 - 80 / 400

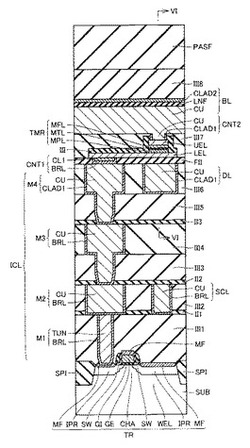

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

キャパシタ、集積装置、高周波切替装置及び電子機器

【課題】能動素子で扱う信号の影響を抑制しつつ、十分な容量密度を得られるキャパシタ、集積装置、高周波切替装置及び電子機器を提供する。

【解決手段】絶縁層12と、絶縁層12の上に設けられた半導体層13と、半導体層13において、能動素子が形成されるアクティブ領域とは電気的に分離して設けられたダミーアクティブ領域20と、を有する基板10と、基板10におけるダミーアクティブ領域20の上に、互いに対向して配置された第1電極31及び第2電極32と、第1電極31と、第2電極32と、の間に設けられた第1誘電体部40と、を備える。

(もっと読む)

双方向スイッチ素子及びそれを用いた双方向スイッチ回路

【課題】安定に動作する双方向スイッチ素子を実現できるようにする。

【解決手段】双方向スイッチ素子は、窒化物半導体からなる半導体層積層体203と、半導体層積層体203の上に形成された第1のオーミック電極211及び第2のオーミック電極212と、第1のゲート電極217及び第2のゲート電極218とを備えている。第1のゲート電極217は、第1のオーミック電極211と電位が実質的に等しい第1のシールド電極221に覆われている。第2のゲート電極218は、第2のオーミック電極212と電位が実質的に等しい第2のシールド電極222に覆われている。第1のシールド電極221の端部は、第1のゲート電極217よりも第2のゲート電極218側に位置し、第2のシールド電極222の端部は、第2のゲート電極218よりも第1のゲート電極217側に位置している。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法及びプログラム

【課題】半導体集積回路において、シールド配線を配置することで配線間のクロストークの影響を削減するとともに、配置したシールド配線の電位を安定化させること。

【解決手段】半導体集積回路の設計方法は、コンピュータが、半導体集積回路の配線パターンにおいて、配置済の信号配線に対して複数のシールド配線を配置する工程と、前記複数のシールド配線のそれぞれを電源配線に接続する工程と、前記複数のシールド配線を相互に接続する工程と、前記複数のシールド配線のうちの電源配線に接続されていないものを除去する工程と、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】同一チップ上に形成されたインダクタ素子とその上方に位置する配線との間に生じる相互作用を、適切に抑制することを課題とする。

【解決手段】半導体基板1と、半導体基板1上に形成された多層配線層と、を有し、多層配線層は、インダクタ素子10と、インダクタ素子10の上方に形成された配線11A乃至11Cおよび12と、インダクタ素子10とインダクタ上配線11A乃至11Cおよび12との間に形成され、平面視で前記インダクタ素子10を覆う、固定電位を有する遮蔽導体13及び14と、を有する半導体装置が提供される。

(もっと読む)

半導体装置

【課題】半導体装置の集積回路を自動配線にて設計する際、SMC(Scan Mode Control:スキャンモード制御)信号などの静的信号を複数の回路セルに同時に供給する静的信号配線を、通常信号配線と同じ配線層に配置すると、集積回路全体の配線リソースが不足しやすい。

【解決手段】本発明の半導体装置では、静的信号を複数の回路セルに同時に供給する静的信号配線を、電源配線やグランド配線と同じ下層部に配置する。このため、通常信号配線を上層部に自由に配置することが可能となり、特に自動配線時における配線性の向上が期待される。その結果、集積回路全体としてののべ面積の削減、半導体装置全体としての製造コストの削減、などが期待される。

(もっと読む)

集積回路をDCおよびRF遮蔽する方法構造

【課題】集積回路をDCおよびRF遮蔽する方法と構造を提供すること。

【解決手段】組み合わせられて集積回路デバイスを形成する回路を電磁気的に遮蔽するための方法であって、導電性材料によって横方向および下方を囲まれた隔離型のシリコン・アイランドを供給する。

(もっと読む)

伝送線のためのシールド構造体

シールド構造体は、集積回路上の第1金属化層に形成された櫛状構造体が複数の歯を備え櫛状構造体の歯は他方の櫛状構造体に向かって延びる第1、第2櫛状構造体と、第1櫛状構造体から上方に延びる複数の第1導電性ビアと、第2櫛状構造体から上方に延びる複数の第2導電性ビアと、第1金属化層の上方の第2金属化層に配置された第1、第2平面構造体と、第1平面構造体から複数の第1導電性ビアに向かって下方に延びる複数の第3導電性ビアと、第2平面構造体から複数の第2導電性ビアに向かって下方に延びる複数の第4導電性ビアとを備え、第1、第2櫛状構造体、第1、第2平面構造体及び第1〜第4導電性ビアは全て同電位であり接地されることが好ましい。ある実施形態では1つ以上の信号線が第1、第2平面構造体間の第2金属化層に配置され、他の実施形態では1つ以上の信号線が第1、第2平面構造体間の第3金属化層に配置される。 (もっと読む)

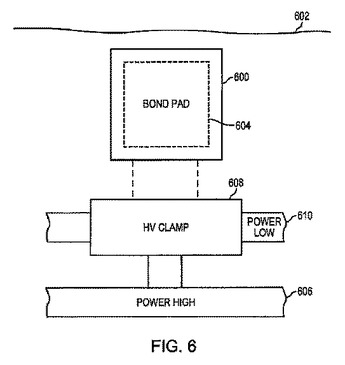

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

デジタルCMOS工程において周波数合成器に用いられるソレノイドインダクタ

本発明のデジタルCMOS工程で周波数合成器に用いられるソレノイドインダクタは、所定の幅を有し、両側が垂直方向に積層され、ソレノイド構造を有する多数の配線金属と、両側に積層された多数の配線金属の相互間を連結する配線金属連結部とを備え、両側に積層された多数の配線金属のうち、所定数の下位層配線金属と、下位層配線金属の相互間を連結する配線金属連結部とがそれぞれ連結され重なる。本発明によると、デジタルCMOS工程で4〜5GHz以上の周波数帯域で動作する周波数合成器を具現するためにソレノイドインダクタを用いることで、RF CMOS工程でのみ具現可能な数GHz帯域の周波数合成器を具現することができる効果がある。  (もっと読む)

(もっと読む)

微小容量素子及びこれを用いた半導体装置

【課題】精度の高くノイズに強い微小容量素子を提供する。

【解決手段】

微小容量素子は、絶縁層上に成膜されかつそれぞれが互いに対向して第1間隙を画定する対向面を有する第1及び第2金属電極と、絶縁層上に成膜されかつ外部電位に接続可能でありかつ第1間隙内において結合容量制限スリットを画定するシールド電極と、からなる。

(もっと読む)

半導体装置

【課題】ラッチアップを利用したESD保護のための半導体装置において、ラッチアップ発生電圧を任意の値に設定すること。

【解決手段】半導体装置300は、P型基板301と、P型基板301の表面に形成されたN型ウェル領域302と、N型ウェル領域302の表面上のP+型拡散領域303及びN+型拡散領域304と、P型基板301とN型ウェル領域302との境界上に配置された酸化膜305と、酸化膜305の一部の上に配置されたポリSi306と、P型基板301の表面上のP+型拡散領域307及びN+型拡散領域308とを備える。フローティング電極309は、ポリSi306及びN型ウェル領域302とそれぞれ容量結合するように配置されている。ポリSi306は接地されている。

(もっと読む)

抵抗素子及びその製造方法

【課題】 従来のポリシリコン層を抵抗層とする抵抗素子は、抵抗素子のシート抵抗を例えば10MΩ/□以上に高くしたい場合、所望のシート抵抗が得られない問題があった。この原因は、製造工程中にポリシリコン層上の絶縁膜が帯電することが考えられ、このため設計値より2桁以上も低い値となってしまっていた。また、同一ウエハ内であっても抵抗素子毎に抵抗層のばらつきが大きくなる問題があった。

【解決手段】 ポリシリコン層を抵抗層とする抵抗素子において、抵抗層を被覆する絶縁膜の上に、保護層を設ける。保護層は金属層であり、抵抗素子の配線層や、電極等の金属層と同一金属層で形成できる。保護層は、ポリシリコン層の曲折部が露出するパターンに設ける。また、保護層に固定電位を印加する。固定電位に応じて、異なるシート抵抗が得られる。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、印加電圧により抵抗値にバラツ

キが生じない半導体装置を提供することを目的とする。

【解決手段】半導体基板(2)上にバイポーラ素子とともに抵抗素子を形成さ

れる半導体装置(100)において、抵抗素子は、半導体基板(2)上に形成さ

れ、半導体基板(2)を絶縁する絶縁層(101)と、絶縁層(101)上に形

成され、抵抗を形成する抵抗層(102)とを設ける。

(もっと読む)

半導体パッケージ

【課題】磁気メモリ素子に記憶された情報を不正な手段で読み出すことを困難にして、磁気メモリ素子に記憶された情報が漏洩することを抑制できる半導体パッケージを提供すること。

【解決手段】磁気を加えることにより情報を記憶するメモリセル11を有するダイ10を内部に備える半導体パッケージ1であって、パッケージ本体20の内部に配置され、メモリセル11の磁気メモリ素子を磁化可能な磁界MF1を少なくともメモリセル11が位置する空間に発生させる磁界源41と、ダイ10の基板面10Aを覆って配置され、メモリセル11に加わる磁界MF1を減衰させる磁気シールド材42と、を備えることを特徴とする。

(もっと読む)

集積回路装置及び電子機器

【課題】アナログ処理の特性の向上を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、信号が入力されるパッドPANTと、パッドPANTを介して入力される信号についてのアナログ処理を行うアナログ回路と、アナログ回路の信号入力ノードとパッドPANTとの間に設けられるキャパシターCAを含む。パッドPANTとキャパシターCAの一端とが、最上層金属層ALEで形成されるパッド配線LNPにより接続される。

(もっと読む)

半導体装置

【課題】半導体装置の伝送線路の信号伝達効率を高くする

【解決手段】本発明は、多層配線400内に形成され、信号線342下にあり、トランジスタ領域上に形成された第1導体パターン312を有する、半導体装置に関する。第1導体パターン312はグラウンドまたは電源に接続し、トランジスタ領域と重なる。また、信号線342は第1導体パターン312と重なっている。第1導体パターン312は複数のトランジスタ形成領域と重なっていてもよい。第1導体パターン312の下にトランジスタ形成領域を複数有していていもよい。

(もっと読む)

半導体装置

【課題】WCSPの再配線を用いて、回路から発生するノイズが他の回路ブロックへ干渉することを防ぎ、特性劣化を防止できる半導体装置を提供する。

【解決手段】2以上の回路ブロック1、2が形成される半導体基板と、前記半導体基板の回路形成面上に配置され外部端子3a〜3e、4a〜4eが先端に設けられるポストと、該ポストの基端と前記半導体基板の回路形成面における前記回路ブロック1、2の電極端子とを接続する再配線12a、12b、16a、16bとが樹脂封止された封止樹脂層とを備える半導体装置において、前記2以上の回路ブロック1、2のうち少なくとも1つの回路ブロック1、2では、接地用の前記電極端子と接地用の前記外部端子3a〜3e、4a〜4eとを接続する前記再配線12a、12b、16a、16bが自回路ブロック1、2の形成領域の全部または一部を覆うように設けられている。

(もっと読む)

半導体装置、製造方法および設計方法

【課題】インダクタをグローバル層に配置してもインダクタ性能の低下を許容値内に抑えるようにインダクタの形成領域上部をシールドできる半導体装置、製造方法および設計方法を提供すること。

【解決手段】半導体基板上に完成された集積回路の形成面上面を被覆する保護膜上の、前記集積回路内の高周波回路においてノイズに対するシールド対策を必要とする少なくともインダクタの形成領域と対向する領域に、パッケージを介して接地される所定形状のシールドメタル層が形成されている半導体装置。

(もっと読む)

半導体装置及びこれを備える半導体パッケージ

【課題】パッケージ基板上におけるカップリングノイズを低減可能な半導体装置を提供する。

【解決手段】第1のデータ入出力パッド、第1の電源パッド、第2のデータ入出力パッド及び第2の電源パッドがこの順にX方向に配列されたパッド群Pを複数備える。第1及び第2のデータ入出力パッドはそれぞれ第1及び第2のデータ入出力バッファに接続され、第1の電源パッドは第1及び第2のデータ入出力バッファに第1の電源電位を供給し、第2の電源パッドは第1及び第2のデータ入出力バッファに第2の電源電位を供給する。各パッド群Pに含まれる第1のデータ入出力パッドは、他のパッド群に含まれる第2の電源パッド又はいずれのパッド群にも含まれない複数の電源パッドのいずれかと隣接している。これにより、パッケージ基板上におけるカップリングノイズを防止しつつ、パッド総数の増加を抑制することが可能となる。

(もっと読む)

61 - 80 / 400

[ Back to top ]