Fターム[5F038BH10]の内容

Fターム[5F038BH10]に分類される特許

21 - 40 / 400

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗素子について、レイアウト面積の増大を防ぎつつ、周辺の電荷の影響を受けずに安定した抵抗値を得ることができ、しかも、抵抗体に印加できる電位の極性に制限のない半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1上のLOCOS酸化膜3上に形成された抵抗素子10と、を備え、抵抗素子10は、LOCOS酸化膜3上に形成されたシールド用ポリシリコン膜11と、シールド用ポリシリコン膜11上に形成されたシリコン酸化膜13と、シリコン酸化膜13上に形成されたポリシリコン抵抗体15と、ポリシリコン抵抗体15の一方の端部に接合された第1の電極21と、ポリシリコン抵抗体15の他方の端部に接合された第2の電極22と、シールド用ポリシリコン膜11に接合された第3の電極23と、を有し、第1の電極21及び第2の電極22うちの一方が、配線25を介して第3の電極23と電気的に接続されている。

(もっと読む)

半導体装置

【課題】キャパシタ構造の信号線およびGND電極を抵抗成分やインダクタンス成分を最小限にできる構造の配線基板を有する半導体装置を提供する。

【解決手段】信号線の一部を構成する中心導体2cの周囲に誘電体2bを介して同心円状にシールド線を構成する外側導体2aを備えるキャパシタ構造部2を有した構成とする。そして、2つのスルーホール3内に設けた各キャパシタ構造部2の中心導体2cについては、配線基板の表面側で各中心導体2cが上面配線5に電気的に接続され、裏面側でもう一方のキャパシタ構造部2の中心導体2cと第1下面配線6を介して電気的に接続され、さらに、各キャパシタ構造部2の外側導体2aについては、配線基板の裏面側に全面に一様に形成された第2下面配線7で覆われた状態で電気的に接続されるようにする。

(もっと読む)

半導体装置

【課題】規格により規定された速度による信号の転送を実現し、半導体装置やそれを内蔵した電子機器の誤動作を防止する。

【解決手段】第1の半導体素子101の導体配線層106に、パッケージ基板100の信号端子103と第2の半導体素子102の信号端子117とを接続する信号線導体113aと、パッケージ基板100の電源端子104と第2の半導体素子102の電源端子118とを接続する電源導体114とを、信号線導体113aが導体配線層106において、信号線導体113aとの間に水平方向に一定の間隔をあけて隣接する電源導体114に挟まれるように形成する。

(もっと読む)

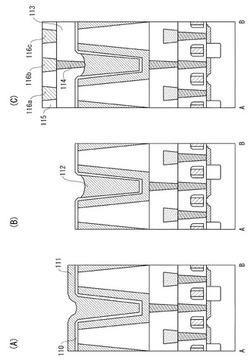

垂直集積システム

【課題】コストのかかる空間をとらずに電子部品内に個別パッシブ部品を組み込むことが可能な垂直集積システムを提供する。

【解決手段】集積回路システム100は、半導体ダイ110の前面上に製造された第一のアクティブ層と、半導体ダイ110の裏面上の第二の予め製造された層とを含み、その第二の予め製造された層は、その中に埋め込まれた電気部品を有し、その電子部品は、少なくとも一つの個別パッシブ部品140を含む。また、集積システム100は、第一のアクティブ層及び第二の予め製造された層を結合する少なくとも一つの電気経路150も含む。

(もっと読む)

半導体装置

【課題】安定した特性のヒューズ素子を有する半導体装置を提供する。

【解決手段】半導体装置100は、基板10と、基板10の上方に形成され、空洞部20を画成する被覆構造体30と、空洞部20に収容されたヒューズ素子40a,40b,40cと、を含み、被覆構造体30は、導電層を有し、ヒューズ素子40a,40b,40cの材質は、導電層の材質と同じである。

(もっと読む)

集積回路内における、インターフェースデバイスの面積効率の良い配列

【課題】過度にシステムの中にスキューを増加させずに、増加した数の入力/出力デバイスを有するシステムを提供する。

【解決手段】論理回路を備えるコアと、処理コアからおよび処理コアへ信号を伝送するための、複数のインターフェースデバイスであって、2つのタイプのインターフェースデバイスを備える、複数のインターフェースデバイスと、コアに電力を送達するための、電力インターフェースデバイスである、1つのタイプと、コアと集積回路の外部のデバイスとの間で、データ信号を伝送するための信号インターフェースデバイスである、第2のタイプと、を備え、複数のインターフェースデバイスは、コアの外縁に向かう外側列、およびコアの中心により近い外側列の内側にある内側列の、2列に配設され、内側列は、2つのタイプのインターフェースデバイスのうちの一方を備え、外側列は、2つのタイプのインターフェースデバイスのうちの他方を備える、集積回路が開示される。

(もっと読む)

電子装置

【課題】大型化を招くことなく装置に関する情報を外部から好適に読み取り得る電子装置を提供する。

【解決手段】半導体チップ10は、装置に関する情報が外部から読み取り可能に記憶されるRFIDチップ30を搭載する回路ブロック11がモールド部材16によりモールドされてパッケージ化されている。このRFIDチップ30は、回路上に形成される複数のパッド13のうちモールド部材16によりモールドされた状態で外部に接続されていない検査用パッド20上に配置されている。

(もっと読む)

半導体装置

【課題】複数のフローティング領域の間の電位差の不均一を軽減することができる半導体装置を提供する。

【解決手段】半導体装置は、領域3(k)と領域3(k+1)間に、外部容量6(k)を備えている。複数の外部容量6(k)は、その容量がkの増加とともに(即ち、図1の紙面右側から紙面左側に向かうほど)大きくなるように選定されている。この構造により、領域3(k)と領域3(k+1)間の電位差の不均一を軽減することができる。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置

【課題】高出力の高周波信号の影響を抑制することが可能な半導体装置を提供する。

【解決手段】半導体装置は、電子回路が設けられた主面を有する半導体基板10と、前記主面の上に絶縁膜2,3,4を介して設けられたパッシブ回路30と、を備える。そして、前記半導体基板と前記パッシブ回路との間に前記パッシブ回路から絶縁されて設けられ、前記主面に平行な少なくとも1方向に流れる電流を遮断する間隙45を有した第1の導体層40と、前記第1の導体層と前記パッシブ回路との間に、前記第1の導体層および前記パッシブ回路から絶縁されて設けられ、前記主面に平行な少なくとも1方向に流れる電流を遮断する間隙55を有し、前記パッシブ回路から見た前記第1の導体層の間隙を覆う第2の導体層50と、を備える。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置

【課題】送信機の変調器のキャリアリークを従来よりも高精度に抑制する。

【解決手段】半導体装置10において、信号分配部37は、発振器26によって生成されて入力部IN1に入力された高周波信号を第1および第2の信号に分配し、第1および第2の出力部OA1,OB1からそれぞれ出力する。変調器30は、ベースバンド信号を第1の信号で変調して出力する。オフセット調整部90は、第2の信号と変調器30の出力から漏洩した第1の信号とを比較することによってベースバンド信号のオフセットを調整する。上記の信号分配部37は、入力部IN1と第1の出力部OA1との間に設けられた第1の容量素子Ccapと、第1の出力部OA1と第2の出力部OB1との間に設けられた第2の容量素子Cpとを含む。第1の容量素子Ccapの静電容量は、第2の容量素子Cpの静電容量よりも大きい。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】良好な伝送性能と小さい配置面積を両立可能なデータバスを備える半導体装置を提供する。

【解決手段】本発明の半導体装置は、配線層M1、M2と、複数のデータ入出力端子と、N本のデータ線(DU、DL)を含むデータバスとを備え、N本のデータ線は所定の配線長の長短に応じた2種類のデータ線群を含む。配線層M1、M2にはデータ線(DL、DU)の各々に隣接する複数のシールド線(Sa、Sb、Sc)が配置され、各データ線(DL、DU)は、配線層M1、M2の積層方向で互いに重ならない位置に配置される。このような配線構造により、各データ線(DL、DU)の間のカップリング容量を抑え、データバスのクロストークを防止することができる。

(もっと読む)

半導体装置

【課題】チップ面積を拡大することなく信頼性の高い配線レイアウトを実現する。

【解決手段】信号線S1〜S3と電源線VDD1,VSS1がY方向に延在する下層配線層と、信号線S4〜S6と電源線VDD2,VSS2がX方向に延在する上層配線層と、対応する信号線が重なり合うオーバーラップ領域OL1に設けられたビア導体VE1と、対応する電源線が重なり合うオーバーラップ領域OL2,OL3に設けられたビア導体VE2,VE3とを備える。領域OL1のX方向における幅は、領域OL2,OL3のX方向における幅よりも広く、これにより、領域OL1には複数のビア導体VE1a,VE1bが設けられる。また、電源線VDD1,VSS1は、領域OL1との干渉を避けるようY方向に分断されている。複数の下層配線は、一つのビアを含むミニマムピッチで2つのビアを配置している。

(もっと読む)

電力増幅器

【課題】複数のトランジスタを均一に動作させ、低消費電力及び良好な歪特性を実現する。

【解決手段】高周波信号を増幅する電力増幅器100であって、上部電極120a及び下部電極120bを有し、高周波信号が入力される整合容量120と、整合容量120の下部電極120bから出力される高周波信号を増幅する複数のトランジスタ110が所定の方向に並んで配置されているトランジスタ列とを備え、トランジスタ列に隣り合う領域において、トランジスタ列の両端から略等しい距離には、接地されたビアホール170が形成され、下部電極120bは、ビアホール170を挟んで高周波信号が均等に分配されるように配置されたマイクロストリップ線路であり、複数のトランジスタ110のベース端子に接続される。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化されても高精度を維持できるキャパシタを提供する。

【解決手段】キャパシタは、平面上に交互に配列した、直線状で第1の長さを有し第1の方向に延在する第1の電極パターンと、直線状で前記第1の長さより短い第2の長さを有し、前記第1の方向に延在する第2の電極パタ―ンと、前記第1の電極パターンに第1の電圧を、第1のビアプラグを介して供給する第1の配線パタ―ンと、前記第2の電極パターンに第2の電圧を、第2のビアプラグを介して供給する第2の配線パタ―ンと、を備え、前記第1および第2の電極パターンをそれぞれの前記第1の方向で比較した場合、前記第1の電極パターンの第1の端部が、前記第1の端部に対応する前記第2の電極パターンの第2の端部よりも突出しており、前記第1の電極パターンの前記第1の端部に対向する第3の端部が、前記第3の端部に対応する前記第2の電極パターンの第4の端部よりも突出している。

(もっと読む)

半導体装置

【課題】 カップリングノイズを低減すること。

【解決手段】 半導体装置は、第1の回路と、第2の回路と、第1の配線と、一対のシールド線とを含む。第1の回路は、所定電圧を発生する電圧発生回路を含み、所定電圧を出力端に出力する。第1の配線は、第1の回路の出力端を第2の回路の入力端に結線する。一対のシールド線は、第1の配線を挟むように配置され、一方には電圧発生回路および第2の回路の少なくとも一方を駆動する電源電位が供給され、他方には電圧発生回路および第2の回路の少なくとも一方を駆動する接地電位が供給される。

(もっと読む)

21 - 40 / 400

[ Back to top ]