Fターム[5F038CA09]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 寄生防止 (242)

Fターム[5F038CA09]に分類される特許

1 - 20 / 242

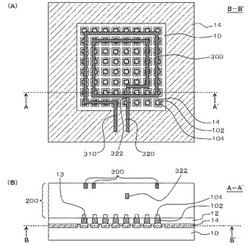

半導体装置

【課題】インダクタの下方に位置する素子分離膜に開口を設けてその開口内に半導体基板を残しつつ、インダクタの下方に位置する半導体基板に渦電流が発生することを抑制する。

【解決手段】インダクタ300は、多層配線層200に形成されており、素子分離膜12の上方に位置している。開口13は、素子分離膜12のうち少なくとも平面視でインダクタ300と重なる領域に形成されている。また、素子分離膜12とインダクタ300の間に位置するいずれの層にも、インダクタ300と半導体基板10の間をシールドするシールド導電部材は形成されていない。

(もっと読む)

基準電圧回路及び半導体基板

【課題】電源電位が接地電位に対して変動するハイサイド回路又はローサイド回路において、電源電位の変動の影響を回避し、安定した基準電圧を出力することができる基準電圧回路及び半導体基板を提供する。

【解決手段】本発明は、P型半導体基板20上のNウェル層21内に形成したハイサイド回路中において、Nウェル層21をコレクタとし、Nウェル層21内に形成したP領域23をベースとし、ベースの上層に形成したN領域24をエミッタとし、ハイサイド回路素子22を構成する基板を、コレクタとしてのNウェル層21とで共通化した。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置に負電流が流れた場合でも、回路素子を構成する深い半導体層の電位に対して、半導体基板の電位が低くなるのを抑制して寄生素子を作動させず、半導体装置の誤動作を防止する。

【解決手段】本発明は、n型の半導体基板3と、半導体基板3の一面に形成し、接続する負荷に電力を供給する電力素子1と、n型のソース・ドレイン領域を有するMOSトランジスタ2cを少なくとも1つ含む回路素子2と、電力素子1および回路素子2に対し独立して配置したp型の半導体層4と、半導体基板3および半導体層4と接続する外部回路とを備えている。外部回路は、電源と、電源に一端を接続する抵抗素子と、抵抗素子の他端にアノード電極を接続し、カソード電極をGND接地するダイオードとを有し、抵抗素子の他端に半導体層4を接続する。

(もっと読む)

半導体装置

【課題】配線間の寄生容量を削減可能にした半導体装置を提供する。

【解決手段】X方向に配列する複数のトランジスタについて、夫々が、対応するダミーゲートDG1,DG2を挟む複数のソース拡散層S1,S2に接続する第2及び第3の金属配線M12,M13は、2つのS1,2つのS2に夫々接続する複数の第1のビアV1の両方を含む第1の幅L1と、V1を含まず、L1よりも短い第2の幅L2と、を有する。ドレイン拡散層D1に接続する第1の金属配線M11と、M12との間、並びにM11及びM13の間の夫々は、L1に対応する第1のギャップSP1と、L2に対応する、L1よりも大きな第2のギャップSP2と、を有する。好ましくは、M11〜M13の夫々と第2のビアV2を介して接続される第4〜第6の金属配線M24〜M26の夫々は、L1よりも短い第3の幅L3を有する。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

縦構造キャパシタを備える半導体装置

【課題】縦構造キャパシタの剥離を防止し、チップサイズの増加を抑制した半導体装置を提供する。

【解決手段】半導体装置には、第1の回路の機能素子として使用される第1の縦構造キャパシタと、第2の回路の機能素子として使用され、第1の縦構造キャパシタよりも容量値の大きい第2の縦構造キャパシタと、が含まれている。半導体装置では、第1の縦構造キャパシタを、第2の縦構造キャパシタに隣接、又は、包含させるようにレイアウトする。

(もっと読む)

ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

(もっと読む)

半導体集積回路

【課題】電荷転送効率が高い転送トランジスタを備える半導体集積回路を提供することを目的とする。

【解決手段】実施形態に係る半導体集積回路は、ゲート電極を有し、当該ゲート電極及び一の拡散層が第1配線でダイオード接続された転送トランジスタと、クロック信号が供給されるクロック信号線とを備え、前記クロック信号線の一部である第1部分クロック信号線の少なくとも一部が前記ゲート電極上に形成されていることを特徴とする。

(もっと読む)

ブートストラップ回路、インバータ回路、走査回路、表示装置、及び、電子機器

【課題】ブートストラップゲインの上昇を可能にしたブートストラップ回路、当該ブートストラップ回路を用いたインバータ回路、当該インバータ回路を用いた走査回路、当該走査回路を用いた表示装置、及び、当該表示装置を有する電子機器を提供する。

【解決手段】トランジスタと、当該トランジスタの一方のゲート電極とソース/ドレイン領域との間に接続された容量とを有し、当該一方のソース/ドレイン領域の電位の変動に応じてゲート電極の電位が変動するブートストラップ動作を行うブートストラップ回路において、トランジスタについて、ゲート電極の中心を通る線に関してソース領域とドレイン領域とを非対称な構造にする。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

半導体装置

【課題】容量素子を備え、電気的特性の安定化が可能な半導体装置を提供する。

【解決手段】半導体基体1上の配線層に形成されている配線と絶縁層とからなる容量素子10を備える。そして、容量素子10の形成領域内の半導体基体11上に形成されている導体パターンと、導体パターンの電位を固定するための電位固定端子28とを備える半導体装置を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

半導体装置

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

ESD保護回路

【課題】ESD保護回路の配線部の寄生容量を低減する。

【解決手段】一つの実施形態によれば、ESD保護回路は、複数のダイオードから構成されるESD保護ダイオード、第一の空隙部、及び第二の空隙部が設けられる。ESD保護ダイオードは、信号線と低電位側電源の間に設けられ、信号線に印加される静電気が入力される。第一の空隙部は、信号線と複数のダイオードの少なくともいずれか1つを接続する第一の配線と複数のダイオードが形成される半導体基板の間に設けられる。第二の空隙部は、複数のダイオードの間を接続する第二の配線と半導体基板の間に設けられる。

(もっと読む)

高周波半導体スイッチ

【課題】ゲート配線に良好な電圧分布を形成し、挿入損失特性およびハーモニック特性を向上した高周波半導体スイッチを提供する。

【解決手段】無線通信を切り替えるための高周波半導体スイッチに含まれる電界効果型トランジスタ50であって、基板に形成されたソース領域100と電気的に接続され、一の方向に延びるソース配線60と、基板に形成されたドレイン領域110と電気的に接続され、ソース配線と略平行に延びるドレイン配線70と、ソース配線60およびドレイン配線70の間において、ソース配線60およびドレイン配線70と略平行に延びる平行部分122を有するゲート120と、ゲート120に電圧を印加するためゲート配線80と、ゲート120およびゲート配線80を電気的に接続するゲートビア82と、を有し、平行部分122は、2つの端部126を有し、ゲートビア82から2つの端部126にそれぞれ電圧の印加の経路が形成される電界効果型トランジスタ。

(もっと読む)

抵抗素子及び反転バッファ回路

【課題】無駄な電流や信号の歪みを発生させることなく、抵抗素子層の周辺の半導体基板や、抵抗素子層の上部を通過する電源線、信号線等の電位によって抵抗値が変化するのを抑えることのできる抵抗素子及び反転バッファ回路を提供する。

【解決手段】抵抗素子10は、半導体基板14上に、第1の電極11及び第2の電極12を有する抵抗素子層13が形成されている。第1の電極11の電位によってバイアスされた第1の導電層15と、第2の電極12の電位によってバイアスされた第2の導電層16とで、抵抗素子層13の下部が均等に覆われている。このように、両端をバイアスされた抵抗素子層13の下部又は上部の少なくとも一方を覆う第1の導電層15及び第2の導電層16によって、抵抗素子層13の周辺の半導体基板14等との電圧差による抵抗値の変化を相殺することで、抵抗値の変化を抑える。

(もっと読む)

ハイサイドスイッチ回路、インターフェイス回路、および電子機器

【課題】ハイサイドスイッチの過電流の検出精度を高めることが可能なハイサイドスイッチ回路、および、そのハイサイドスイッチ回路を含む装置を提供する。

【解決手段】ハイサイドスイッチ回路10は、入力端子11と出力端子12との間に電気的に接続されるスイッチ(MOSトランジスタ15)と、ゲート制御部16と、過電流検出部20とを備える。過電流検出部20は、抵抗素子21と、比較器22とを含む。比較器22は、抵抗素子21の電圧V1がしきい電圧を超える場合に、過電流を検出する。比較器22は、過電流時の検出電圧V1がしきい電圧を上回るように、予め調整される。抵抗素子21の抵抗値の精度が高くない場合にも、比較器22の調整によって、過電流の検出精度が高められる。

(もっと読む)

ハイサイドスイッチ回路、インターフェイス回路、および電子機器

【課題】ハイサイドスイッチの過電流が検出された場合に、ハイサイドスイッチだけでなくハイサイドスイッチに接続される回路を保護することが可能なハイサイドスイッチ回路、および、そのハイサイドスイッチ回路を含む装置を提供する。

【解決手段】ゲート電圧降圧部31は、過電流検出部20からの電流制限信号に応じて、MOSトランジスタ15のゲート電圧を第1の電圧から、第1の電圧と第2の電圧との間の第3の電圧まで、第1の時間変化率で低下させる。これによりMOSトランジスタ15のオン抵抗がMOSトランジスタ15の完全オン時のオン抵抗より高くなる。ゲート電圧降圧部32は、ゲート電圧が第3の電圧に達した後に、ゲート電圧を第3の電圧から第2の電圧まで第2の時間変化率で低下させる。第1の時間変化率は、第2の時間変化率よりも大きい。

(もっと読む)

半導体集積回路及び半導体集積回路装置

【課題】従来技術と比較して占有面積が小さく、かつ基板電流が流れる経路の抵抗を低く抑え、寄生バイポーラトランジスタの動作を抑制することができる半導体集積回路及び半導体集積回路装置を提供する。

【解決手段】p型半導体基板10に形成されたドレイン領域D1、ソース領域S1、及びp型活性領域Bと、ドレイン領域D1とソース領域S1との間に形成されたゲート電極TG1と、ドレイン電極TD1と、ソース電極TS1と、基板電極TB1とを備えたNMOSトランジスタMN1と、ソース領域S1とp型活性領域Bとの間に形成されたドレイン領域D2及びソース領域S2と、p型活性領域Bと、ドレイン領域D2とソース領域S2との間に形成されたゲート電極TG2と、ドレイン電極TD2と、ソース電極TS2と、基板電極TB2とを備えたNMOSトランジスタMN2とを備え、NMOSトランジスタMN2は、基板電極TB1とソース電極TS1との間に接続される。

(もっと読む)

1 - 20 / 242

[ Back to top ]