Fターム[5F038CA18]の内容

Fターム[5F038CA18]に分類される特許

1 - 20 / 390

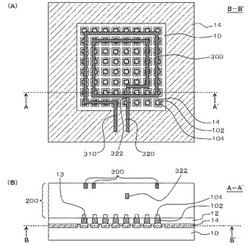

半導体装置

【課題】インダクタの下方に位置する素子分離膜に開口を設けてその開口内に半導体基板を残しつつ、インダクタの下方に位置する半導体基板に渦電流が発生することを抑制する。

【解決手段】インダクタ300は、多層配線層200に形成されており、素子分離膜12の上方に位置している。開口13は、素子分離膜12のうち少なくとも平面視でインダクタ300と重なる領域に形成されている。また、素子分離膜12とインダクタ300の間に位置するいずれの層にも、インダクタ300と半導体基板10の間をシールドするシールド導電部材は形成されていない。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】SETUP時間とHOLD時間のどちらも満足させるタイミングの調整が可能な技術を提供する。

【解決手段】半導体集積回路の配置配線レイアウトを決定した後に、所定の信号線を伝搬するデータのタイミング情報に基づいて、タイミング違反を有する違反データの遅延情報を抽出する。その抽出された遅延情報に基づいて、タイミング違反を解消するための追加すべき容量値を算出する。また、違反データを伝搬する配線のレイアウト配置情報に基づいて、違反データを伝搬する配線の近傍の電源容量セルを検出する。また、算出された容量値に基づいて、検出された電源容量セルを、電源容量セルとレイアウト外形・電源/GND配線配置位置が同じ調整容量セルに置き換える。そして、置き換えた調整用容量セルのゲートと違反データを伝搬する配線とを接続して再配線を実行する。

(もっと読む)

半導体装置

【課題】高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制する。

【解決手段】半導体装置1は、高周波配線、およびダミー導体パターン20(第2のダミー導体パターン)を備えている。ダミー導体パターン20は、高周波配線と相異なる層中に形成されている。ダミー導体パターン20は、平面視で、高周波配線と重なる領域を避けるように配置されている。これにより、高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制できる。

(もっと読む)

配線設計装置、配線設計方法、及びプログラム

【課題】半導体集積回路に対し、ダミーパターン配置後に、ダミーパターンを使用したECO(Engineering Change Order)配線設計を行う。

【解決手段】配線設計装置は、半導体集積回路にダミーパターンを配置し、ダミーパターンをECO配線に変更し、ダミーパターンの再配置及び電気的ショートを発生することなくECO配線を行う。これにより、ECO配線を行う時に、ダミーパターン再挿入や、既存配線とのショートを発生せずに、設計TAT(Turn Around Time)増を抑制することを可能とする。

(もっと読む)

半導体装置

【課題】半導体基板の上方にコイルが設けられた半導体装置において、コイル直下の半導体基板に回路を形成することができる半導体装置を提供する。

【解決手段】半導体装置は、一面11を有する半導体基板10と、半導体基板10の一面11に形成された絶縁層20と、絶縁層20の上方に形成されたコイル30と、を備えて構成されており、半導体基板10はコイル30の直下にスリット12を備えている。このスリット12は、コイル30のうち、半導体基板10の一面11に平行な面方向のうちの一方向に沿って形成された部分の直下に位置している。これにより、スリット12を境界として半導体基板10の渦電流面積が小さくなるので、半導体基板10に発生する渦電流による損失が低減し、コイル30の下部に位置する半導体基板10に回路を形成することが可能となる。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

半導体装置

【課題】スパイラルインダクタを有する半導体装置における寄生容量の低減と、Q値の低下を抑制すること。

【解決手段】半導体基板と、前記半導体基板の表面近傍に設けられた複数個の素子分離領域と、前記素子分離領域間の半導体基板上に設けられた能動素子部と、基板上に積層された複数の配線層と、前記素子分離領域のうち第1の素子分離領域の鉛直上方であって、かつ、前記配線層のうち少なくとも最上の配線層に設けられたスパイラルインダクタとを備え、前記スパイラルインダクタが形成されたインダクタ形成領域の鉛直下方であって、かつ、前記第1の素子分離領域の半導体基板表面上にシリサイド形成防止膜が形成されていることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】配線間の寄生容量を削減可能にした半導体装置を提供する。

【解決手段】X方向に配列する複数のトランジスタについて、夫々が、対応するダミーゲートDG1,DG2を挟む複数のソース拡散層S1,S2に接続する第2及び第3の金属配線M12,M13は、2つのS1,2つのS2に夫々接続する複数の第1のビアV1の両方を含む第1の幅L1と、V1を含まず、L1よりも短い第2の幅L2と、を有する。ドレイン拡散層D1に接続する第1の金属配線M11と、M12との間、並びにM11及びM13の間の夫々は、L1に対応する第1のギャップSP1と、L2に対応する、L1よりも大きな第2のギャップSP2と、を有する。好ましくは、M11〜M13の夫々と第2のビアV2を介して接続される第4〜第6の金属配線M24〜M26の夫々は、L1よりも短い第3の幅L3を有する。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、配線の伝送特性が不安定となってしまう。

【解決手段】半導体装置1は、配線10、およびダミー導体パターン20を備えている。配線10は、5GHz以上の周波数を有する電流が流れる配線である。配線10の近傍には、ダミー導体パターン20が配置されている。ダミー導体パターン20の平面形状は、180°を超える内角を有する図形に等しい。

(もっと読む)

半導体ウェハ及びその製造方法

【課題】スクライブ線領域におけるダミーパターンが影響して配線形成の際に露光時のアライメント波形検出精度を低下させるおそれがあった。

【解決手段】複数の素子形成領域と、素子形成領域を相互に区画するスクライブ線領域と、素子形成領域において半導体基板上に配置された複数のパターンと、スクライブ線領域において半導体基板上に配置されるとともに、パターンと同様な構成の複数のダミーパターンと、パターン及びダミーパターンを含む半導体基板上に形成されるとともに、上面が平坦化された層間絶縁膜と、スクライブ線領域における層間絶縁膜に形成されるとともに、ダミーパターンと重ならない領域にて半導体基板に通じないように形成された穴状のアクセサリパターンと、を備える。

(もっと読む)

半導体集積回路及びそれを備えた半導体装置、並びに電子機器

【課題】半導体集積回路において、ダイシング時の保護膜の剥離を抑制しつつ保護膜の密着性を確保し、チップサイズの小型化を実現する。

【解決手段】半導体集積回路は、スクライブ領域2近傍に形成されたシールリング3と、パッド4と、シールリング3とパッド4との間に形成された配線5と、シールリング3と、ダミーパターン8と、保護膜6と、保護膜7とを備えている。保護膜7の終端縁9は、シールリング3とパッド4との間に位置しており、ダミーパターン8における配線5を挟んで互いに向かい合う部分の端部が、保護膜7の終端縁9を中心に半導体チップ1の周縁部側及び中央部側方向に5μmの間隔以内に位置している。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

レイアウト方法及び半導体装置の製造方法

【課題】ダブルパターニングによるトランジスタの特性ばらつきを抑える。

【解決手段】並列に配置される複数のゲート電極パターン10〜15を交互に、ダブルパターニングの第1の露光工程で形成する第1のパターン及び第2の露光工程で形成する第2のパターンとして設定し(ステップS1)、第1のパターンと第2のパターンとを並列に接続したトランジスタ対を含む回路をレイアウトすることで(ステップS2)、ダブルパターニングによるトランジスタの特性ばらつきが抑えられる。

(もっと読む)

半導体装置およびその製造方法

【課題】チップ面積の増加を抑えつつ、金属等からなるゲート電極を有するMISトランジスタと、抵抗体とを同一基板上に不具合なく形成する。

【解決手段】半導体装置は、半導体基板1上にそれぞれ設けられたMISトランジスタと抵抗素子とを備える。MISトランジスタは、活性領域1aと、活性領域1a上に設けられたゲート絶縁膜18と、ゲート絶縁膜18上に設けられたゲート電極19とを有する。抵抗素子40は、素子分離領域2上に設けられた抵抗体10を有しており、ゲート電極19の少なくとも一部は、抵抗体10よりも小さな抵抗率を有しており、活性領域1a上においてはゲート電極19の上面を覆っておらず、抵抗体10の上面を覆っている層間絶縁膜16がさらに設けられる。

(もっと読む)

半導体装置および半導体装置設計方法

【課題】半導体基板においてダミーパターンの配置密度を高める。

【解決手段】半導体基板104には、配線パターン102とダミーパターン106がレイアウトされる。配線パターン102の周囲にはマージン領域がレイアウトされ、マージン領域の周囲にダミー領域がレイアウトされる。このダミー領域に、複数のダミーパターン106がレイアウトされる。ダミーパターン106は、ダミー領域の延伸方向に配列される。マージン領域とダミー領域は、配線パターン102を基準として交互にレイアウトされる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性の高い半導体装置を実現する。

【解決手段】半導体装置100は、基板30と、基板30に埋め込まれた絶縁膜20と、絶縁膜20上に形成された複数の抵抗素子10と、を備えている。基板30は、複数の抵抗素子10を有する抵抗素子形成領域40において複数の凸部32を有している。複数の凸部32は、絶縁膜20に入り込んでおり、かつ上端が絶縁膜20の表面よりも低い。このため、信頼性の高い半導体装置を実現することが可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】TEGによる検査結果を容易に確認できるようにしつつ、TEGの占有面積を小さくする。

【解決手段】TEG群300は、第1テスト用パッド310、第2テスト用パッド312、及び複数のTEG(例えば第1TEG320、第2TEG340、及び第3TEG360)を有している。複数のTEGは、電気回路上、第1テスト用パッド310と第2テスト用パッド312の間に位置し、互いに直列又は並列に配置されており、かつ平面視で互いに重なっていない。本実施形態において、TEG群300を構成するTEGは、OBRICH(Optical Beam Induced Resistance Change)用のTEGである。

(もっと読む)

半導体集積回路装置

【課題】配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することを目的とする。

【解決手段】電極パッド113形成領域の、低誘電率膜より誘電率の高い配線層間膜からなる多層配線層領域において、ダミービアを形成しないことにより、配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することができる。

(もっと読む)

データ保持装置及びこれを用いた論理演算回路

【課題】マスクパターンの疎密に起因する強誘電体素子の特性ばらつきを適切に低減することが可能なデータ保持装置及び、これを用いた論理演算回路の提供。

【解決手段】データ保持装置において、不揮発性記憶部に含まれる複数の強誘電体素子X(素子幅m)は、各々よりも素子幅の小さいダミー素子Y(素子幅n、ただしn<m)によって包囲されている。これによってマスクパターンの疎密に起因するエッチングのローディング効果を抑制する事が可能となる。

(もっと読む)

半導体装置

【課題】容量素子を備え、電気的特性の安定化が可能な半導体装置を提供する。

【解決手段】半導体基体1上の配線層に形成されている配線と絶縁層とからなる容量素子10を備える。そして、容量素子10の形成領域内の半導体基体11上に形成されている導体パターンと、導体パターンの電位を固定するための電位固定端子28とを備える半導体装置を構成する。

(もっと読む)

1 - 20 / 390

[ Back to top ]