Fターム[5F038CD11]の内容

Fターム[5F038CD11]に分類される特許

1 - 20 / 45

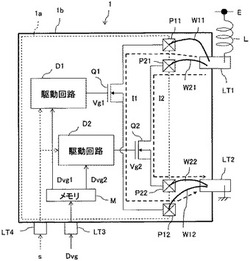

半導体装置

半導体装置および半導体装置の駆動方法

【課題】複数の出力トランジスタが並列接続された構成を備え、出力トランジスタを含む各電流経路間で分担電流を高精度に均一に揃えることができる半導体装置、および当該半導体装置の駆動方法を提供する。

【解決手段】互いに並列に接続された複数の出力トランジスタを備える半導体装置であって、出力トランジスタごとに設けられ第1の制御信号を供給する駆動回路と、第1の制御信号に含める出力トランジスタのコンダクタンスの情報を有するデータを記憶するメモリと、メモリにデータを入力するための第1の外部入力端子と、各駆動回路に出力トランジスタを1つずつ入れ替わり導通させる第2の制御信号を入力するための第2の外部入力端子とを備え、各駆動回路は、メモリに記憶されている駆動対象の出力トランジスタについてのデータを読み出して、コンダクタンスの情報を含む第1の制御信号を生成する。

(もっと読む)

半導体装置

【課題】ESD耐圧が向上した半導体装置を提供する。

【解決手段】半導体装置は、電源パッドと、電源用配線を有する所定回路と、電源パッドと電源用配線とを接続する第1配線と、所定電位に設定された第2配線と、第1静電保護素子と、第2静電保護素子と、を含む。第1静電保護素子は、第1配線の電位が第1の閾値になった場合に、第1配線から第2配線への電流経路を形成する。第2静電保護素子は、電源用配線と第2配線との間に設けられ、第1配線の電位が第2の閾値になった場合に、電源用配線から第2配線への電流経路を形成する。

(もっと読む)

半導体装置

【課題】周辺回路領域を整形された形状とすることによりチップ面積を縮小する。

【解決手段】Y方向に延在する複数のデータバスDBがピッチP1でX方向に配列されたメモリセル領域40と、対応する複数のデータバスDBにそれぞれ接続された複数のバッファ回路BCが設けられたバッファ領域61とを備える。バッファ領域61上においては、Y方向に延在する複数のデータバスDBがピッチP2でX方向に配列され、ピッチP2はピッチP1よりも小さい。本発明によれば、データバスDBの配列ピッチをバッファ領域上において縮小していることから、他の回路ブロックに割当可能な面積を十分に確保することが可能となる。これにより、当該回路ブロックの幅拡大や形状の変形が不要となることから、無駄な空きスペースが生じにくく、チップ面積を縮小することが可能となる。

(もっと読む)

半導体集積回路装置

【課題】ESD保護回路を備え外部端子数を効率よく配置できる半導体集積回路装置を提供する。

【解決手段】第1、第2電源電圧を供給する第1、第2電源パッドに対応した第1、第2電源セル、第1信号パッドに対応した入出力セル、第1電源電圧を供給する第1電源線、第2電源電圧を供給する第2電源線を有する。入出力セルは、信号入出力を行う回路、静電保護回路及び第1電源線と第2電源線との間に設けられた第1MOSを有する。第1電源セルは、第1電源パッドの正静電気に応答して第1MOSを一時的にオンにさせる時定数回路、第1電源パッドに向かう電流を流す一方向性素子を有する。第2電源セルは、第2電源パッドの正静電気に応答して第1MOSを一時的にオンにさせる時定数回路、第2電源パッドに向かう電流を流す一方向性素子を有する。第1MOSのゲートとウェルは時定数回路と接続される。

(もっと読む)

半導体装置、半導体装置のレイアウト装置、及び半導体装置のレイアウト方法

【課題】信号配線を自由にレイアウトすることのできる、半導体装置、半導体装置のレイアウト装置、及び半導体装置のレイアウト方法を提供する。

【解決手段】半導体装置は、主面及び裏面を有する基板と、前記主面上に設けられ、機能セル群が形成された機能セル層と、前記機能セル層上に積層された複数の配線層と、前記複数の配線層に設けられ、電源電圧を前記機能セル群に供給する、電源配線部と、前記基板を貫通する貫通ビア群とを具備する。前記電源配線部は、前記複数の配線層のうちの最下層に設けられた最下層電源配線群を有する。前記貫通ビア群は、前記裏面から前記最下層にまで伸びており、前記最下層において前記最下層電源配線群に接続される。前記最下層電源配線群は、分岐して伸びる部分を有している。

(もっと読む)

半導体装置

【課題】従来技術において、制御回路に発生する電源ノイズを出力バッファに影響させないようにするには、出力バッファと制御回路の電源ラインを別々に設ける方法があった。しかし、この方法には、電源・グランドピン数の増加、給電ラインインダクタンスの増加といった問題があった。

【解決手段】本発明では、上記課題である(1)電源・グランドピン数増加と(2)給電ラインインダクタンスの増加を生じることなく、制御回路で問題となるノイズが出力バッファに回り込まないような技術を提供する。具体的な手法は、(A)制御回路用のオンチップバイパスキャパシタンスを設け、AC的に制御回路と出力バッファの給電経路を切り分ける方法、と(B)給電経路の電気パラメータノイズの振動モードが過減衰になるような設計(抵抗の挿入)をする方法がある。

(もっと読む)

半導体装置

【課題】ESD放電経路におけるメタル配線の電流密度の許容値を高くとることが可能であり、また、配線抵抗を小さくすることが可能である半導体装置を提供する。

【解決手段】信号パッド(101)と、電源線(103)と、接地線(104)と、一端が信号パッド(101)と接続されたインダクタ(111)と、インダクタ(111)の他端と電源線(103)または接地線(104)との間に設けられた終端抵抗(112)と、インダクタ(111)の中間の第1位置(Aa)に接続された第1ESD保護素子(ESD_G)と、インダクタ(111)の中間の第1位置(Aa)とは異なる第2位置(Ab)に接続された第2ESD保護素子(ESD_V)とを備える。

(もっと読む)

低損失多層オンチップインダクタ

【課題】多層構造のオンチップインダクタ素子において、インダクタの表皮効果を低減してQ値を向上させる。

【解決手段】単一のインダクタ配線1から構成される、又は複数のインダクタ配線1を上下に積層して並列接続したものから構成されるインダクタ配線層を3層以上有し、各インダクタ配線層は上下に積層されて直列接続されており、最上層と最下層のインダクタ配線層を除く中間層の各インダクタ配線層の実効的な膜厚が、該最上層及び最下層のインダクタ配線層の実効的な膜厚よりも大きいことを特徴とする、半導体基板上絶縁膜中のオンチップインダクタである。

(もっと読む)

制御可能なサージ電流耐性を有するパワースイッチング素子

半導体スイッチング素子は、ワイドバンドギャップパワートランジスタと、前記パワートランジスタと並列に接続されたワイドバンドギャップサージ電流トランジスタと、前記サージ電流トランジスタを駆動するように構成された駆動トランジスタを含む。前記半導体スイッチング素子の、オン状態での出力電流のほぼすべては、前記パワートランジスタのドレイン−ソース電圧が第一の電圧範囲内にあるときには、前記パワートランジスタのチャネルを通って流れる。当該第一の電圧範囲は、例えば、通常動作中に期待されるドレイン−ソース電圧に対応し得る。その一方で、前記半導体スイッチング素子は、さらに、オン状態で、前記パワートランジスタのドレイン−ソース電圧が第二の(より高い)電圧範囲内にあるときには、出力電流が、前記サージ電流トランジスタ、および前記パワートランジスタのチャネルの両方を通って流れるように構成される。 (もっと読む)

表示パネルドライバ

【課題】必要な静電保護抵抗値を保ちつつ、出力特性を改善することができる出力回路を備えた表示パネルドライバを提供する。

【解決手段】表示パネルドライバが、第1及び第2アンプと、第1〜第n偶数出力ノードと(nは、2以上の整数)、第1〜第n奇数出力ノードと、表示パネルのデータ線にそれぞれに接続される第1及び第2出力パッドと、第1〜第nスイッチブロックと、第1〜第n偶数静電保護抵抗と、第1〜第n奇数静電保護抵抗とを具備する。第1〜第nスイッチブロックのうちの第iスイッチブロックは(iは1以上n以下の任意の整数)、第1及び第2アンプと第i偶数出力ノード及び第i奇数出力ノードとの間の接続関係を切り換えるように構成されている。第1〜第n偶数静電保護抵抗は、それぞれ、第1〜第n偶数出力ノードと第1出力パッドとの間に接続されており、第1〜第n奇数静電保護抵抗は、それぞれ、第1〜第n奇数出力ノードと第2出力パッドとの間に接続されている。

(もっと読む)

エレクトロマイグレーション対応のFETトランジスタ

【課題】 エレクトロマイグレーション対応の高性能FETレイアウトを提供する。

【解決手段】 電気コンタクト構造体が、その長さに沿って電流を分配する。電気コンタクト構造体は、n個の金属レベル上の複数のn個の金属矩形部を含む。1つの金属レベル上の矩形部の幅は、真下の金属レベル上の矩形部の幅と少なくとも同じ広さであり、かつ、これを垂直方向に覆う。1つの金属レベル上の矩形部の長さは、真下の金属レベル上の矩形部より短く、かつ、これと第1の端部において実質的に位置合わせされる。矩形部の第1の端部は実質的に位置合わせされる。本発明の例示的なFETトランジスタの構造部は、ソース及びドレイン端子、電気コンタクト構造体、両端部でゲート矩形部を接続するマルチレベルの金属リング、及び最小のものより広いゲート間間隔である。本発明は、例えば、エレクトロマイグレーション対応の高性能トランジスタに有用である。

(もっと読む)

半導体集積回路

【課題】 複数のチップが積層され、均一な電源供給が可能な半導体集積回路を提供する。

【解決手段】 第1の半導体集積回路チップと第2の半導体集積回路チップとを積層し、チップ間接続電極で互いに接続する。そして、第2の半導体集積回路チップのコア電源端子と、チップ間接続電極を介して、第1の半導体集積回路チップに形成されたコア回路にコア電源電圧を供給する。

(もっと読む)

半導体装置

【課題】銅めっき層をアンテナの導体に用いた、集積回路とアンテナが一体形成された半導体装置において、銅の拡散による回路素子の電気特性への悪影響を防止するとともに、密着性の良い銅めっき層を提供することを課題とする。また、集積回路とアンテナが一体形成された半導体装置において、アンテナと集積回路の接続不良に伴う半導体装置の不良を防止することを課題とする。

【解決手段】アンテナ101と集積回路100が一体形成された半導体装置において、アンテナ101として銅めっき層を用いるとともに、そのシード層107としてAg、Pd及びCuの合金を用い、バリア層116としてTiN又はTiを用いるものである。

(もっと読む)

配線接続構造

【課題】電源配線やグランド配線の断線のために駆動ICが表示パネルを駆動できなくなる可能性を低減することができる配線接続構造を提供する。

【解決手段】駆動ICのバンプを、電源配線に接続されるバンプ131のバンプグループ、バンプ151のバンプグループ、グランド配線に接続されるバンプ141のバンプグループ、およびバンプ161のバンプグループに分ける。さらに、各バンプグループ内で、バンプを複数のグループに分ける。そのグループ毎に、バンプを一本の電源配線またはグランド配線に接続される。これらの電源配線91,92,95,96やグランド配線93,94,97,98は、それぞれFPC71上の銅箔81〜88に接続される。1つのバンプグループに対応する銅箔は、FPC71上で一本の銅箔に接続される。

(もっと読む)

劣化診断回路及び半導体集積回路

【課題】単純な回路で構成される劣化診断回路及びIPコア化された劣化診断回路が組み込まれた半導体集積回路を提供する。

【解決手段】半導体集積回路10a内に設けられた実回路12の経年劣化による故障時期を予測する劣化診断回路13aであって、一定の周波数でパルス信号を出力する信号発生回路14と、実回路12と同時期に設けられ、信号発生回路14により出力されたパルス信号を通過させて出力する劣化診断対象回路16aと、信号発生回路14により出力されたパルス信号の立ち上がりから所定時間だけ遅れて立ち上がりかつ信号発生回路14により出力されたパルス信号と同じ周波数を有するクロック信号を生成するとともに、劣化診断対象回路16により出力されたパルス信号のタイミングとクロック信号のタイミングとを比較して劣化診断対象回路16aの劣化が発生したか否かを判定し、判定結果を実回路と外部との少なくとも一方に出力する劣化判定回路18とを備える。

(もっと読む)

半導体集積回路

【課題】パワー・トランジスタに流れる電流ルートを明確にすると共に、パワー・トランジスタに流れる電流の最適化を図ることにより、パワー・トランジスタへのダメージ又はストレスを低減し、信頼性に優れた半導体集積回路を提供する。

【解決手段】半導体集積回路は、パワー・トランジスタ(100A)と、パワー・トランジスタ(100A)の直上に形成され、複数の第1のバス(140〜142)と、複数の第2のバス(150〜152)と、複数の第1のバス(140〜142)及び複数の第2のバス(150〜152)の各々に1つずつ設けられたコンタクト・パッド(304)とを備える。複数の第1のバス(140〜142)と複数の第2のバス(150〜152)は、外部の接続部材(307)に近い側に位置するものから遠くに位置するものへと順に面積が小さくなるように形成されている。

(もっと読む)

半導体集積回路及びその製造方法

【課題】パワー・トランジスタに流れる電流ルートを明確にすると共に、パワー・トランジスタに流れる電流の最適化を図ることにより、パワー・トランジスタへのダメージ又はストレスを低減し、信頼性に優れた半導体集積回路を提供する。

【解決手段】半導体集積回路は、半導体基板上(100)に形成されたパワー・トランジスタ(100A)と、パワー・トランジスタ(100A)の直上に形成され、パワー・トランジスタの第1の電極及び第2の電極として機能する複数の第1の金属パターン及び複数の第2の金属パターンと、複数の第1の金属パターンのうち対応する第1の金属パターンと電気的に接続する複数の第1のバス(130,131)と、複数の第2の金属パターンと電気的に接続する単一の第2のバス(150)と、複数の第1のバス(130,131)及び単一の第2のバス(150)に1つづつ設けられたコンタクト・パッド(304)とを備える。

(もっと読む)

半導体装置

【課題】チップ面積を減少させることができる半導体装置を得る。

【解決手段】本発明に係る半導体装置は、半導体基板と、半導体基板の表面の一部に形成された動作層と、動作層上に形成されたゲート電極と動作層にオーミックコンタクトされたソース電極及びドレイン電極と、ソース電極と接地との間に並列接続された第1の容量及び第1の抵抗とを備え、第1の容量は、ソース電極と、ソース電極上に形成された第1の絶縁膜と、第1の絶縁膜上に形成され、接地された第1の上部電極とから構成される。

(もっと読む)

半導体集積回路

【課題】マクロセルを有する半導体集積回路の面積を抑える。

【解決手段】半導体集積回路であって、回路素子を複数有するマクロセルと、前記マクロセルに第1の電位を供給する第1のマクロセル用電源配線と、前記第1のマクロセル用電源配線と同一の配線層に配置され、前記マクロセルに第2の電位を供給する第2のマクロセル用電源配線とを備える。前記第1及び第2のマクロセル用電源配線は、前記マクロセル上に配置されており、前記第2のマクロセル用電源配線は、前記第1のマクロセル用電源配線の延長方向である第1の方向に延びるように配置されている。

(もっと読む)

1 - 20 / 45

[ Back to top ]