Fターム[5F038DF05]の内容

半導体集積回路 (75,215) | 集積回路機能及び回路ブロック構成 (8,544) | 特定機能回路(単一機能) (5,304) | メモリ (1,792)

Fターム[5F038DF05]に分類される特許

1,781 - 1,792 / 1,792

検査パッド構造を有する集積回路および検査方法

半導体装置(10)は、ワイヤボンディングのために周囲に多数のボンド・パッド(24)を有する。半導体装置(10)は、モジュール(12)およびその他の回路を有するが、モジュール(12)は検査のために他の回路よりも遥かに長い時間を必要とする。比較的少数のボンド・パッド(20)、モジュール・ボンド・パッド(20)が、少なくとも部分的に、内蔵自己検査(BIST)(16)回路を有する半導体装置によるモジュール検査のために必要である。これらのモジュール・ボンド・パッド(22)の機能性は、半導体装置(10)の上面上および内部に二重化されており、モジュール検査パッド(22)は周辺のボンド・パッド(24)よりも遥かに大きい。検査のために大きなパッド(22)を有することにより、プローブ・ニードルを長くすることができ、したがって並行検査機能が向上する。機能性の二重化は、モジュール・ボンド・パッド(20)およびモジュール検査パッド(22)が互いに短絡しなくてよいように、検査パッド・インターフェースを介して達成する。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

半導体デバイス(低電力処理アイランド構造)

【課題】 複数の電子構造を含む集積回路による電力消費を低減する構造を提供する。

【解決手段】 半導体デバイス上のデータを処理するための構造は、半導体デバイス(18)内に形成された入力アイランド(14)、処理アイランド(8)、および出力アイランド(12)を含む。入力アイランドは、指定されたデータ量を受け入れ、指定されたデータ量を受け入れた後に処理アイランドに電力を供給するための第1の指定された電圧を与えるための手段をイネーブルするように構成されている。処理アイランドは、第1の指定された電圧によって処理アイランドに電力を供給した後に入力アイランドからの指定されたデータ量を受信し処理するように構成されている。出力アイランドは、第2の指定された電圧によって電力を供給されるように構成されている。処理アイランドは、更に、第2の指定された電圧による前記電力供給に基づいて出力アイランドに処理済みデータを送信するように構成されている。出力アイランドへの処理済みデータの送信が完了した後に、第1の指定された電圧がディスエーブルされ、これによって処理アイランドから電力を取り除くように構成されている。

(もっと読む)

縦列アーキテクチャ

複数の列に配列される回路を有する集積回路(IC)が開示される。ICの列は、ICの第1の端部から第2の端部へ延在する、同じ種類の実質的に一連の位置合せされた回路素子である。加えて、異なるタイプの回路素子を有する中央列があり得る。  (もっと読む)

(もっと読む)

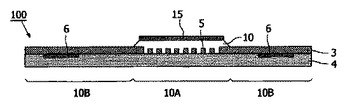

柔軟な半導体デバイス及び識別ラベル

集積回路(5)と、その集積回路(5)の相互接続構造に組み込まれ、又は直接結合されるアンテナ(6)とを備える柔軟なデバイス(100)が与えられる。相互接続構造は、アクティブ領域の外側に広がる。電気的に絶縁する又は誘電性のある層(4)がアンテナ(6)と集積回路(5)との両方に対する支持層として存在する。基板(10)は、集積回路(5)のアクティブ領域(10A)の外側の非シリコン領域(10B)で除去される。この除去は、単結晶シリコンの基板の使用に結び付けられることができる。柔軟なデバイスは、識別ラベル及びセキュリティペーパへの一体化にとても適しており、一時的に付けられたキャリア基板を用いて製造されることができる。  (もっと読む)

(もっと読む)

シグナルインテグリティ自己テストアーキテクチャ

少なくとも1つのモジュールを有する集積回路装置であって、該モジュール内の温度、給電ノイズ及びクロストーク等のような装置パラメータをモニタするのに適した少なくとも1つの関連するモジュールモニタを組み込んでいるモジュールを有する集積回路装置をテストするのに適した方法が、記載されている。  (もっと読む)

(もっと読む)

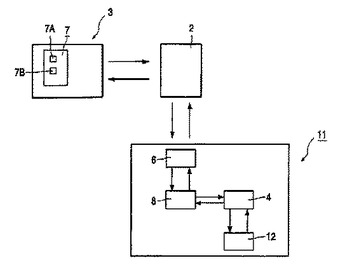

半導体デバイス、認証方法およびシステム

本発明の半導体デバイス(11)は回路と保護構造(50)とを備える。本発明の半導体デバイス(11)は、第1および第2のセキュリティ素子(12A、12B)と、入力および出力(14、15)とを備える。セキュリティ素子(12A、12B)は、異なる第1および第2のインピーダンスをそれぞれ有する。このデバイスはさらに、測定手段、処理手段および接続手段を備える。処理手段は、受け取られた第1の情報を特定の測定プログラムに変換する。これによって、デバイス(例えばスマートカード)のオーセンティシティをチェックし、またはアイデンティティを確立するために、デバイス(11)および読取り装置中にチャレンジ−レスポンス機構が実装される。  (もっと読む)

(もっと読む)

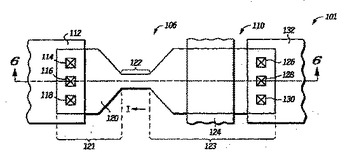

フューズ及びその形成方法

アクティブフューズはアクティブフューズ構造(120)を備え、この構造を使用して可変抵抗体(106)及び選択トランジスタ(110)の双方を形成する。一の実施形態では、アクティブフューズ構造は、半導体基板(140)の活性領域(160)の一部に形成され、選択ゲート(124)はアクティブフューズ構造の一方の端部(123)の上に配置されてアクティブフューズへの書き込みに使用する一体型選択トランジスタ(110)を形成する。共有型のアクティブフューズ構造を活性領域の内部に使用することによって、面積要件を縮小し、かつ検出マージンを大きくすることができる。  (もっと読む)

(もっと読む)

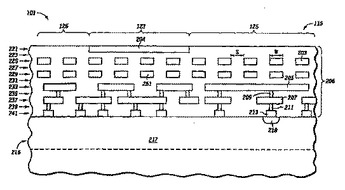

半導体の整合補助部

半導体デバイス用の整合補助部(115)に関する。整合補助部は、高い反射度を有する領域(123)と、低い反射度を有する隣接領域(125)とを備える。低い反射度を有する領域には、半導体デバイスの相互接続層(225)に配置され、かつ半導体デバイスの能動回路(218)の上方に配置されている、1層以上のタイル(203)が含まれる。一部の例では、整合補助部のタイルの走査方向への間隔は、整合補助部の走査に使用される光(例えば、レーザ光)の波長より短い。他の例では、整合補助部のタイルの走査方向への幅が、整合補助部の走査に使用される光の波長より短い。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】近年、MOSトランジスタのウェル(基板)に順方向バイアス電圧を印加することが注目されているが、温度変化に対して最大限の順方向バイアス電圧を得ることが難しく、そのための回路構成や占有面積も問題になってきている。

【解決手段】第1導電型(p+;n+)のソース電極Sおよびドレイン電極Dとゲート電極Gとを有し、第2導電型(n;p)のウェル10;20に形成されてなるMISFET1;2を備える半導体集積回路装置であって、前記ウェル10;20の電位Vbp;Vbnを、前記MISFET1;2のソース電極Sおよび該ウェル10;20により形成されるダイオード11;21に対して所定電流Ibp;Ibnを順方向に流すことにより生成する基板バイアス回路110;111〜113を備えるように構成する。

(もっと読む)

昇圧電位発生回路及び制御方法

【課題】 半導体メモリにおいて、外部電源電圧が低下しても、半導体メモリ内部では、高速動作を可能にすると共に、小型化をも可能にする昇圧電位発生回路を提供する。

【解決手段】 容量MOSトランジスタとトランスファMOSトランジスタとを備え、メモリセルを含むDRAMに使用される昇圧電位発生回路において、容量MOSトランジスタのゲート絶縁膜を、メモリセルを構成するMOSトランジスタのゲート絶縁膜の膜厚よりも薄い膜厚にすることにより、小面積で大容量の昇圧電位発生回路を実現する。この場合、トランスファMOSトランジスタのゲート絶縁膜の厚さを容量MOSトランジスタのゲート絶縁膜の厚さを同等以上に厚くすることが好ましい。

(もっと読む)

半導体集積回路、当該半導体集積回路を搭載した非接触型情報媒体、及び半導体集積回路の駆動方法

【課題】 データが重畳された搬送波より駆動電源を得る半導体集積回路において、得られた電源電圧が過電圧状態となった場合でも誤判別なくデータを復調することができ、また、搬送波から供給される電源を効率的に利用することができる半導体集積回路等を提供する。

【解決手段】 電源回路111として二電圧整流回路を用いるとともに、データの復調に用いる電圧値の高い側の電源(VDDH)が所定の電圧値以上にならないように制御する電圧調整回路112に、抵抗141及び容量素子142を設け、搬送波の振幅が変化することによりVDDHの電圧値が変化した場合に、基準電圧としてレギュレータ回路1121に入力される電圧値を変化させるようにする。

(もっと読む)

1,781 - 1,792 / 1,792

[ Back to top ]