Fターム[5F038EZ10]の内容

Fターム[5F038EZ10]に分類される特許

1 - 20 / 439

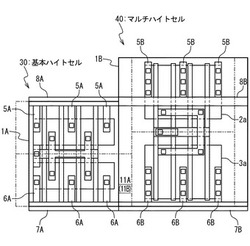

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

半導体装置、パラメータ最適化方法、及びプログラム

【課題】トランジスタの容量の各成分や配線容量を分離してパラメータを最適化することが可能な半導体装置、パラメータ最適化方法、及びプログラムを提供すること。

【解決手段】MOSトランジスタから構成されたプリミティブゲート回路11aを奇数段でリング状に結合した第1リングオシレータ部11の各前記プリミティブゲート回路の出力部と電気的に接続された負荷部12となる第1配線を有する配線負荷パターンと、第2リングオシレータ部の各プリミティブゲート回路の出力部が第2配線を介して負荷部となるMOSトランジスタのゲートに電気的に接続された複数のゲート負荷パターンと、第3リングオシレータ部の各プリミティブゲート回路の出力部が第3配線を介して負荷部となる拡散層に電気的に接続された複数の拡散層負荷パターンと、を備え、複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、複数の拡散層負荷パターンは、パターンごとに容量負荷が異なる。

(もっと読む)

安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路を備える半導体装置を提供する。

【解決手段】基板10と、基板上に配置され、ガン発振である高周波負性抵抗発振の発振周波数において負性抵抗を生ずる能動素子140と、基板上に配置され、能動素子のドレイン端子電極と出力端子との間に接続され、負性抵抗の絶対値に等しい抵抗値を有する抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とからなる安定化回路120とを備え、安定化回路120は、発振周波数に、インダクタンスLとキャパシタンスCからなる共振周波数を同調することによって、発振周波数において、抵抗Rによって負性抵抗をキャンセルする半導体装置。

(もっと読む)

シミュレーション装置およびシミュレーション方法

【課題】ESD保護素子を有する半導体回路の回路シミュレーションを高速かつ精度よく行うことができるシミュレーション装置を提供する。

【解決手段】ESD保護素子を有する半導体回路の動作検証を行うシミュレーション装置は、ESD保護素子の等価回路のパラメータファイルを作成する第1のパラメータファイル作成部と、半導体回路内のESD保護素子以外の内部回路のパラメータファイルを作成する第2のパラメータファイル作成部と、作成したパラメータファイルを記憶するパラメータファイル記憶部と、記憶したパラメータファイルを選択するパラメータファイル選択部と、選択したパラメータファイルを利用して半導体回路のネットリストを作成するネットリスト作成部と、ネットリストに基づいて半導体回路の動作検証を行うシミュレーション実行部とを備える。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の制御された酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

検証装置、検証方法及びプログラム

【課題】検証する範囲を少なくして、検証コストや検証時間の増大を抑制する。

【解決手段】抽出部12が、第1のクロック信号で動作する回路部21と、第2のクロック信号で動作する回路部22とを含む検証対象回路(論理回路20)から、ハンドシェイクの手順に従って回路部21と回路部22間でのデータの送受信を行うハンドシェイク部23を抽出し、検証部13が抽出されたハンドシェイク部23の信号が、その手順を満たすかを検証し、手順を満たさない信号があるとき、回路部21と回路部22のうち当該信号を出力する側で、当該信号が手順を満たさなくなる条件が回路動作時に起こり得るか検証する。

(もっと読む)

クロック設計方法、クロック設計プログラム

【課題】半導体集積回路のクロック設計において、異なる2種類のクロック間の「セル遅延と配線遅延の比率α」の差を抑制する。

【解決手段】半導体集積回路は、第1クロック(CLK1)が供給される第1素子群と、第1クロック(CLK1)と異なる第2クロック(CLK2)が供給される第2素子群と、を備える。クロック設計方法は、第1クロック(CLK1)に関するクロックツリーシンセシスを実施することによって、第1クロックツリー構造10を作成するステップと、第1クロックツリー構造10の少なくとも一部を流用することによって、第2素子群に第2クロック(CLK2)を供給する第2クロックツリー構造20を作成するステップと、を含む。

(もっと読む)

電源電圧設定方法及び電源電圧設定プログラム

【課題】チップごとに適正な電源電圧を設定する。

【解決手段】チップのレイアウトデータ20からクリティカルパスのゲート遅延と配線遅延の遅延比を抽出する(ステップS1,S2)。チップのモニタ回路で実測されたゲート遅延及び配線遅延を、その遅延比に基づき合成して第1遅延値を生成し(ステップS3)、モニタ回路のシミュレーションで得られるゲート遅延及び配線遅延を、その遅延比に基づき合成して第2遅延値を生成する(ステップS4,S5)。このようにゲート遅延、配線遅延、クリティカルパスでの遅延比が考慮された第1遅延値及び第2遅延値に基づいて、チップに適用するチップ電源電圧を設定する(ステップS7)。

(もっと読む)

スタンダードセル回路、半導体集積回路、及び半導体集積回路装置

【課題】スタンダードセル回路のレイアウト面積を削減する。

【解決手段】配線導体Laは電源電圧VDDaを出力する電源に接続される。レギュレータ6aは、配線導体Laからの電源電圧VDDaを電源電圧VDDaより低い電源電圧VDDbに変換し、配線導体Lbを介してレベルシフタ2−1〜2−3,3,及びスタンダードセル4に出力する。レベルシフタ2−1は、入力されるデータの電圧レベルを電源電圧VDDaの電圧レベルから電源電圧VDDbの電圧レベルに電圧シフトしてスタンダードセル4に出力する。レベルシフタ3は、スタンダードセル4からの出力信号の電圧レベルを電源電圧VDDbの電圧レベルから電源電圧VDDaの電圧レベルに電圧シフトし、出力端子Tqを介して出力する。

(もっと読む)

半導体集積回路及びその設計方法

【課題】半導体集積回路の外部端子としてTRSTがなくても、論理シミュレーションの際に、タップコントローラのステートを確定する。

【解決手段】タップコントローラ2は、リセット端子(端子p4)を有し、回路部3は、タップコントローラ2における状態遷移を制御するステート制御信号と、クロック信号を入力し、ステート制御信号とクロック信号に応じて、リセット端子p4にリセット信号を供給することで、タップコントローラ2のステートを確定する。

(もっと読む)

半導体集積回路,および,半導体集積回路の検査方法

【課題】故障検査のために観測用フリップフロップ回路を配置することなく,故障検査を可能とする半導体集積回路,その検査方法を提供する。

【解決手段】第2の論理回路51の試験の際に試験モードを示す制御信号TSMが,故障検査用回路41に入力され,この試験モードに対応するテスト値が,論理回路51に入力されると,故障検査用回路41により,論理回路51の出力論理が,論理回路13に対応するフリップフロップ回路14に入力される。さらに,通常モード時に,論理回路13の出力論理が,故障検査用回路41により,論理回路13に対応するフリップフロップ回路14にそのまま入力される。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

検波器及び受信機

【課題】低電圧、低電流、或いは低電力といった条件下でも使用することが可能な検波器を提供する。

【解決手段】検波器は、信号入力端子に接続された第1導電型の第1の半導体領域と、信号出力端子に接続された第2導電型の第2の半導体領域であって、第1の半導体領域に接して位置する第2の半導体領域と、交流的に接地された第1導電型の第3の半導体領域であって、第1の半導体領域から離間し且つ第2の半導体領域に接して位置する第3の半導体領域と、一端が第2の半導体領域に接続され、他端が交流的に接地された第1の抵抗素子と、を含む。

(もっと読む)

トンネル電流回路

【課題】消費電力の少ない基準電圧を発生する回路を、従来並みのサイズで提供することを目的とする。

【解決手段】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、

前記差電圧が印加される第一のトンネル電流素子と、

第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、

前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流す手段によって、

上記「差電圧に比例する電圧」を発生させることを特徴とする。

(もっと読む)

混合器、送信機及び通信システム

【課題】低電圧、低電流、或いは低電力といった条件下でも使用することが可能な混合器、送信機及び通信システムを提供する。

【解決手段】混合器は、交流的に接地された第1導電型の第1の半導体領域と、第1の信号入力端子に接続された第2導電型の第2の半導体領域であって、第1の半導体領域に接して位置する第2の半導体領域と、第1の信号出力端子に接続された第1導電型の第3の半導体領域であって、第1の半導体領域から離間し且つ第2の半導体領域に接して位置する第3の半導体領域と、第2の半導体領域上に位置する第1の絶縁膜と、第2の信号入力端子に接続された第1の導電体膜であって、第1の絶縁膜上に位置する第1の導電体膜と、を含む。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】半導体集積回路の面積を増大させることなく、配線性のよいテスト専用回路の電源遮断を実現する半導体集積回路を提供する。

【解決手段】テスト実行時のみ動作するテスト専用回路を有する半導体集積回路1であって、当該半導体集積回路1の内部回路領域(内部制御回路部100)に電源を供給する通常電源(通常動作用電源)104と、当該内部回路領域の全面にメッシュ状に配線され、テスト専用回路に電源供給するテスト用電源103と、テスト用電源103と通常電源104とを接続及び遮断して、通常電源104からテスト用電源103への電源供給を制御する電源遮断スイッチ109と、を備える。

(もっと読む)

半導体集積回路装置のレイアウト設計方法

【課題】チップサイズの増大を抑制できる半導体集積回路装置のレイアウト設計方法を提供する。

【解決手段】外部電源電圧が供給される第一電源線と第一電源線にスイッチとなる第二電源ドライバを介して接続される第二電源線とを備えた、SCRC方式を採用した半導体集積回路装置において、第二電源ドライバのレイアウト面積の増大を抑制するために、半導体集積回路装置の全回路を機能別回路に分割し、機能別回路領域毎に、SCRC方式による制御対象の回路であるSCRC使用動作回路のトランジスサイズに応じて第二電源ドライバとして用いるMOSトランジスタのサイズを決定する。

(もっと読む)

1 - 20 / 439

[ Back to top ]