Fターム[5F043AA14]の内容

ウェットエッチング (11,167) | 被エッチング体 (2,299) | 半導体基板以外の半導体層 (313) | 単層構造 (281) | 3−5族 (163) | Ga−As系 (23)

Fターム[5F043AA14]に分類される特許

1 - 20 / 23

半導体装置の製造方法

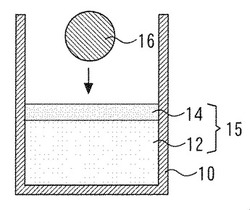

【課題】本発明は、Br−アルコール液を有するエッチング液のエッチングレートを安定させることができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本願の発明に係る半導体装置の製造方法は、Brをアルコールで希釈した溶液に、該アルコールよりも比重が小さく、かつ該アルコールに難溶解性の液体である封止液を加えたエッチング液に、ウエハを浸漬させて該ウエハをエッチングするエッチング工程を備えたことを特徴とする。

(もっと読む)

エッチング液組成物およびエッチング方法

【課題】エッチングにより、適切に、エッチング対象物の表面に凹凸形状を形成して粗面化を行うことができるエッチング液組成物を提供する。

【解決手段】エッチング液組成物は、エッチング対象物の表面16をエッチングして凹凸形状を形成するエッチング液組成物であって、有機酸、有機酸塩、無機酸、無機酸塩、キレート剤、界面活性剤、糖アルコール類、フェノール類、アゾール類、および複素環化合物からなる群から選択される少なくとも一つと、酢酸と、フッ化水素酸と、硝酸とを含む。

(もっと読む)

電界効果型トランジスタ

【課題】実用上十分なプロセスマージンを備える状態で、リーク電流の増大およびキャリア濃度の低下を招くことなく、ゲート電極とチャネル層との距離が短縮できるようにする。

【解決手段】InPからなる基板101の上に形成された電子供給層102と、電子供給層102の上に形成されたスペーサ層103と、スペーサ層103の上に形成されたチャネル層104と、チャネル層104の上に形成された障壁層105とを備え、障壁層105は、GaおよびAlの少なくとも1つと、Inと、Pとを含んだアンドープの化合物半導体から構成し、InPよりショットキー障壁高さが高いものとされている。

(もっと読む)

光集積素子の製造方法

【課題】パッシブ素子の特性の設計値からの低下を抑制することができる光集積素子の製造方法を提供すること。

【解決手段】基板上に、活性コア層を含む半導体積層構造で形成された、アクティブ素子を形成するためのアクティブ領域と、パッシブコア層を含む半導体積層構造で形成された、パッシブ素子を形成するためのパッシブ領域とを形成し、アクティブ領域とパッシブ領域とに被覆部と開口部とを有する第1エッチングマスクを形成し、アクティブ領域およびパッシブ領域において開口部からドライエッチングを行い、アクティブ領域にアクティブ素子のアクティブメサ構造を形成するとともにパッシブ領域にパッシブ素子のパッシブメサ構造を形成し、パッシブ領域に第2エッチングマスクを形成し、パッシブメサ構造を第2エッチングマスクにて保護しながらアクティブメサ構造をウェットエッチングする、ことを含む。

(もっと読む)

光電素子及びその製造方法

【課題】本発明は光電素子及びその製造方法を提供する。

【解決手段】本発明による光電素子であって、表面及び表面と垂直する法線方向を有する基板と、基板の表面に位置して表面と接触する第一半導体層と、第一半導体層と基板の表面の間に位置する少なくとも一つの空洞構造とを有し、少なくとも一つの空洞構造は幅と高さを有し、幅は空洞構造における表面に平行する方向の最大寸法であり、高さは空洞構造における法線方向に平行する方向の最大寸法であり、高さは幅より小さい。

(もっと読む)

エッチング液組成物およびエッチング方法

【課題】特殊な技術を用いることなく、LEDの光取り出し面を構成する半導体膜の表面を、効率よくエッチングして粗面化(凹凸化)することが可能なエッチング液組成物および該エッチング液組成物を用いたエッチング方法を提供する。

【解決手段】無機酸と、金属化合物とを含む組成とする。

さらに、有機酸、有機酸塩、無機酸塩、界面活性剤のいずれかを含む組成とする。

さらに、無機酸として、塩酸、リン酸、硫酸、硝酸のいずれかを含む組成とする。

また、金属化合物として、鉄系化合物を用いる。

有機酸および有機酸塩として、モノカルボン酸、ポリカルボン酸、オキシカルボン酸、ホスホン酸、スルホン酸およびその塩からなる群より選ばれる少なくとも1種を用いる。

本発明のエッチング液組成物を用いて、AlGaInP膜、AlGaAs膜、GaAsP膜のいずれか半導体膜をエッチングし、表面を粗面化する。

(もっと読む)

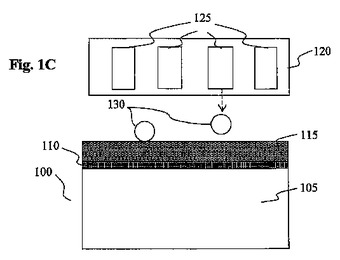

半導体薄膜の製造方法及び半導体装置の製造方法

【課題】半導体薄膜を基板上に形成した後剥離する方法において、剥離のためのエッチング液の浸透速度が高く、エッチング速度の均一性を高め、短時間で良好な半導体薄膜を得ることができるようにする。

【解決手段】複数の半導体薄膜(20)が基板(11)上にあるときに、複数の半導体薄膜(20)を互いに連結して支持するための、感光性のシート状部分(101)を有する連結支持体(100)を設ける。連結支持体(100)のシート状部分(101)を半導体薄膜(20)の上に設けた後、シート状部分(101)に貫通孔(103)を形成する。貫通孔(103)が、エッチング液を少なくとも基板(11)の面に垂直な方向に通過させる。これにより、複数の半導体薄膜(20)を基板(11)から剥離する。

(もっと読む)

エピタキシャルリフトオフを用いたフレキシブル光起電力デバイスの製造方法、およびエピタキシャル成長に用いる成長用基板の一体性を保持する方法

エピタキシャルリフトオフを用いる、フレキシブル光電(PV)デバイス等の感光性デバイスの製造方法が開示される。同様に、成長用基板を有する構造を含むフレキシブルPVデバイスを製造する方法が開示され、この方法では、保護層の選択的エッチングにより、再利用に好適な平滑な成長用基板が得られる。 (もっと読む)

半導体発光装置の製造方法および半導体発光装置

【課題】本発明は、半導体結晶内部からの光取り出し効率を向上させることにより、光出力を高めた半導体発光装置の製造方法および半導体発光装置を提供することを目的とする。

【解決手段】発光層2と、Ga(1−x)AlxAs層(0≦x<0.8)を含み発光層から放出された光を外部に取り出す表面層8と、を有する半導体積層体を、0℃未満の液温に保持した硝酸水溶液に浸漬して表面層の表面を粗面化することを特徴とする半導体発光装置の製造方法が提供される。

(もっと読む)

エッチング液及び半導体装置の製造方法

【課題】V族として砒素を含むIII−V族化合物半導体を安定したエッチングレートでエッチングすることができるエッチング液を得る。

【解決手段】V族として砒素を含むIII−V族化合物半導体のエッチングに用いるエッチング液であって、RをCnF2n+l(nは8を除く正の整数)とし、XをNH4+,K+,H+,Na+の何れか1つとして、RSO3X,RCOOX,(RSO2)2NXの何れか1つと酸又はアルカリを含む。

(もっと読む)

化合物半導体装置とその製造方法

【課題】

隣接するAs系半導体層からのAsの拡散を防止できるP系化合物半導体層を成長する。

【解決手段】

化合物半導体装置の製造方法は、(a)化合物半導体基板上方に、第2のAs系化合物半導体層、第3のAs系化合物半導体層を形成する工程と、(x)第3のAs系化合物半導体層の上に、As濃度5×1017atoms/cm3〜3×1019atoms/cm3の範囲のAsをドーピングしつつ、V族元素がPである第1のP系化合物半導体層を形成する工程と、(y)第1のP系化合物半導体層の上にV族元素がAsである第1のAs系化合物半導体層を形成する工程と、を含む。

(もっと読む)

半導体の形成方法

【課題】エッチング、試験を繰り返し停止、実行する工程を省略可能とする半導体の形成方法の提供。

【解決手段】ソース電極12とドレイン電極14の下にGaxIn1-xAsのドープキャップ層16を配置し、キャップ層開口部38を提供する。GaxIn1-xAsの非ドープ抵抗層18を上記キャップ層16の下に配置し、第一の幅W1をもち上記キャップ層開口部38と位置の合った抵抗層開口部38を画定する。AlyIn1-yAsのショットキー層20を上記抵抗層18の下に配置する。非ドープチャネル層28を上記ショットキー層20の下に配置する。上記抵抗層開口部38直下の上記ショットキー層の上部表面42により、第一の幅W1よりも小さな第二の幅W2をもつリセス44ができる。ゲート電極22は、上記ショットキー層20の上記リセスW2の底部表面48と接触する。

(もっと読む)

選択された材料のパターン化されたエッチング法

加工されるべき部分が予め定められたパターンに制限される表面加工は、(a)加工されるべき表面の領域であって、前記予め定められたパターンの部分を少なくとも覆う領域上に第一の試薬の層を提供する工程と;(b)前記表面を加工するために必要とされる更なる試薬である一つ以上の更なる試薬を提供する工程と;(c)前記予め定められたパターンに従って加工されるべき領域上に少なくとも一つの更なる試薬を塗布する工程と、により達成され、それにより、第一の試薬は予め定められたパターンの部分のみにおいて表面を加工すべく、一つ以上の更なる試薬と反応する。同加工は、二つ以上の成分を有するエッチャントが使用されるエッチングに特に適用可能である。その場合、少なくとも第一のエッチャント成分は表面上に適用され、かつ少なくとも一つの更なるエッチャント成分が予め定められたパターンに適用される。  (もっと読む)

(もっと読む)

半導体薄膜の製造方法及び半導体装置の製造方法

【課題】半導体薄膜を基板上に形成した後剥離する方法において、剥離のためのエッチング液の浸透速度が高く、エッチング速度の均一性を高め、短時間で良好な半導体薄膜を得ることができるようにする。

【解決手段】半導体薄膜(20)が基板(11)上にあるときに、複数の半導体薄膜(20)を互いに連結して支持するための連結支持体(90)を設ける。連結支持体(90)は、シート状部分(91)と、シート状部分(91)と半導体薄膜(20)との間に空隙を設けるためのスペーサ部(92)とを備えており、この隙間(20)が、基板(11)の面に平行な方向にエッチング液を通過させる。

(もっと読む)

III−V族半導体基板からのバルク金属汚染の除去方法

【課題】III−V族半導体基板からバルク金属汚染を除去するための単一工程の方法を提供する。

【解決手段】該方法は、金属汚染したIII−V族半導体基板を、体積比x:y H2SO4:H2O2(xは3〜9、yは1)を有する硫酸および過酸化物の混合物の中に浸漬することを含む。本発明の実施形態に係る方法を用いてIII−V族半導体基板を処理した後、バルク金属汚染は、基板からほぼ完全に除去できるとともに、処理後の基板の表面粗さは、2μm×2μmの表面グリッドに関して0.5nmRMS未満とすることができる。本発明は、半導体デバイスを製造する更なる処理ステップを実施する前に、本発明の実施形態に係るバルク金属汚染を除去する方法を用いて、半導体デバイスを製造するための方法を提供する。

(もっと読む)

半導体レーザ素子の製造方法および半導体レーザ素子

【課題】リッジ部の加工精度を改善でき、したがってキンクの発生を十分に抑制でき高出力動作が可能な半導体レーザ素子およびその製造方法を提供する。

【解決手段】この半導体レーザ素子の製造方法では、エッチングモニタ用開口部117で反射する光の反射干渉波形をモニタし、エッチングマーカ層110を利用してドライエッチング工程の終点を検出し、ドライエッチングを停止しているので、従来の時間制御法に比べて、より深くまで精度良くドライエッチングを続けることができる。さらに、このドライエッチング工程に続くウエットエッチング工程において、エッチングストップ層108を利用してウエットエッチングを行うので、リッジ部120の高さを精密に制御できると共に、等方的に進むウエットエッチングの時間を短縮できる。

(もっと読む)

発光素子の製造方法

【課題】AlGaAs発光素子において光取り出し面に面粗し処理を均一に施すことができ、ひいては面粗し状態にムラの生じにくい発光素子の製造方法を提供する。

【解決手段】 酢酸と弗酸と硝酸とヨウ素と水とを、その合計が90質量%以上となるように含有し、かつ酢酸と弗酸と硝酸とヨウ素との合計質量含有率が水の質量含有率よりも高い面粗し用エッチング液FEAにより(100)面からなるp型AlGaAs光取出層20に面粗し処理を施す。そして、その面粗し用エッチング液FEAによる面粗し工程に先立って、AlGaAsからなる積層体の第一主表面(主光取出領域)を、硫酸過酸化水素水溶液からなる前処理液と接触させて前処理を行なうことにより、面粗しにより得られるウェーハの突起形成状態にムラが生じることを効果的に防止することができる。

(もっと読む)

レーザー加工装置

【課題】ウェーハにレーザー光線を照射することにより個々のチップに分割した後、加工歪みを除去するため、別途設けたエッチング装置に搬送することなく同一装置内で直ちにエッチング処理ができるレーザー加工装置を提供する。

【解決手段】ウェーハを保持するチャックテーブル3と、レーザー光線を照射しウェーハを分割するレーザー光線照射手段4と、チャックテーブルの送り機能である加工送り手段と割り出し送り手段と、を具備するレーザー加工装置であって、レーザー加工後のウェーハをエッチング処理するエッチング手段としての機能とエッチング処理後のウェーハを洗浄する洗浄手段としての機能とレーザー加工前のウェーハの加工面に保護膜を被覆する保護膜被覆手段としての機能を備えたエッチング兼洗浄兼保護膜被覆手段7と、ウェーハをチャックテーブル3からエッチング兼洗浄兼保護膜被覆手段7に搬送する第2のウェーハ搬送手段17を具備する。

(もっと読む)

半導体素子の製造方法およびこの方法に使用されるエッチング液

【課題】選択リセスエッチング工程を含む半導体素子の製造方法を簡略化し、安定的に高品質な半導体素子を製造することを目的とする。

【解決手段】少なくとも、InGaAs層とInAlAs層とが積層された構造を有する半導体基板を用いる半導体素子の製造方法において、

InAlAs層上に積層されたInGaAs層をエッチングする工程を含み、且つ該工程で用いられるエッチング液に、安息香酸と過酸化水素水の混合溶液からなる混合溶液を用いることを特徴とする半導体素子の製造方法である。

(もっと読む)

半導体ウェハ裏面粗さ評価方法及び半導体ウェハ

【課題】 ラッピング後エッチングした半導体ウェハ裏面の粗さを短時間で客観的に評価する方法及びそれによるエピタキシャル特性の安定した半導体ウェハを提供することにある。

【解決手段】 ラッピング後、エッチングした半導体ウェハを、露出時間が数値表示される顕微鏡写真撮影装置にセットして、当該導体ウェハの裏面についての露出時間を計測し、予め把握されている上記露出時間とエッチング量との相関から、当該半導体ウェハの裏面粗さを評価する。簡便には、目標とする標準の裏面粗さを有する半導体ウェハについてその裏面の標準露出時間を測定しておき、実際に評価をすべき半導体ウェハの裏面についての実際の露出時間を測定し、この実際の露出時間を上記標準露出時間と比較して、当該半導体ウェハの裏面粗さを評価する。

(もっと読む)

1 - 20 / 23

[ Back to top ]