Fターム[5F044AA12]の内容

ボンディング (23,044) | ワイヤによるペレット電極との接続構造 (951) | 他の素子電極との接続 (50)

Fターム[5F044AA12]に分類される特許

41 - 50 / 50

半導体装置

【課題】実装高さ縮小および実装面積縮小及び軽量化を満足する積層型の半導体装置を高性能、かつ既存の製造ラインで低コストに実現する。

【解決手段】絶縁性樹脂からなる封止体4と、半導体チップを支持するタブ1eと、前記封止体の実装面に一面を露出する複数のリード1aと、前記封止体内に位置し、回路形成面である第1主面およびその反対側の第1裏面を有し、前記タブの一面に支持される第1半導体チップ2と、前記第1半導体チップの第1主面に形成された複数の第1電極パッド2aと、前記電極パッドと前記リードとを電気的に接続するワイヤ5、回路形成面である第2主面およびその反対側の第2裏面を有し、前記第1半導体チップの第1主面に積層搭載された第2半導体チップ3と、前記第1半導体チップの複数の第1電極パッドと前記リード、前記第2半導体チップの第2主面に形成された複数の第2電極パッドと前記リードとをそれぞれ電気的に接続するワイヤ5とを含み、前記タブは枠状に形成されている絶縁性樹脂からなる半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】電極パッド上のメッキ膜の厚さのバラツキが増大して、保護膜の表面よりもメッキ膜が突出していると、重なり合う2枚の配線基板において双方の配線基板の保護膜に傷が付き、配線保護に悪影響を及ぼすような傷の場合には配線基板が不良となるため、半田接合部の耐衝撃強度向上を図ること共に、電極パッド上に形成されるメッキ膜のバラツキを低減し、ニッケルメッキ膜が設けられた半導体装置に適用して有効な技術を提供する。

【解決手段】電極パッド7aの表面に電解メッキ法でメッキ膜(例えばNi膜)を形成する工程において、前記電極パッド7aの表面に第1の電流密度で第1の層12aを形成し、その後、前記第1の層の表面に前記第1の電流密度よりも高い第2の電流密度で第2の層12bを形成する。

(もっと読む)

マルチチップ構造を採用した半導体装置

【課題】半導体チップへのダメージを最小限に抑えたマルチチップ構造の半導体装置;製造工程における作業性の高いマルチチップ構造の半導体装置;半導体チップ単位での特性試験を容易に行い得るマルチチップ構造の半導体装置を提供すること。

【解決手段】リードフレームをベースフレームとして用いて製造される半導体装置において、ベースフレーム上に複数の半導体チップを積層してなり、少なくとも一つの面が外部と電気的に接続可能な端子領域を有する第1のマルチチップ構造部と;ベースフレーム上に複数の半導体チップを積層してなり、少なくとも一つの面が外部と電気的に接続可能な端子領域を有する第2のマルチチップ構造部とを備える。そして、ベースフレームのインナーリードが、第1のマルチチップ構造部の端子領域と、第2のマルチチップ構造部の端子領域とにワイヤボンディングによって接続される。

(もっと読む)

バッテリ電力制御用マルチ・チップ・モジュール

バッテリ保護回路に使用するのに適したマルチ・チップ・モジュール。マルチ・チップ・モジュールは、集積回路チップ、第1のパワー・トランジスタ、第2のパワー・トランジスタ、集積回路チップを第1のパワー・トランジスタに電気的に接続する第1の接続構造、集積回路チップを第2のパワー・トランジスタに電気的に接続する第2の接続構造と、第1のリード、第2のリード、第3のリードおよび第4のリードを含むリードフレーム構造とを含み、集積回路チップ、第1のパワー・トランジスタおよび第2のパワー・トランジスタがリードフレーム構造に搭載されている。モールディング材料は、集積回路チップ、第1のパワー・トランジスタ、第2のパワー・トランジスタ、第1の接続構造および第2の接続構造の少なくとも一部分を覆う。  (もっと読む)

(もっと読む)

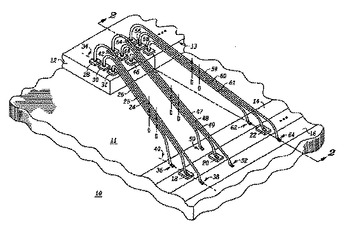

積層化集積回路を備えた集積回路パッケージとそのための方法

集積回路パッケージ内で集積回路ダイを積層化するための改良された技術が開示される。これらの改良された技術によれば、集積回路パッケージ内の集積回路ダイの積層化密度をより大きくすることができる。更に改良した積層化技術によれば、従来の接合技術を用いて種々の集積回路ダイを互いに、又は基板に電気的に接続することができる。これら改良された方法は、同じサイズ(多くの場合同じ機能)の集積回路ダイを集積回路パッケージ内に積層化するのに特に有用である。そのような集積回路パッケージの一例として、積層体内に配置される複数の類似したサイズのメモリ保存集積回路ダイを備えた不揮発性メモリ集積回路パッケージが挙げられる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 高集積化された半導体装置を安定して製造することができる半導体装置の製造方法を得る。

【解決手段】 複数のパッドについてバンプ電極を形成し、そのバンプ電極上にワイヤをステッチボンディングする場合に、まず、第1工程として、複数のパッドの1つにバンプ電極を形成する。次に、第2工程として、第1工程の直後に、バンプ電極上にワイヤをステッチボンディングする。そして、第3工程として、複数のパッドの他の各パッドについて同様に第1工程と第2工程を繰り返し行う。

(もっと読む)

半導体装置

【課題】接続信頼性の高い半導体装置を提供する。

【解決手段】受光素子4に設けられた電極パッド10と、制御素子5に設けられた電極パッド10とを導通接続する2本のワイヤ8であって、第1のワイヤ11は、ファーストボンド11aが受光素子4の電極パッド10に接続され、かつセカンドボンド11bが制御素子5の電極パッド10に接続され、第2のワイヤ12は、第1のワイヤ11のセカンドボンド11bとした位置にセキュリティボンドとしたファーストボンド12aが接続され、かつ第1のワイヤ11のファーストボンド11aが接続された位置とは異なる位置にセカンドボンド12bが接続されている。

(もっと読む)

電力半導体装置

【課題】単位ワイヤ当たりの電流密度を小さくして、主電流ワイヤのボンド部の温度上昇を低減化することにより、スイッチング動作時に於ける熱サイクル疲労に対する寿命の向上化を図る。

【解決手段】主電流ワイヤ用ボンド部22aを有する主電流ワイヤ10のワイヤ群とは別に、電力用トランジスタ1のエミッタ電極13上と電力用ダイオード2のアノード電極14上とに、シングルボンド部21a,21bを有するボンディングワイヤ17aが、形成されている。加えて、電力用ダイオード2のアノード電極14の他端側上(エミッタ電極13とは反対側の端近傍の電極表面上)と第2主端子6の一端側寄り部分上とにシングルボンド部21c,21dを有するボンディングワイヤ17bが、形成されている。

(もっと読む)

半導体装置並びにその製造方法及びそれを用いた電子機器

【課題】 低廉で信頼性の高い半導体装置を提供する。

【解決手段】 パワー素子である第1の半導体チップ1と、前記パワー素子を制御する制御回路が形成される第2の半導体チップ2とを備え、前記パワー素子が有する駆動端子の一つに電気的に接続される電極パッド1Aを第1の半導体チップ1の表面中央部に設けている半導体装置。

(もっと読む)

ワイヤ・ボンドの位置付けを最適化した半導体パッケージ

密接配置したボンディング・ワイヤを種々の異なるパッケージング用途に用いると、電気的性能の向上を図ることができる。一実施形態では、ワイヤ群内にある2本の隣接するボンディング・ワイヤが密接配置されているのは、2本の隣接するワイヤのうちの短い方の長さの少なくとも50パーセントで、これら2本の隣接するワイヤ間において分離距離Dが満たされる場合である。一実施形態では、分離距離Dは、2本の隣接するワイヤのうちの直径が大きい方のワイヤの直径の多くとも2倍である。別の実施形態では、分離距離Dは、2本の隣接するワイヤ間のワイヤ間ピッチの多くとも3倍である。各ワイヤ群は、2本以上の密接配置ワイヤを含むことができる。密接配置ボンディング・ワイヤのワイヤ群を用いると、例えば、電力−信号−接地の三重組、信号−接地対、信号−電力対、あるいは差動信号対または三重組を形成することができる。  (もっと読む)

(もっと読む)

41 - 50 / 50

[ Back to top ]