Fターム[5F044LL02]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | 直接ハンダ付け状態 (1,160) | 基板の貫通孔を介してハンダ付け (18)

Fターム[5F044LL02]に分類される特許

1 - 18 / 18

多層回路基板、その製造方法及び半導体装置

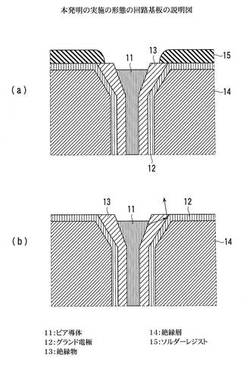

【課題】 多層回路基板、その製造方法及び半導体装置に関し、基板表面に露出した電極端子の近傍におけるインピーダンス整合を実現する。

【解決手段】 複数の絶縁層と複数の導体層とが交互に積層された多層基板と、前記多層基板の一方の主表面側に形成され、前記多層基板の内部から前記主表面に向かうにつれて径が大きくなる円錐台形状のビア導体と、前記円錐台形状のビア導体に対して絶縁層を介して同軸的に形成された縦断面がテーパ状部を有するグランド電極とを設ける。

(もっと読む)

微細孔シート、半導体装置、および半導体装置の製造方法

【課題】電子部品のパッドとプリント配線板のパッド間において、未はんだや、電極間ブリッジを解消できる微細孔シートを提供する。

【解決手段】微細孔シート1は、電子部品のパッドおよびプリント配線板のパッドのうち、小さい方のパッドにつき2個以上の貫通孔2が配置されており、2個以上の貫通孔のうち、少なくとも1個はパッドと対向する位置に、かつ少なくとも1個は隣接するパッドとの間の中間点よりパッド側に配置されている。

(もっと読む)

配線基板およびはんだバンプ付き配線基板ならびに半導体装置

【課題】 絶縁基板に配置された接続パッドに半導体素子の電極がはんだバンプを介して接合される配線基板において、接続パッドのエレクトロマイグレーションによる空隙が抑制された配線基板を提供する。

【解決手段】 上面に半導体素子の搭載部1aを有する絶縁基板1と、搭載部1aに配置された、半導体素子4の主面の電極5がはんだバンプ6を介して接合される接続パッド2と、絶縁基板1の搭載部1aから内部にかけて形成され、端部が接続パッド2に接続された貫通導体3とを備え、接続パッド2の上面に、平面視で貫通導体3の端部が接続された領域の外側に、はんだバンプ6よりも電気抵抗が低い金属材料からなる凸部2aが形成されている配線基板である。貫通導体3からの電流を凸部2aに分散させて接続パッド2における電流密度を低く抑え、エレクトロマイグレーションによる空隙を抑制できる。

(もっと読む)

半導体素子およびフリップチップ相互接続構造を形成する方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】半導体ダイの能動表面上に形成された複数のバンプを有する、半導体ダイを提供するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、前記相互接続部位よりも幅広い、ステップと、前記接続部位から離れた前記基板の領域上にマスキング層を形成するステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップと、を含む、半導体素子を作製する方法。

(もっと読む)

プリント回路板

【課題】プリント配線板に搭載された電子部品の接合部にかかる応力を緩和する。

【解決手段】マトリクス形状に配置された端子を有する電子部品2の角部端子2bは、電気信号を伝えない。プリント配線板1には、電子部品2の残りの端子2aと電気的に接続するためのマトリクス形状のランド3が設けられており、角部端子2bに対向する位置には貫通孔4を設ける。これにより、電子部品2の接合部における応力集中を低減し、破断の危険性を回避する。

(もっと読む)

電子装置、配線基板、電子装置の製造方法

【課題】電子部品が配線基板に表面実装される構成において、電子部品の電極と配線基板のランドとの接続信頼性を向上できる電子装置、配線基板、電子装置の製造方法を提供する。

【解決手段】一面にランドが形成された配線基板と、ランドに対応して、外部接続用の電極が形成された電子部品と、ランドと電極とを接続するはんだ接続部と、を備え、電子部品が配線基板に表面実装されてなる電子装置であって、配線基板は、一端がランドに開口し、他端が一面の裏面に開口するとともに、壁面に壁面導体部が形成された貫通孔を有し、ランドは、貫通孔の一端が開口され、壁面導体部と接続された孔ありランドを含み、孔ありランドと電極とを接続するはんだ接続部は、貫通孔内に配置されて壁面導体部に接続された孔内はんだ接続部と、一体的に形成されている。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、半導体部品と回路基板との位置合わせを容易にすること。

【解決手段】表面に複数の第1の電極22が形成された第1の回路基材20と、第1の回路基材20の上方に設けられ、第1の電極22の各々の上方に第1の貫通孔30aと第2の貫通孔30bとが形成された第2の回路基材30と、第2の回路基材30の上方に設けられた半導体パッケージ50と、第1の貫通孔30aと第2の貫通孔30b内に設けられ、第1の電極22と半導体パッケージ50とを接続する複数の第1のバンプ51とを有する半導体装置による。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法における歩留まり低下を防ぐ。

【解決手段】基材60上に絶縁膜30を積層する第1工程と、絶縁膜30にビアホール31を形成する第2工程と、絶縁膜30上に導体層を形成しパターニングすることで、ビアホール31上に貫通穴41a、42aを有する配線41、42を形成する第3工程と、貫通穴41a、42aの上部に電極12が配置されるように半導体チップ11をフェースダウンボンディングする第4工程と、を含む半導体装置1の製造方法である。

(もっと読む)

電子部品装置及びその製造方法

【課題】電子部品の実装面積を小さくできると共に、電子部品を平行度よく実装できる電子部品装置の製造方法を提供する。

【解決手段】シリコン基板11と、その上面側に設けられた凹部Cと、凹部Cの底面側のシリコン基板11を貫通して形成されたスルーホールTHと、シリコン基板11に形成された絶縁層14と、スルーホールTH内の下部からその高さ方向の途中まで形成された下側金属部22と、スルーホールTH内の下側金属部22の上に形成された接続金属部材26(インジウム層)とにより構成される貫通電極20とを備えた配線基板1と、下面側に端子金属部材42(金バンプ)を備えた電子部品40とを用意する工程と、加熱雰囲気で、配線基板1の接続金属部材26を軟化させ、電子部品40の端子金属部材42を接続金属部材26に突き刺して接続する工程とを含む。

(もっと読む)

半導体部品の実装構造及び実装方法

【課題】半導体部品を回路基板上に容易に実装することができ、且つ回路基板からの半導体部品の取り外しも容易な半導体部品の実装構造及び実装方法を提供する。

【解決手段】BGA型半導体部品1の底面に複数のはんだバンプ12を突設させ、回路基板3に、はんだバンプ12を挿入可能な開口径を有するとともに、はんだバンプ12と同じ間隔で形成され、当該回路基板3の厚さ方向に貫通する複数のスルーホール31を備え、はんだバンプ12をスルーホール31に挿入させ、次いで、回路基板3の底面側から加熱することによりはんだバンプ12を溶解させて、BGA型半導体部品1を回路基板3に溶着する。

(もっと読む)

半導体部品の実装方法

【課題】回路基板上へのBGA型半導体部品の取り付け、取り外しを容易に行うことができるBGA型半導体部品の実装方法を提供する

【解決手段】BGA半導体部品1の底面に複数のはんだバンプ12を格子状に突設させ、回路基板2に、はんだバンプ12を挿入可能な開口径を有するとともに、はんだバンプ12と同じ間隔で形成され、当該回路基板2の厚さ方向に貫通する複数のスルーホール21を設ける。そして、はんだバンプ12の融点よりも高い耐熱温度を有する治具ボード3を、回路基板2の底面側に配置するとともに、BGA型半導体部品1を、はんだバンプ12を回路基板2の上面側からスルーホール21に挿入することにより、回路基板2の上面側に配置し、次いで、はんだバンプ12を加熱してBGA型半導体部品1を回路基板2に溶着させ、その後、治具ボード3を回路基板2から取り外す。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体チップに形成された電極パッド108と製品用基板120との一括した接続が可能な、新規かつ改良された半導体装置および半導体装置の製造方法を提供する。

【解決手段】電極パッド108が形成された半導体チップ104と、半導体チップ104を搭載して封止するためのパッケージ実装用基板102と、半導体チップ104の電極パッド108に電気的に接続するための金属柱114とを備え、半導体チップ104は、電極パッド形成面をパッケージ実装用基板102に対向させ、パッケージ実装用基板102に固着され、パッケージ実装用基板102は、電極パッド108の部位に貫通孔112が形成されており、金属柱114は、パッケージ実装用基板102の貫通孔112に挿入されて半導体チップ104の電極パッド108に接続し、さらにパッケージ実装用基板102から突出して封止により固定されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】工程の大幅な簡素化が図れかつ薄型化が可能であり、ICチップにダメージを与えるおそれのない半導体装置および半導体装置の製造方法を提供する。

【解決手段】ICチップ1の電極パッド2形成面に電気絶縁基材3を取り付け、電気絶縁基材3のICチップ被着面と反対側の面に、導体パターンを有する金属箔層5を貼り付ける。電気絶縁基材に設けた貫通孔3cに、ICチップの電極パッド2と金属箔層5の導体パターンとを接続する貫通電極4をメッキにて形成する。

(もっと読む)

半導体フリップチップパッケージ用の基板およびプロセス

フリップチップパッケージ用の半導体パッケージ構造は、基板(830)およびチップ(820)を備えている。基板(830)は、パターンされた回路層(860)および絶縁層(832)を少なくとも備えている。パターン化された回路層は、複数のバンプパッド(840)を備え、絶縁層は、複数のエッチング孔(834)を備えている。バンプ(810)が、チップの活性面に配置されている。これらのバンプは、スタッドバンピングによって、得られる。エッチング孔は、ソルダペースト(870)によって充填され、チップのバンプが、ソルダ充填エッチング孔に入り込むようになっている。 (もっと読む)

電子部品の位置決め方法、ならびに、電子部品およびその製造方法

【課題】電子部品を搭載する基板の特定箇所に、電子部品の特定部位を正確かつ高速で位置決めする方法を提供する。

【解決手段】電子部品の特定部位に他の部位よりも強い磁性を付与し、この電子部品に所定方向から磁場を印加することにより、特定部位を所定方位に配列させる工程を有する位置決め方法。この方法において、基板の特定箇所もしくはその近傍に仮配置した電子部品に所定方向から磁場を印加する方法、および仮配置用部材の所定箇所に配置した電子部品に所定方向から磁場を印加した後、その配列状態を維持したまま電子部品を基板に移転させる方法が好ましい。

(もっと読む)

配線基板、半導体装置、及び半導体装置の製造方法

【課題】

半導体装置の組立工程の時間の増加を抑制し、パッケージ信頼性を維持しながら、反りを大幅に低減する半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、(a)一方の面から他方の面へ貫通する複数の孔(14)を含みアンダーフィル樹脂31を含浸させることが可能な絶縁層2と絶縁層2内に設けられた回路配線11とを備える配線基板1の両側から、それぞれ第1半導体チップ21及び第2半導体チップ21を回路配線11に接続する工程と、(b)配線基板1の一方の側からアンダーフィル樹脂31を含浸する工程と、(c)第1及び第2半導体チップ21と配線基板1とが一体化するようにアンダーフィル樹脂31を硬化する工程とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】小型で高密度、高機能な半導体システムを実現するため、複数の異なる半導体チップ間を貫通電極を用いて最短の配線長で三次元的に接続し、低ノイズな高速動作を可能とする方法について、公知例に対比して非常に低コスト、短TAT、かつ常温での接合が可能で接続信頼性に優れた三次元の接続方法を提供する。

【解決手段】例えば、異なる上下の半導体チップの中間に上下チップ間を接続するためのインターポーザ基板を配した三次元のチップ積層構造において、半導体チップ及びインターポーザ基板裏面側に表層電極に達するまでの貫通孔を形成し、孔の側壁及び裏面側周囲に金属製のメッキ膜を施し、前記金属製のメッキ膜が施された貫通孔内部に、上段側に積層される半導体チップの金属製バンプを圧接によって変形注入させ、半導体チップ及びインターポーザ基板内に形成された貫通孔内部に前記金属製バンプを幾何学的にかしめて電気的に接続させる。

(もっと読む)

半導体装置

【課題】 はんだ接合部の応力集中を緩和しディバイスに発生する内部熱を効率的に放熱して信頼性の向上を図る。

【解決手段】 実装面2aに接続電極6と周辺補強用ダミー電極7と中央補強用ダミー電極8が形成されたディバイス2と、接続ランド10と周辺補強ランド11と中央補強ランド12とが形成されディバイス2をディバイス実装面3a上に実装する実装基板3とを備える。実装基板3には、中央補強ランド12に接続される放熱ビア14と、裏面3bに放熱パターン15が形成され、中央補強ランド12がディバイス2からの発生部を兼用して裏面3bからの放熱を行う。

(もっと読む)

1 - 18 / 18

[ Back to top ]