Fターム[5F045BB12]の内容

気相成長(金属層を除く) (114,827) | 目的 (9,309) | 歪・反り防止 (1,345) | 結晶性・格子整合性の向上・結晶欠陥の防止 (911)

Fターム[5F045BB12]に分類される特許

141 - 160 / 911

ホモエピタキシャルIII−V族窒化物品、デバイス、およびIII−V族窒化物ホモエピタキシャル層を形成する方法

【課題】LEDや高電子移動度トランジスタなどのデバイス用として有用なIII−V族窒化物品の提供。

【解決手段】自立III−V族窒化物基板上に堆積したIII−V族窒化物ホモエピタキシャル層を含むホモエピタキシャルIII−V族窒化物品であって、前記III−V族窒化物ホモエピタキシャル層が1E6/cm2未満の転位密度を有しており、(i)前記III−V族窒化物ホモエピタキシャル層と前記自立III−V族窒化物基板の間に酸化物を有するか、(ii)前記III−V族窒化物ホモエピタキシャル層と前記自立III−V族窒化物基板の間にエピ中間層を有するか、

(iii)前記自立III−V族窒化物基板がオフカットされており、前記III−V族窒化物ホモエピタキシャル層が非(0001)ホモエピタキシャルステップフロー成長結晶を含むことを特徴とする。

(もっと読む)

半導体発光素子と、その製造方法およびランプ、電子機器、機械装置

【課題】発光層の結晶性に起因する不良が生じにくく、かつ、高い出力の得られる半導体発光素子および半導体発光素子の製造方法を提供する。

【解決手段】第一有機金属化学気相成長装置において、基板上に第一n型半導体層を積層する第一工程と、第二有機金属化学気相成長装置において前記第一n型半導体層上に、第二n型半導体層と、障壁層およびGa1−yInyN(0.07<y<0.30)なる組成の井戸層からなる発光層と、p型半導体層と、を順次積層する第二工程とを具備し、前記第二工程において、前記障壁層を第一の成長温度T1で成長させた後に、前記第一の成長温度T1よりも高温の第二の成長温度T2に昇温して前記障壁層を成長させ、さらに、前記第二の成長温度T2よりも低温の前記第三の成長温度T3に降温して前記障壁層の成長を続けることを特徴とする半導体発光素子の製造方法を採用する。

(もっと読む)

III族窒化物半導体の種結晶の製造方法、III族窒化物半導体単結晶の製造方法、基板の製造方法、種結晶

【課題】拡大成長させた場合に、結晶性の良好なIII族窒化物半導体単結晶を得ることができるIII族窒化物半導体の種結晶の製造方法、およびIII族窒化物半導体単結晶の製造方法を提供すること。

【解決手段】III族窒化物半導体の種結晶の製造方法は、気相成長法により、種結晶形成用部材1上に複数のIII族窒化物半導体の核を離間させて形成し、前記複数の核を成長させて、前記複数の核から複数の種結晶2を得る。

(もっと読む)

半導体素子およびその製造方法

【課題】バッファで改善された結晶性および平坦性を有効に機能積層体に引き継がせることにより、機能積層体の平坦性および結晶性を向上させた半導体素子をその製造方法とともに提供する。

【解決手段】基板1上に、バッファ2と、複数の窒化物半導体層を含む機能積層体3とを具える半導体素子100であって、機能積層体3は、バッファ2側にn型またはi型である第1のAlxGa1−xN層4(0≦x<1)を有し、バッファ2と機能積層体3との間に、第1のAlxGa1−xN層4とAl組成が略等しいp型不純物を含むAlzGa1−zN調整層5(x−0.05≦z≦x+0.05、0≦z<1)を具え、バッファ2は、少なくとも機能積層体3側にAlαGa1−αN層(0≦α≦1)を含み、該AlαGa1−αN層のAl組成αと、第1のAlxGa1−xN層4のAl組成xとの差が、0.1以上であることを特徴とする。

(もっと読む)

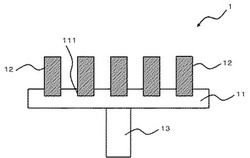

成膜装置

【課題】 ホモエピタキシャル成長による成膜中における薄膜上への副生成物の落下量が減少して半導体ウエハの品質が向上する成膜装置を提供する。

【解決手段】 本発明に係る成膜装置1は、上面に炭化ケイ素基板2が載置されるサセプタ3と、これらの炭化ケイ素基板2およびサセプタ3を収容する反応容器4と、を備え、前記炭化ケイ素基板2上に薄膜をホモエピタキシャル成長させる成膜装置1である。サセプタ3の上面および反応容器4の内面の少なくともいずれかに、単結晶または多結晶の3C−SiCからなる第1のライナー7と第2のライナー8を設けている。

(もっと読む)

窒化物半導体素子

【課題】 リーク電流の増加を抑制しつつ、基板上のIII族窒化物半導体の超格子構造の周期数を増やした場合でもクラックの発生を抑制できる窒化物半導体素子を提供する。

【解決手段】 基板2上に、GaN層10およびAlN層11が複数対交互に積層された第1GaN/AlN超格子層8を形成し、この第1GaN/AlN超格子層8に接するように、GaN層12およびAlN層13が複数対交互に積層された第2GaN/AlN超格子層9を形成する。第2GaN/AlN超格子層9上には、GaN電子走行層6およびAlGaN電子供給層7からなる素子動作層を形成する。これにより、HEMT1を構成する。このHEMT1において、第1GaN/AlN超格子層8のc軸平均格子定数LC1と、第2GaN/AlN超格子層9のc軸平均格子定数LC2と、GaN電子走行層6のc軸平均格子定数LC3とが、式(1)LC1<LC2<LC3を満たすようにする。

(もっと読む)

エピタキシャル炭化珪素単結晶基板及びその製造方法

【課題】オフ角度の小さな炭化珪素単結晶基板上に、高品質でドーピング密度の面内均一性に優れた炭化珪素エピタキシャル膜を有するエピタキシャル炭化珪素単結晶基板、及びその製造方法を提供する。

【解決手段】オフ角度が1°以上6°以下の炭化珪素単結晶基板上に、ドーピング密度の面内均一性に優れた炭化珪素エピタキシャル膜を有するエピタキシャル炭化珪素単結晶基板、及び、その製造方法であり、上記エピタキシャル膜が、0.5μm以下のドープ層と0.1μm以下のノンドープ層とを繰り返し成長させており、そのエピタキシャル成長において、ドープ層を形成する場合には材料ガス中の珪素原子数に対する炭素原子数の比(C/Si比)を1.5以上2.0以下とし、その時にドーピングガスである窒素を導入してドープ層とする。ノンドープ層を形成する場合にはC/Si比を0.5以上1.5未満とする。

(もっと読む)

プラズマCVD成膜装置および高周波電圧の印加方法

【課題】プラズマCVD成膜装置において、膜の膜特性や成膜速度の向上と、クリーニングによる損傷の低減との両有用性を選択自在に取得する。

【解決手段】真空チャンバ10を有するプラズマCVD成膜装置1において、真空チャンバ10内において平行して対向配置される高周波電極5および対向電極6を有する平行平板電極と、高周波電極5に高周波電圧を印加する高周波電源2と、高周波電源2と高周波電極5との間に直列接続されるブロッキングコンデンサC2を含むマッチングボックス3と、マッチングボックス3と高周波電極5との間に、平行平板電極に並列接続する低周波フィルタ回路7を備える。低周波フィルタ回路7は、高周波電源側からマッチングボックスを介して高周波電極に印加される高周波電力について、高周波電極と接地点との直流的な接続関係を可変として、高周波電極の直流電圧を調整する。

(もっと読む)

炭化珪素単結晶基板および炭化珪素単結晶エピタキシャルウェハ

【課題】デバイス特性の劣化や、歩留まりの低下を抑制するため、貫通転位の転位線の方向を規定する。

【解決手段】貫通転位3の転位線の方向が揃えられ、貫通転位3の転位線の方向と[0001]c軸とが平行となるようにする。[0001]c軸方向に転位線を持つ貫通転位3は、基底面転位の転位線の方向と垂直であるため、C面内の拡張転位とはならず、積層欠陥を発生させることがない。このため、貫通転位3の転位線の方向が[0001]c軸であるSiC単結晶基板に対して電子デバイスを形成すれば、デバイス特性は良好となり、劣化が無く、歩留まりも向上したSiC半導体装置とすることができる。

(もっと読む)

AlGaInP系半導体発光素子用エピタキシャルウェハ及びその製造方法

【課題】AlGaInP系半導体発光素子用エピタキシャルウェハ表面平坦度およびダイオードチップを製造する際の発光強度の歩留まりを向上できるAlGaInP系半導体発光素子用エピタキシャルウェハを提供する。

【解決手段】N型GaAs基板2上に、N型AlGaInP系クラッド層4、AlGaInP系活性層5、P型AlGaInP系クラッド層6、及びGaPからなる電流拡散層7を有するAlGaInP系半導体発光素子用エピタキシャルウェハ1において、電流拡散層7が、P型AlGaInP系クラッド層6上に形成されたV/III比が1以上100以下の低V/III比部分8と、低V/III比部分上に形成されたV/III比が100以上500以下の高V/III比部分9とからなるものである。

(もっと読む)

プラズマ処理装置およびプラズマ処理方法

【課題】珪素粒子の欠陥密度を可及的に低減すること。

【解決手段】珪素粒子1を積載する第一の電極2と、水素プラズマの発生領域を挟んで第一の電極2に対向して配設されている第二の電極4と、第一の電極2の温度が第二の電極4の温度よりも高くなるように温度制御して第一の電極2と第二の電極4との間に原料ガスの対流を起こす温度制御手段(ヒーター3、冷却管6)と、を備え、原料ガスの対流によって第一の電極2に積載されている珪素粒子1を水素プラズマ中に浮遊させて水素プラズマに曝露する。

(もっと読む)

炭化珪素半導体エピタキシャル基板の製造方法

【課題】点欠陥の少ない炭化珪素半導体エピタキシャル基板を製造する方法を提供する。

【解決手段】本発明の炭化珪素半導体エピタキシャル基板の製造方法は、オフセット角が2°以上10°以下である炭化珪素単結晶基板10を用意する工程と、化学気相堆積法により、1400℃以上1650℃以下の温度で、炭化珪素からなるエピタキシャル層11を前記炭化珪素単結晶基板上に成長させる工程と、前記エピタキシャル層を1300℃以上1800℃以下の温度で熱処理する工程とを包含する。

(もっと読む)

化合物半導体基板の製造方法

【課題】結晶欠陥の少ない化合物半導体層を種基板上にエピタキシャル成長できる化合物半導体基板の製造方法を提供する。

【解決手段】電解めっきにおいて種基板10を膜厚方向に貫通する貫通転位101〜105をそれぞれ通して種基板10の厚さ方向に電流を流すことにより、種基板10の第1の主面11上の貫通転位101〜105が存在する位置に金属膜201〜205を選択的に形成するステップと、金属膜201〜205の融点より低いエピタキシャル成長温度で、金属膜201〜205を覆うように種基板10の第1の主面11上に化合物半導体層30をエピタキシャル成長させるステップとを含む。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】室温(300K)以上において正孔濃度が1.0×1015cm‐3以上で、かつ、ドーパント原子濃度が1.0×1021cm‐3以下である実用的なp型ダイヤモンド半導体デバイスとその製造方法を提供すること。

【解決手段】単結晶ダイヤモンド基板1−1の上に形成された単結晶ダイヤモンド薄膜1−2の中には、二次元の正孔または電子チャンネル1−3が形成される。基板1−1の面方位と基板1−1の結晶軸「001」方向との成す角度をαs、ダイヤモンド薄膜1−2の面方位と単結晶ダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαd、チャンネル1−3の面方位とダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαcとする。単結晶ダイヤモンド薄膜1−2の表面上には、ソース電極1−4、ゲート電極1−5、ドレイン電極1−6が形成される。

(もっと読む)

単結晶3C−SiC基板の製造方法およびそれによって得られた単結晶3C−SiC基板

【課題】エピタキシャル成長過程において発生する表面欠陥を大幅に減少させることができ、後工程を簡略化しながら半導体デバイスとしての品質を確保できる単結晶3C−SiC基板の製造方法を提供する。

【解決手段】ベース基板上にエピタキシャル成長によって単結晶3C−SiC層を形成させる単結晶3C−SiC基板の製造方法であって、

上記単結晶3C−SiC層を、平坦性の高い表面とその中に点在する表面ピットからなる表面状態となるよう形成する第1の成長段階と、

上記第1の成長段階で得られた単結晶3C−SiC層を、脱離律速の領域において表面の上記表面ピットを埋めるようさらにエピタキシャル成長させる第2の成長段階とを行う。

(もっと読む)

炭化珪素エピタキシャル膜の製造方法

【課題】高品質のエピタキシャル膜を製造することができる、新たな炭化珪素エピタキシャル膜の製造方法を提供する。

【解決手段】化学気相堆積法によって、炭化珪素単結晶基板上に炭化珪素エピタキシャル膜を成膜する炭化珪素エピタキシャル膜の製造方法であって、圧力条件又は基板温度条件のうち、いずれか一方の条件を固定したまま、成膜途中で、他方の条件を、高い設定条件と低い設定条件との間で切り替えることを特徴とする炭化珪素エピタキシャル膜の製造方法である。

(もっと読む)

窒化物半導体素子

【課題】Si基板の上に形成した窒化物半導体素子の生産性及び動作特性を向上させる。

【解決手段】窒化物半導体素子は、シリコン基板101の上に初期層102を介して形成された歪み抑制層110と、歪み抑制層の上に形成された動作層120とを備えている。歪み抑制層110は、第1のスペーサ層111と、第1のスペーサ層の上に接して形成された第2のスペーサ層112と、第2のスペーサ層の上に接して形成された超格子層113とを有している。第1のスペーサ層は、格子定数が第2のスペーサ層よりも大きい。超格子層は、第1の層113A及び第1の層よりも格子定数が小さい第2の層113Bが交互に積層されている。超格子層の平均の格子定数は、第1のスペーサ層の格子定数よりも小さく且つ第2のスペーサ層の格子定数よりも大きい。

(もっと読む)

エピタキシャル炭化珪素単結晶基板の製造方法

【課題】炭化珪素単結晶基板に含まれる基底面転位がエピタキシャル膜に引き継がれるのを抑制して、高品質のエピタキシャル膜を成膜することができるエピタキシャル炭化珪素単結晶基板の製造方法を提供し、また、これにより得られたエピタキシャル炭化珪素単結晶基板を提供する。

【解決手段】化学気相堆積法によって、炭化珪素単結晶基板上に炭化珪素膜をエピタキシャル成長させる結晶成長工程において、エピタキシャル成長の主たる時間を占める結晶成長主工程での成長温度T1に対し、低い設定温度T0と高い設定温度T2との間で、成長温度を上下に変化させる温度切り替え操作を伴う結晶成長副工程を含むエピタキシャル炭化珪素単結晶基板の製造方法であり、また、この方法を用いて得られたエピタキシャル炭化珪素単結晶基板である。

(もっと読む)

炭化珪素単結晶基板、炭化珪素エピタキシャルウェハ、及び薄膜エピタキシャルウェハ

【課題】体積抵抗率が低く、しかも、エピタキシャル成長工程等のウエハプロセスにおいて炭化珪素単結晶基板が1000℃以上に晒されても、積層欠陥が殆ど発生することがない炭化珪素単結晶基板、および、この基板を用いて得た炭化珪素エピタキシャルウェハ、及び薄膜エピタキシャルウェハを提供する。

【解決手段】体積抵抗率が0.001Ωcm以上0.012Ωcm以下の炭化珪素単結晶基板であり、表裏面のうち少なくとも片面の表面粗さRaが1.0nm以下であると共に、外周側面の表面粗さRaが1.0nm以下である炭化珪素単結晶基板、および、前記炭化珪素単結晶基板上に炭化珪素薄膜をエピタキシャル成長してなる炭化珪素エピタキシャルウェハ、あるいは、窒化ガリウム、窒化アルミニウム、窒化インジウム又はこれらの混晶をエピタキシャル成長してなる薄膜エピタキシャルウェハ。

(もっと読む)

エピタキシャルウェーハの製造方法、エピタキシャルウェーハ及び撮像用デバイスの製造方法

【課題】欠陥のほとんどないシリコンエピタキシャル層を形成できるエピタキシャルウェーハの製造方法、当該方法により製造されたエピタキシャルウェーハ及び撮像用デバイスの製造方法を提供することを目的とする

【解決手段】前記シリコン基板に急速熱処理を施すことによって、少なくとも前記シリコン基板の表面から0.5μmの深さまでの領域に存在するRIE法により検出される欠陥を消滅させるRIE欠陥消滅工程と、前記RIE法により検出される欠陥を消滅させたシリコン基板の表面上に前記シリコンエピタキシャル層を形成する工程とを具備するエピタキシャルウェーハの製造方法。

(もっと読む)

141 - 160 / 911

[ Back to top ]