Fターム[5F046DA29]の内容

半導体の露光(電子、イオン線露光を除く) (57,085) | 露光の制御、調整の対象、内容 (6,447) | 露光前後のプロセス (119)

Fターム[5F046DA29]に分類される特許

1 - 20 / 119

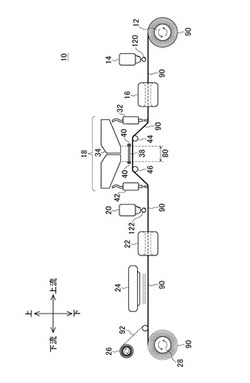

フィルム状製品の製造方法、フィルム状製品の製造装置、及び、マスク

【課題】最終的に希望する1パターン以上の露光面積分のマスクと、光源と、場所が必要になり、フィルム状製品の製造装置が大きくなる。

【解決手段】フィルム状製品の製造方法は、長尺状のフィルム90を長手方向に搬送する搬送ステップと、予め定められた露光領域80を露光する露光装置を用いて、前記フィルム90を露光する露光ステップとを備え、前記搬送ステップおよび前記露光ステップにおいて、前記露光装置の前記露光領域における前記長手方向の長さよりも長く、切れ目なく前記フィルム90を露光する。

(もっと読む)

基板テーブル、リソグラフィ装置、及びリソグラフィ装置を使用してデバイスを製造するための方法

【課題】センサの読み取りにおける誤差の可能性を少なくとも低減する装置を提供する。

【解決手段】リソグラフィ装置のための基板テーブルであって、該基板テーブルは、前記基板テーブル上に配置されているエンコーダプレートと、前記エンコーダプレートと前記基板テーブルの上表面との間の隙間であって、前記基板テーブルの外周に対し放射方向に前記エンコーダプレートの内側に位置する隙間と、前記隙間から液体を抽出するために前記隙間の表面にある1つまたは複数の開口をもつ流体抽出システムと、を備える。

(もっと読む)

半導体装置の製造方法及びフォトマスク

【課題】半導体記憶装置の製造において、パターン間隔を縮小し、レジスト膜厚、エッチング量等のバラツキに対応する。

【解決手段】半導体装置の製造方法は、基板上に被加工膜を形成する工程(a)、被加工膜上にレジスト膜を形成する工程(b)、フォトマスクのマスクパターン200bをレジスト膜に転写パターン200cとして転写する工程(c)、転写パターン200cを加工する工程(d)を含む。転写パターン200cは、所定間隔を開けて端部同士が対向して直列に並ぶ第1及び第2の転写ラインパターン201c及び202cと、これらに各々並列する第3及び第4の転写ラインパターン203c及び204cと、第2及び第3の転写ラインパターン202c及び203cの端部同士を接続する接続部212とを含む。工程(d)にて、接続部212の少なくとも一部を除去し、第2及び第3の転写ラインパターン202c及び203cを分離する。

(もっと読む)

基板裏面平坦化方法

【課題】基板の裏面を荒らすことなく微小な傷を除去することができる基板裏面平坦化方法を提供する。

【解決手段】ウエハWの裏面における傷Sの位置や大きさが検出され、位置や大きさが検出された傷Sへ選択的に多数のガス分子28が集合して形成されたガス分子28のクラスター29が吹き付けられ、ウエハWの表面に塗布されたフォトレジスト30が露光される。

(もっと読む)

半導体装置の製造方法

【課題】フォトレジスト上において現像液の液引きの生じない半導体装置の製造方法を提供する。

【解決手段】基板上にフォトレジストを塗布するフォトレジスト塗布工程と、塗布された前記フォトレジストに対して所定のパターンを露光する露光工程と、前記露光工程の後、前記基板を回転させることなく、前記基板上において現像液を供給するノズルを移動させながら、前記基板上の前記フォトレジストに現像液を供給し、前記フォトレジストの現像を行う現像工程と、を有し、前記露光工程における露光は、前記所定のパターンと、前記所定のパターンの他に前記所定のパターンの以外の領域に設けられたダミーパターンに対して行われることを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

マスクパターンの生成方法、マスクパターン生成プログラム及び半導体装置の製造方法

【課題】フォトリソグラフィ法による閉ループを切断する工程を不要とするマスクパターンの生成方法、マスクパターン生成プログラム及び半導体装置の製造方法を提供する。

【解決手段】マスクパターンの生成方法は、回路パターンのレイアウトデータから芯材パターンを取得し、芯材パターンを形成するためのマスクパターンを用いて、芯材パターン、芯材パターンを転写した転写パターン及び芯材パターンまたは転写パターンの側壁に形成する側壁パターンのいずれかを求めるプロセスシミュレーションを行い、芯材パターンまたは転写パターンの側壁に形成される側壁パターンが閉ループを構成するか否かを検証し、検証の結果、側壁パターンが閉ループを構成すると判断する場合は、マスクパターンを変更し、側壁パターンが閉ループを構成しないと判断する場合は、マスクパターンを採用する、ことを含む。

(もっと読む)

パターン形成方法

【課題】マルチパターニングを用いたパターン形成において、高精度のパターンを形成する。

【解決手段】第1のマスクパターンが形成されたマスクを用いて、基板上のレジストを露光し、前記露光後のレジストを現像することにより、前記レジストに第1のサブパターンを形成し、形成された第1のサブパターンの開口底部に接触させずに前記レジストの表面を覆うように酸性膜または酸を発生させる膜を形成する成膜し、該成膜工程後、第2のマスクパターンが形成されたマスクを用いて、前記レジストを露光し、前記露光後のレジストを現像することにより、前記レジストに第2のサブパターンを形成するパターン形成方法であり、前記第2のサブパターンを形成する際の現像処理を終えるまでに、前記酸性膜または酸を発生させる膜を除去することを特徴とするパターン形成方法。

(もっと読む)

半導体装置の製造方法及び製造システム

【課題】レジストパターンの寸法の変動を抑えた半導体装置の製造方法及び製造システムを提供する。

【解決手段】塗布現像装置11において、ウェーハ上にレジスト膜を成膜し(ステップS1)、ウェーハをデバイス領域用の露光装置12に搬送し(ステップS2)、露光装置12において、レジスト膜のうちデバイス領域に形成された部分を露光し(ステップS3)、レジスト膜を加熱して未反応の酸を拡散長を制御しつつ反応させ(ステップS4)、ウェーハを塗布現像装置11に戻し(ステップS5)、塗布現像装置11において、レジスト膜のうち周縁領域に形成された部分を露光し(ステップS6)、レジスト膜を加熱し(ステップS7)、レジスト膜を現像する(ステップS8)。これにより、レジストパターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】ロジック回路とメモリ回路を混載した半導体装置において、ロジック回路部に形成されるレジストパターン形状の精度低下抑制に寄与する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、ロジックトランジスタ、不揮発性メモリをそれぞれ形成する第1及び第2の活性領域を画定する素子分離絶縁膜を、STIで形成する工程と、第2の活性領域上方に、フローティングゲートとなる導電層を形成する工程と、導電層上及びその外側の領域を覆って、窒化シリコンを含む絶縁膜を形成する工程と、第1の活性領域の隣接部分の素子分離絶縁膜上の窒化シリコンを含む絶縁膜を覆い、第1の活性領域を露出するマスクを用いてエッチングする工程と、第1の活性領域の隣接部分の素子分離絶縁膜上の窒化シリコンを含む絶縁膜上に端部の配置されたフォトレジストパターンを形成する工程とを有する。

(もっと読む)

半導体ウェハ端面の処理方法および半導体装置の製造方法

【課題】 ウェハ端面での反射防止膜のリンス処理により形成されたハンプ、又は該ハンプに起因するエッチング段差や膜残渣を除去し、ウェハ端面からの微小異物の飛散を防止する。

【解決手段】 半導体ウェハ111の端面において、半導体ウェハ111上に成膜された反射防止膜121、141の外周部をリンス処理により除去した後、反射防止膜121、141上に設けられたレジストパターン123、143を用いて、反射防止膜121、141及びその下地構造をエッチングする。リンス処理は、反射防止膜121、141の最外周部にハンプ122、142を生じさせ得る。上記エッチングの前又は後に、ウェハ端面において、ウェハ端面以外の領域にマスクを設けることなく、ハンプ122、142が形成された位置をエッチングする。

(もっと読む)

基板検査方法および基板検査装置

【課題】高スループッドで高精度の検査を行う。

【解決手段】表面にレジスト膜が形成されたウェハのエッジ周辺に照明光を照射してその反射光を撮影し、エッジ周辺の明視野画像を取得する明視野画像取得工程S1と、ウェハのエッジ周辺に照明光を2つの光路に分けて照射してウェハ表面からの反射光とレジスト膜からの反射光とが合成された干渉光を撮影し、エッジ周辺の微分干渉画像を取得する微分干渉画像取得工程S2と、明視野画像に基づいてウェハ境界位置を検出するエッジ位置検出工程S11と、微分干渉画像に基づいてEBR境界位置Eを検出する境界位置検出工程S12と、ウェハ境界位置からEBR境界位置までの距離を判定する判定工程S13とを備える基板検査方法を提供する。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】微細なパターンを高精度で形成することのできる半導体装置の製造方法及び半導体装置の製造装置を提供する。

【解決手段】基板に第1パターンを形成する工程と、第1パターンの状態を計測する計測工程と、第1パターンを化学的に処理してリソグラフィーに対する耐性を付与するフリージング工程であって、計測工程の計測結果に基づいて処理条件を変更するフリージング工程と、基板に第2パターンを形成する工程とを具備し、フリージング工程は、処理液を塗布する工程と、第1加熱工程と、不要な処理液を除去するストリッピング工程と、第2加熱工程と、を具備し、変更する処理条件は、第1加熱工程の加熱温度、ストリッピング工程の処理時間、第2加熱工程の加熱温度のうちの少なくともいずれか1つである。

(もっと読む)

薄膜のパターニング方法、デバイス及びその製造方法

【課題】本発明は、表面エネルギーの低い薄膜に、ダメージなくパターニングを行う薄膜のパターニング方法、デバイス及びその製造方法を提供することを目的とする。

【解決手段】薄膜20上に、蒸着膜30を積層する工程と、

前記蒸着膜上に、フォトレジスト層40を積層する工程と、

フォトリソグラフィにより、前記フォトレジスト層をパターニングし、パターニングされた前記フォトレジスト層を用いて前記蒸着膜をエッチングしてパターニングする工程と、

パターニングされた前記蒸着膜をパターンマスクとして、前記薄膜をエッチングしてパターニングを行う工程と、を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】複数の同種の製造装置を用いて半導体装置を製造する場合に、製品間での寸法のばらつきの発生を抑制できる技術を提供する。

【解決手段】制御機器CDをそれぞれの露光機に対して個別に配置する。露光処理が完了した各ロットは、どの露光機で露光処理がなされたかによって分類され、露光機毎に、露光機を調整するためのパラメータが製品情報収集部CD1に収集され、最適製造条件計算部CD2にて処理条件が計算され、計算された処理条件が設定される。すべてのロットは、露光処理を行う露光機が予め割り当てられ、露光処理が済んでいないロットは、分類機CMによって割り当てられた露光機へ振り分けられ、制御機器CDによって求められた処理条件で露光処理が行われる。

(もっと読む)

生産管理装置

【課題】生産ライン1内の複数の露光装置で使用される複数のレチクルの検査を効率よく実行させることが可能な生産管理装置を提供する。

【解決手段】複数のロットが進行する生産ラインに属する露光装置で露光処理に使用される複数のレチクルに対して検査を管理する生産管理装置1であって、露光処理でレチクルに照射された露光量の積算値を取得するレチクル情報収集部6と、取得されたレチクルの積算露光量と、レチクルの継続使用上限露光量未満に設定された基準値とを比較することにより、検査候補となるレチクルを抽出する検査候補レチクル抽出部7と、抽出された検査候補レチクルが仕掛りロットの露光処理に使用される使用予定期間以外の期間を不使用予定期間として算出する不使用予定期間算出部9と、算出された不使用予定期間内に、抽出された検査候補レチクルの検査を検査装置に実行させるレチクル検査計画実行部10とを備える。

(もっと読む)

レジストパターン形成方法および基板処理装置

【課題】ダブルパターンニングにおいて、処理工程を煩雑化させることなく、先に形成されたレジストパターンがその上に塗布されたレジスト材料の溶剤に溶けることを防止する。

【解決手段】基板に第1レジスト材料を用いて第1レジスト膜を形成し、第1レジスト膜に対して露光および現像処理を行って、第1レジストパターンを形成する。ただし、第1レジスト膜形成処理後に行われる塗布後加熱処理、もしくは、第1レジスト膜に対する露光処理後に行われる露光後熱処理において、第1レジスト膜が形成された基板を第1レジスト材料に含まれる樹脂のガラス転移点以上の温度で加熱する。そして、第1レジストパターンが形成された基板に第2レジスト材料を用いて第2レジスト膜を形成し、第2レジスト膜に対して露光および現像処理を行って、第2レジストパターンを形成する。

(もっと読む)

塗布、現像装置、塗布、現像方法及び記憶媒体

【課題】先発ロットの基板に対して処理を終えた後に、後発ロットの基板が加熱モジュールに搬送される前に当該加熱モジュールにおいて整定処理が行われる塗布、現像装置において、その整定によりその加熱モジュールの後段のモジュールへの基板の搬入間隔が広がることを防ぐこと。

【解決手段】塗布ブロック及び現像ブロックの各々について、そのモジュールにて行われる処理に必要なプロセス時間を当該モジュールが用意されている台数で除した値と、塗布ブロック及び現像ブロックの夫々の基板搬送手段が搬送スケジュールにて設定されたモジュール群に対して順次上流側から下流側に基板を受け渡すことにより1周するときの最短時間と、から各加熱モジュールの滞在サイクル数あるいはその滞在サイクル数及び使用する加熱モジュールの数を決定する。

(もっと読む)

基板の処理方法、プログラム、コンピュータ記憶媒体及び基板処理システム

【課題】基板上のレジスト膜の有効面積を向上させつつ、露光処理後に基板の周縁部上のレジスト膜を完全に除去する。

【解決手段】ウェハ上にレジスト液を塗布し、ウェハの全面にレジスト膜を形成する(工程S1)。その後、プリベーク処理を行った後(工程S2)、ウェハ上のレジスト膜を露光処理する(工程S3)。その後、ウェハの周縁部上のレジスト膜に溶剤を供給し、この周縁部上のレジスト膜を除去する(工程S4)。その後、露光後ベーク処理を行った後(工程S5)、ウェハ上のレジスト膜を現像する(工程S6)。

(もっと読む)

半導体基板の露光方法及び半導体装置製造システム

【課題】TATが長くならずに、露光時のフォーカスのばらつきを制御して所望のレジスト寸法を実現することができる半導体基板の露光装置を提供する。

【解決手段】半導体基板の露光方法は、(a)半導体基板に所望のレジストパターンを露光・現像する方法であって、(b)レジスト塗布処理とプレ・ベーク処理とにおける各設備パラメータから、半導体基板に塗布されたレジスト膜厚を半導体基板毎に算出する第1の工程(S101)と、(c)レジスト膜厚と、露光処理における各露光パラメータとから、露光・現像後のレジストパターンのレジスト寸法を半導体基板毎に予測する第2の工程(S102)と、(d)露光前の半導体基板に対して、レジスト寸法に応じて、露光処理における各露光パラメータを補正する第3の工程(S103,S105)とを含む。

(もっと読む)

二重層マスク、三重層マスクのCD制御

【課題】パターンつきフォトレジストマスクと、その下に配された中間マスク層と、その下に配された機能性有機質マスク層と、その下に配されたエッチング層とによって形成されるスタックにおいてエッチング層内のエッチング構成の限界寸法を制御するための方法を提供する。

【解決手段】中間マスク層416は、パターンつきフォトレジストマスク420に対して選択的にエッチングすることによって開口される。機能性有機質マスク層412の開口は、COSを含む開口ガスを流すこと、プラズマを発生させること、および開口ガスを流すことを停止する工程とを含んでいる。その後エッチング層408は、所望の寸法にエッチングされる。

(もっと読む)

1 - 20 / 119

[ Back to top ]