半導体ウェハ端面の処理方法および半導体装置の製造方法

【課題】 ウェハ端面での反射防止膜のリンス処理により形成されたハンプ、又は該ハンプに起因するエッチング段差や膜残渣を除去し、ウェハ端面からの微小異物の飛散を防止する。

【解決手段】 半導体ウェハ111の端面において、半導体ウェハ111上に成膜された反射防止膜121、141の外周部をリンス処理により除去した後、反射防止膜121、141上に設けられたレジストパターン123、143を用いて、反射防止膜121、141及びその下地構造をエッチングする。リンス処理は、反射防止膜121、141の最外周部にハンプ122、142を生じさせ得る。上記エッチングの前又は後に、ウェハ端面において、ウェハ端面以外の領域にマスクを設けることなく、ハンプ122、142が形成された位置をエッチングする。

【解決手段】 半導体ウェハ111の端面において、半導体ウェハ111上に成膜された反射防止膜121、141の外周部をリンス処理により除去した後、反射防止膜121、141上に設けられたレジストパターン123、143を用いて、反射防止膜121、141及びその下地構造をエッチングする。リンス処理は、反射防止膜121、141の最外周部にハンプ122、142を生じさせ得る。上記エッチングの前又は後に、ウェハ端面において、ウェハ端面以外の領域にマスクを設けることなく、ハンプ122、142が形成された位置をエッチングする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、反射防止膜の成膜後の半導体ウェハの端面処理方法、及びそれを用いた半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の製造プロセスにおいては、種々のデバイスパターンの形成のために、一般に複数のフォトリソグラフィ工程が用いられている。フォトリソグラフィ工程は、半導体ウェハ等の基板上に塗布したフォトレジスト膜を、所望のパターンが形成されたマスク(レチクル)を介して露光し、その後に現像処理を行うことでレジストパターンを形成する。

【0003】

レジストパターンを所望のパターン通りに形成するために、少なくとも一部のフォトリソグラフィ工程においては、フォトレジスト膜の塗布に先立って反射防止膜(Bottom Anti-Reflection Coating;BARC)が成膜される。BARCは、フォトレジスト膜に入射した露光光が半導体ウェハ又はその上に形成された膜で反射すること、ひいては、入射光と反射光との干渉により露光パターンが変動することを防止する。近年の半導体装置の微細化に伴い、KrF又はArFエキシマレーザ光などの反射しやすい短波長光が露光光として用いられるようになり、ますます多くのフォトリソグラフィ工程でBARCが利用されるに至っている。

【0004】

また、半導体装置の微細化に伴い、微小な付着異物も無視できない状況になっている。このため、ウェハ面内の有効チップエリア内での異物発生のみならず、ウェハ端面(ベベル)での異物発生についても、その抑制が重要となっている。ウェハ端面で発生した異物も、後の工程で飛散し、有効チップエリア内に付着したり製造装置内の環境を汚染したりして、半導体装置の歩留まりを低下させるからである。

【0005】

一例として、シリコン(Si)ウェハに、シャロー・トレンチ・アイソレーション(STI)で素子分離された金属−酸化物−半導体電界効果トランジスタ(MOSFET)を形成するプロセスを考える。図1は、このプロセスの一典型例を、ウェハ端面付近の断面図で示している。

【0006】

先ず、図1(a)に示すように、フォトリソグラフィにより、Siウェハ11上にSTI形成部を定めるレジストパターン23を形成する。Siウェハ11上にはSiNストッパ膜12及びBARC21が形成されている。BARC21は、例えば有機膜であり、ウェハ端面において、エッジリンス(ER)やエッジバックリンス(EBR)等のリンス処理によって除去されている。しかしながら、このようなリンス処理は、BARC21の最外周部に、ハンプ(hump)と呼ばれる局部的にBARCが厚くなった箇所22を生じさせることが知られている。BARC21の厚さは例えば約75nmとすることができ、ハンプ22の高さはBARC21の厚さの2倍程度又はそれを超える高さになり得る。

【0007】

次いで、図1(b)に示すように、レジストパターン23をマスクとして、BARC21、SiN膜12及びSiウェハ11のエッチングを行い、Siウェハ11内にSTI用のトレンチ24を形成する。このとき、ハンプ22が形成されていた箇所で、BARC21及びSiN膜12それぞれの一部21’及び12’が残存する。また、これら膜残渣21’及び12’がマスクとして作用することにより、Siウェハ11の表面に段差24’が発生する。次に、図1(c)に示すように、アッシング等により、Siウェハ11の全面からレジストパターン23及びBARC21を除去する。

【0008】

次いで、図1(d)に示すように、STI25の完成後、酸化膜31、ポリSi膜32及びBARC41を形成し、フォトリソグラフィにより、ゲート電極形成用のレジストパターン43を形成する。BARC41は、BARC21と同様にEBR等のリンス処理を施され、最外周部にBARC41の厚さ(例えば約75nm)の約2倍以上の高さのハンプ42を有し得る。次に、図1(e)に示すように、レジストパターン43をマスクとして、異方性エッチングにより、BARC41、ポリSi膜32及び酸化膜31をエッチングし、ゲート電極32及びゲート酸化膜31を形成する。ハンプ42が存在していた箇所及びSiウェハ11の段差部分24’にポリSi残渣32’及び酸化膜残渣31’が発生する。

【0009】

次いで、図1(f)に示すように、アッシング等により、Siウェハ11の全面からレジストパターン43及びBARC41を除去する。そして、図1(g)に示すように、MOSFETのソース・ドレイン51のイオン注入を行う。この工程は、フォトレジストの塗布及び剥離を伴うが、アッシング等のレジスト剥離処理により、ポリSi残渣32’や酸化膜残渣31’が剥がれて飛散し得る。これらの残渣が飛散して有効チップエリア内のMOSFETに異物として付着すると、MOSFETの動作及び/又は信頼性が損なわれる。

【0010】

なお、図1(e)のゲートエッチングのオーバ量を追加した場合、ウェハ端面ではエッチングレートが低いため、ウェハ端面のポリSi残渣32’を完全に除去しようとすると有効チップエリア内のMOSFETにゲート細りの問題を生じさせる。また、ウェハ全面のバッチ式ウェット洗浄などによりこれらの残渣を完全に除去しようとしても、やはり、MOSFETのゲートにダメージを与えてしまう。従って、これらの手法を用いるためには、有効チップエリアを保護するための追加のマスク工程が必要になる。

【0011】

この問題の原因でもあるBARCのリンス処理によるハンプを除去することに関して、リンス処理に注目した方法が知られている。例えば、ウェハ端面に溶剤を滴下する第1のリンス工程の後に、該工程により形成されたハンプを、ウェハ回転数を上げることにより平坦化し、その後、ウェハ端面に溶剤を滴下する第2のリンス工程を行う手法が提案されている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2006−5344号公報

【特許文献2】特開2005−311339号公報

【特許文献3】特許第3348842号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、上記に示した、ハンプを平坦化した後にウェハ端面に溶剤を滴下する手法は、大口径ウェハにおいては実用的でない。例えば、300mmウェハにおいては、ウェハ外周から数十mmの領域でレジストの膜厚異常が発生する場合があり、また、レジスト端が波打つ現象を示す場合もある。更には、大口径になるほど、ウェハの回転数を増大させる点で制約が大きくなる。

【0014】

ウェハ端面でのBARCのリンス処理の後に、追加のマスク工程を必要とすることなく、該処理により形成されたハンプ、又は該ハンプに起因するエッチング段差や膜残渣を除去する方法、及びそれを用いた半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0015】

一観点によれば、半導体ウェハの端面において該半導体ウェハ上に成膜されたBARCの外周部をリンス処理により除去する工程を含むウェハ端面処理方法が提供される。このリンス工程により、BARCの最外周部にハンプが形成され得る。当該方法は更に、BARC上に設けられたレジストパターンを用いて、BARC及びその下地構造をエッチングする工程と、該工程の前又は後に、ウェハ端面において、ウェハ端面以外の領域にマスクを設けることなく、ハンプが形成された位置をエッチングする工程とを有する。

【0016】

他の一観点によれば、半導体装置形成領域及び端面を有する半導体ウェハの半導体装置形成領域に、フォトリソグラフィ工程を用いて、半導体装置を製造する方法が提供される。少なくとも1つのフォトリソグラフィ工程は、半導体ウェハ上にBARCを成膜する工程と、半導体ウェハの端面において、BARCの外周部をリンス処理により除去する工程とを有する。このリンス工程により、BARCの最外周部にハンプが形成され得る。当該製造方法は更に、BARC上に設けられたレジストパターンを用いて、BARC及びその下地構造をエッチングするエッチング工程と、該工程の前又は後に、ウェハ端面において、半導体装置形成領域にマスクを設けることなく、ハンプが形成された位置をエッチングする工程とを有する。

【発明の効果】

【0017】

BARCのリンス処理により形成されたハンプ、又は該ハンプに起因するエッチング段差や膜残渣がマスクレスで除去され、ウェハ端面からの微小異物の飛散が抑制される。

【図面の簡単な説明】

【0018】

【図1】従来技術に係る半導体装置の製造方法を例示するウェハ端面付近の断面図である。

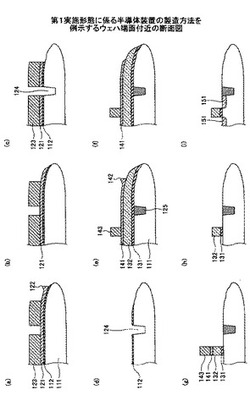

【図2】第1実施形態に係る半導体装置の製造方法を例示するウェハ端面付近の断面図である。

【図3】第2実施形態に係る半導体装置の製造方法を例示するウェハ端面付近の断面図である。

【図4】第3実施形態に係る半導体装置の製造方法を例示するウェハ端面付近の断面図である。

【図5】ウェハ端面のドライエッチングに使用し得るエッチング装置(ベベルエッチャー)を例示する断面図である。

【図6】ウェハ端面のウェットエッチング方法を例示する図である。

【図7】図5のエッチング装置のエッチング特性の一例を示す図である。

【図8】図5のエッチング装置のエッチング特性の他の一例を示す図である。

【発明を実施するための形態】

【0019】

以下、添付図面を参照しながら実施形態について詳細に説明する。なお、図面において、種々の構成要素は必ずしも同一の尺度で描かれていない。また、図面全体を通して、同一あるいは対応する構成要素には同一又は類似の参照符号を付する。

【0020】

(第1実施形態)

先ず、図2を参照して、第1実施形態に係るウェハ端面処理方法及び半導体装置の製造方法を説明する。図2は、Siウェハの有効チップエリア(半導体装置形成領域)にSTIで素子分離されたMOSFETを形成するプロセスの一典型例を、主な工程群におけるウェハ端面(ベベル)付近の断面図で示している。

【0021】

先ず、図2(a)に示すように、フォトリソグラフィにより、Siウェハ111上にSTI形成部を定めるレジストパターン123を形成する。Siウェハ111上には窒化膜(以下、SiN膜)112及びBARC121が形成されている。SiN膜112は例えば約100nmの厚さを有し、STI絶縁膜埋込後の平坦化時の研磨ストッパとして機能し得る。しかしながら、SiN膜112は使用するSTIプロセスに応じて省略され得る。レジストパターン123となるフォトレジスト膜は、例えば、250nmの厚さに塗布し得る。

【0022】

BARC121は、例えば有機膜であり、ウェハ端面において、薬液によるエッジリンス(ER)やエッジバックリンス(EBR)等のリンス処理によって除去されている。ウェハ搬送時やフォトレジストの剥離時に飛散して異物となることを防止するためである。BARC121の厚さは、露光波長などに応じて決定され、例えば約75nmとされ得る。EBR等のリンス処理はSiウェハ111の外周から例えば約1.0mmまでの領域で行う。このリンス処理により、BARC121の最外周部にはBARC121の厚さの2倍程度又はそれを超える高さのハンプ122が形成され得る。

【0023】

次いで、図2(b)に示すように、ハンプ122を除去する。この工程は、追加のマスクを用いることなく、Siウェハの外周部のみをエッチングするベベルエッチングにより行う。

【0024】

このエッチングは、例えば、図5に示すようなプラズマエッチング装置(ベベルエッチャー)500を用いたドライエッチングによって行い得る。装置500は、電極501、502、ウェハステージ503、プラズマ遮断板504、505、及びガス注入口506を含むセラミック板507を有する。電極501、502、及びウェハステージ503はAl等の金属で製造され、プラズマ遮断板504及び505はイットリア(Y2O3)等のセラミックで製造される。電極501、502とウェハステージ503との間には高周波パワーが印加される。

【0025】

ウェハステージ503の上面とセラミック板507の下面との間の距離d1、すなわち、エッチング対象のウェハ511が挿入される空間の高さは、例えば1mm−2mmとすることができる。この距離d1、及び/又はプラズマ遮断板504の外周とウェハ511の外周との間の距離d2を調整することにより、ウェハ511の有効チップエリアへのプラズマ508の回り込みを阻止し、ウェハ端面の所望の外周領域のみをエッチングすることができる。

【0026】

装置500にてBARC121(故に、ハンプ122)をエッチングするための処理条件は、例えば、d1:1.15mm、O2:200sccm、N2:150sccm、Ar:50sccm、圧力:1.9Torr、パワー:500Wとし得る。これにより発生したO2プラズマで、BARC121の最外周部を例えば厚さ80nmだけエッチングすることにより、ハンプ122を除去することが可能である。

【0027】

図7は、上記条件でのBARC121のエッチングレートとウェハ半径位置Rとの関係を示している。図7は更に、同条件での酸化膜(以下、SiO膜)、ポリSi膜、SiN膜のエッチングレートも示している。ただし、これらの結果はウェハの表面側(半導体装置形成側)で測定したものである。上記条件により、300mmウェハのR>147mmのウェハ端面部において、SiO、ポリSi及びSiNに対して高い選択比でBARCをエッチングすることができる。従って、上述のようなSiウェハ111の外周から約1.0mm(R=149mm)までの領域でのEBR処理により形成されたBARCハンプ122を、その下地のSiN膜112を有意にエッチングすることなく除去することが可能である。一方、有効チップエリアの最外周部は例えばR=146mmの半径位置とすることができ、有効チップエリア内のBARC121及びその上に形成されたレジストパターン123がエッチングされることはない。

【0028】

なお、図2(b)のハンプ除去工程は、図2(a)のBARC121のリンス処理後且つレジストパターン123の形成前に行ってもよい。また、本出願において、“ハンプを除去する”とは、ハンプによるBARC膜厚の増大が完全になくなるまで除去することに限られず、後のBARCエッチング工程において通常のオーバ条件でエッチングされ尽くす程度の厚みまで除去することをも含む。

【0029】

次いで、図2(c)に示すように、レジストパターン123をマスクとして、BARC121、SiN膜112及びSiウェハ111のエッチングを行い、Siウェハ111内にSTI用の溝(トレンチ)124を形成する。トレンチ124の深さは例えば約320nmとし得る。本実施形態においては、ハンプ122が既に除去されているので、レジストパターン123によって覆われていないBARC121及びSiN膜111を実質的に完全に除去することができる。

【0030】

次いで、図2(d)に示すように、アッシング等により、Siウェハ111の全面からレジストパターン123及びBARC121を除去する。ウェハ端面のハンプ122が存在していた箇所においても、Siウェハ111の表面に有意な段差は発生しない。

【0031】

次いで、図2(e)に示すように、STI125の完成後、SiO膜131、ポリSi膜132、及びBARC141を形成し、フォトリソグラフィにより、ゲート電極形成用のレジストパターン143を形成する。

【0032】

STI125の完成のため、先ず、例えば、トレンチ124に二酸化シリコン(SiO2)を充填し、化学的機械的研磨(CMP)法を用いて余分なSiO2を除去する。このとき、SiN膜112がストッパとして機能する。SiN膜112は、上記CMP又はそれに続くエッチングより除去される。なお、STI125の完成後、MOSFETのウェル注入やチャネル注入などのイオン注入工程を行い得る。

【0033】

SiO膜131は、後にMOSFETのゲート酸化膜となるものであり、例えば1.2nmの厚さを有する。ポリSi膜132は、後にMOSFETのゲート電極となるものであり、例えば100nmの厚さを有する。

【0034】

BARC141は、BARC121と同様にEBR等のリンス処理を施され、最外周部にBARC141の厚さ(例えば約75nm)の約2倍以上の高さのハンプ142を有し得る。

【0035】

次いで、図2(f)に示すように、ハンプ142を除去する。この工程は、図2(b)の工程と同様に、追加のマスクを用いることなく、Siウェハ111のベベルエッチングにより行い得る。例えば、O2プラズマでBARC141の最外周部を厚さ80nmだけエッチングする。図7を参照して説明したように、SiO及びポリSiに対して高い選択比でBARCをエッチングし得るエッチング条件を用い、下地のポリSi膜132及びSiO膜131を有意にエッチングすることなく、BARC141のみをエッチングしてもよい。

【0036】

なお、図2(f)のハンプ除去工程は、図2(e)のBARC141のリンス処理後且つレジストパターン143の形成前に行ってもよい。

【0037】

次いで、図2(g)に示すように、レジストパターン143をマスクとして、異方性エッチングにより、BARC141、ポリSi膜132及びSiO膜131をエッチングし、ゲート電極132及びゲート酸化膜131を形成する。本実施形態においては、ハンプ122の除去によりSiウェハ111の表面の段差が抑制されており、且つハンプ142が除去されているので、ハンプ122及び142が形成されていた箇所においても、ポリSi残渣及びSiO残渣の発生を抑制することができる。

【0038】

次いで、図2(h)に示すように、アッシング等により、Siウェハ111の全面からレジストパターン143及びBARC141を除去する。

【0039】

そして、図2(i)に示すように、MOSFETのソース・ドレイン(又は、LDDとも呼ばれるソース・ドレインエクステンション領域)151のイオン注入を行う。さらに、ゲート電極132の側壁スペーサの形成、ゲート電極132やソース・ドレイン151の表面のシリサイド化、バックエンド(配線)プロセス等を適宜行って、有効チップエリア内に半導体装置が完成される。

【0040】

本実施形態においては、BARC121のハンプ122、BARC141のハンプ142自体を、それぞれ、STI形成、ゲート形成のためのエッチングに先立って除去している。従って、STI形成時及びゲート形成時のエッチング工程において、従来見られたハンプに起因する段差や膜残渣の発生を防止し、異物の飛散を回避することができる。また、ハンプ122及び142の除去をウェハ端面のみをエッチングするベベルエッチングを用いて行うので、追加のマスク工程を必要とすることなく、有効チップエリア内のMOSFETのゲート等にダメージを与えることを回避し得る。

【0041】

(第2実施形態)

次に、図3を参照して、第2実施形態に係るウェハ端面処理方法及び半導体装置の製造方法を説明する。図3は、Siウェハの有効チップエリア(半導体装置形成領域)にSTIで素子分離されたMOSFETを形成するプロセスの一典型例を、主な工程群におけるウェハ端面(ベベル)付近の断面図で示している。なお、各種の膜の厚さやSTIの埋込工程など、第1実施形態と共通する事項の説明は省略する。

【0042】

先ず、図3(a)に示すように、フォトリソグラフィにより、Siウェハ211上にSTI形成部を定めるレジストパターン223を形成する。Siウェハ211上にはSiN膜212及びBARC221が形成されている。SiN膜212は、STI絶縁膜埋込後の平坦化時の研磨ストッパとして機能し得るが、使用するSTIプロセスに応じて省略され得る。

【0043】

BARC221は、ウェハ端面において、薬液によるエッジリンス(ER)やエッジバックリンス(EBR)等のリンス処理によって除去されている。EBR等のリンス処理はSiウェハ211の外周から例えば約1.0mmまでの領域で行う。このリンス処理により、BARC221の最外周部にはBARC221の厚さの2倍程度又はそれを超える高さのハンプ222が形成され得る。

【0044】

次いで、図3(b)に示すように、レジストパターン223をマスクとして、BARC221、SiN膜212、Siウェハ211のエッチングを行い、Siウェハ211内にSTI用のトレンチ224を形成する。このとき、ハンプ222が存在していた箇所で、BARC221及びSiN膜212それぞれの一部221’及び212’が残存し得る。また、これら膜残渣221’及び212’がマスクとして作用することにより、Siウェハ211の表面に段差224’が発生し得る。

【0045】

次いで、図3(c)に示すように、アッシング等により、Siウェハ211の全面からレジストパターン223及びBARC221(及び221’)を除去する。SiN膜残渣212’及びSiウェハ211の表面のSi段差224’は残存したままである。

【0046】

次いで、図3(d)に示すように、SiN膜残渣212’の除去及びSi段差224’の平滑化を行う。この工程は、追加のマスクを用いることなく、Siウェハ211の外周部のみをエッチングするベベルエッチングにより行う。

【0047】

このエッチングは、例えば、上述の図5のプラズマエッチング装置(ベベルエッチャー)500を用いたドライプロセスによって行い得る。この場合の装置500におけるエッチング条件は、例えば、d1:1.15mm、CF4:110sccm、N2:110sccm、圧力:1.9Torr、パワー:700Wとし得る。図8は、この条件でのSiO膜、ポリSi膜、SiN膜及びフォトレジスト(RES)膜のエッチングレートとウェハ半径位置Rとの関係を、ウェハの(a)表面(半導体装置形成側)及び(b)裏面のそれぞれについて示している。この条件により、300mmウェハにおいて、(a)表面ではR>148mm、(b)裏面ではR>146mmのウェハ端面部において、SiO、ポリSi、SiN及びフォトレジストを実質的に選択性なくエッチングすることができる。従って、上述のようなSiウェハ211の外周から約1.0mm(R=149mm)までの領域でのEBR処理により形成されたBARCハンプ222に起因するSiN膜残渣212’の除去及びSi段差224’の平滑化を、同一且つ単一のエッチング工程で行い得る。一方、有効チップエリアの最外周部は例えばR=146mmの半径位置とすることができ、有効チップエリア内のSiN膜212やトレンチ224がエッチングされることはない。

【0048】

また、図3(d)にて行うSiウェハ211の外周部のみのエッチング処理は、ウェットプロセスにて行うことも可能である。図6は、そのようなウェットエッチング処理に用い得る方法を概略的に示している。図6(a)は、N2を吹き当てた回転中のウェハ611の端面に、ウェハ611の上方に配置した薬液ノズル601から薬液を拭き付ける方法を示す。薬液としては、例えば、硫酸、硝酸、アンモニア、過酸化水素などを用い得る。図6(b)は、N2を吹き当てた回転中のウェハ611の端面に、ウェハ611の側方に配置した気化ノズル602から、図6(a)と同様の薬液を気化させて拭き付ける方法を示す。このような構成でウェットエッチングを行うことにより、Siウェハ211の有効チップエリアをエッチングすることなく、ウェハ端面のSi段差224’、SiN膜残渣212’、及び後述のポリSi膜残渣232’、SiO膜残渣231’を除去することができる。このようなウェットプロセスは、Si段差224’の平滑化の効果をドライプロセスの場合より高めることが可能である。

【0049】

次いで、図3(e)に示すように、STI225の完成後、SiO膜231、ポリSi膜232、及びBARC241を形成し、フォトリソグラフィにより、ゲート電極形成用のレジストパターン243を形成する。

【0050】

BARC241は、BARC221と同様にEBR等のリンス処理を施され、最外周部にBARC241の厚さ(例えば約75nm)の約2倍以上の高さのハンプ242を有し得る。

【0051】

次いで、図3(f)に示すように、レジストパターン243をマスクとして、異方性エッチングにより、BARC241、ポリSi膜232及びSiO膜231をエッチングし、ゲート電極232及びゲート酸化膜231を形成する。このとき、ハンプ242が存在していた箇所にポリSi残渣232’及びSiO膜残渣231’が発生し得る。なお、本実施形態においては、図3(d)にてSi段差224’が平滑化されているので、Si段差224’故にハンプ222に起因する残渣の発生は抑制されている。

【0052】

次いで、図3(g)に示すように、アッシング等により、Siウェハ211の全面からレジストパターン243及びBARC241を除去する。

【0053】

次いで、図3(h)に示すように、ポリSi膜残渣232’及びSiO膜残渣231’を除去する。この工程は、図3(d)の工程と同様にドライプロセス又はウェットプロセスを用いて、追加のマスクを用いることなく、Siウェハ211のベベルエッチングにより行い得る。例えば、図5のプラズマエッチング装置500及び上述のCF4/N2混合ガス条件を用いることができる。それにより、図8を参照して説明したように、ポリSi膜残渣232’及びSiO膜残渣231’を同一且つ単一のエッチング工程で除去し得る。

【0054】

なお、図3(h)の残渣除去工程は、図3(f)の工程と図3(g)の工程との間に行ってもよい。

【0055】

そして、図3(i)に示すように、MOSFETのソース・ドレイン251のイオン注入を行う。さらに、ゲート電極232の側壁スペーサの形成、ゲート電極232やソース・ドレイン251の表面のシリサイド化、バックエンド(配線)プロセス等を適宜行って、有効チップエリア内に半導体装置が完成される。

【0056】

本実施形態においては、BARC221のハンプ222、BARC241のハンプ242に起因して、それぞれ、STI形成、ゲート形成のためのエッチングにより発生した膜残渣を除去し、異物の飛散を回避することができる。また、膜残渣の除去をウェハ端面のみをエッチングするベベルエッチングを用いて行うので、追加のマスク工程を必要とすることなく、有効チップエリア内のMOSFETのゲート等にダメージを与えることを回避し得る。

【0057】

(第3実施形態)

次に、図4を参照して、第3実施形態に係るウェハ端面処理方法及び半導体装置の製造方法を説明する。図4は、Siウェハの有効チップエリア(半導体装置形成領域)にSTIで素子分離されたMOSFETを形成するプロセスの一典型例を、主な工程群におけるウェハ端面(ベベル)付近の断面図で示している。なお、各種の膜の厚さやSTIの埋込工程など、第1及び/又は第2実施形態と共通する事項の説明は省略する。

【0058】

図4(a)−(c)は、各構成要素の参照符号の一桁目を“3”に代えていることを除いて、図3(a)−(c)と同様である。BARC321のリンス処理によるハンプ322の形成箇所で、Siウェハ311の表面に段差324’が発生する。

【0059】

次いで、図4(d)に示すように、STI325の完成後、SiO膜331、ポリSi膜332、及びBARC341を形成し、フォトリソグラフィにより、ゲート電極形成用のレジストパターン343を形成する。BARC341は、BARC321と同様にEBR等のリンス処理を施され、最外周部にBARC41のハンプ342を有する。

【0060】

次いで、図4(e)に示すように、レジストパターン343をマスクとして、異方性エッチングにより、BARC341、ポリSi膜332及びSiO膜331をエッチングし、ゲート電極332及びゲート酸化膜331を形成する。ハンプ342が存在していた箇所及びSi段差324’にポリSi残渣332’及びSiO膜残渣331’が発生し得る。

【0061】

次いで、図4(f)に示すように、アッシング等により、Siウェハ311の全面からレジストパターン343及びBARC341を除去する。

【0062】

次いで、図4(g)に示すように、ポリSi膜残渣332’及びSiO膜残渣331’を除去する。この工程は、図3(d)、(h)に示した工程と同様にドライプロセス又はウェットプロセスを用いて、追加のマスクを用いることなく、Siウェハ311の外周部のみをエッチングするベベルエッチングにより行い得る。例えば、図5のプラズマエッチング装置500及び上述のCF4/N2混合ガス条件を用いることができる。それにより、図8を参照して説明したように、ポリSi膜残渣332’及びSiO膜残渣331’を同一且つ単一のエッチング工程で行い得る。

【0063】

なお、図4はハンプ322及び342の位置がウェハの径方向にずれているように示しているが、ハンプ322及び342は同一のウェハ半径位置に形成されてもよい。従って、第3実施形態においては、第2実施形態の残渣232’、231’より大きい残渣332’、331’が形成され得るが、エッチング時間を延長することにより、これらの残渣を実質的に完全に除去することができる。

【0064】

そして、図4(h)に示すように、MOSFETのソース・ドレイン351のイオン注入を行う。さらに、ゲート電極332の側壁スペーサの形成、ゲート電極332やソース・ドレイン351の表面のシリサイド化、バックエンド(配線)プロセス等を適宜行って、有効チップエリア内に半導体装置が完成される。

【0065】

本実施形態においては、ハンプ又はそれに起因する段差や膜残渣を除去するウェハ端面処理を、複数のパターニング工程に対して一度用いることにより、追加工程数を削減しながら第1及び第2の実施形態と同様の効果を得ることができる。

【0066】

以上、実施形態について詳述したが、本発明は特定の実施形態に限定されるものではなく、特許請求の範囲に記載された要旨の範囲内において、種々の変形及び変更が可能である。例えば、STI形成工程において第1実施形態におけるハンプ除去のための高選択性エッチングを用い、ゲート形成工程において第2実施形態における非選択性エッチングを用いる等、第1及び第2の実施形態は適宜組み合わせることが可能である。また、これらの実施形態が有するウェハ端面処理は、例えばバックエンドプロセスにおけるフォトリソグラフィ工程及び/又はそれに続くエッチング工程など、その他の半導体装置製造工程においても用いることができる。

【0067】

以上の説明に関し、更に以下の付記を開示する。

(付記1)

半導体ウェハの端面において、該半導体ウェハ上に成膜された反射防止膜の外周部をリンス処理により除去するリンス工程であり、前記反射防止膜の最外周部にハンプが形成されるリンス工程と、

前記反射防止膜上に設けられたレジストパターンを用いて、前記反射防止膜及びその下地構造をエッチングするエッチング工程と、

前記エッチング工程の前又は後に、前記端面において、前記端面以外の前記半導体ウェハの領域にマスクを設けることなく、前記ハンプが形成された位置をエッチングするベベルエッチング工程と、

を有するウェハ端面処理方法。

(付記2)

前記ベベルエッチング工程は前記エッチング工程の後に行われ、前記エッチング工程は前記ハンプが形成された位置で前記下地構造を構成する膜の一部を残存させ、前記ベベルエッチング工程は前記膜の一部を除去する、付記1に記載のウェハ端面処理方法。

(付記3)

前記ベベルエッチング工程は前記エッチング工程の後に行われ、前記エッチング工程は前記ハンプの位置で前記半導体ウェハの表面に段差を残存させ、前記ベベルエッチング工程は前記段差を除去する、付記1又は2に記載のウェハ端面処理方法。

(付記4)

前記ベベルエッチング工程は、ポリシリコン、窒化シリコン、及び酸化シリコンを選択性なくエッチングすることが可能である、付記2又は3に記載のウェハ端面処理方法。

(付記5)

前記ベベルエッチング工程は、前記エッチング工程の前に行われて前記ハンプを除去する、付記1に記載のウェハ端面処理方法。

(付記6)

前記ベベルエッチング工程はプラズマエッチングを用いる、付記1乃至5の何れか一に記載のウェハ端面処理方法。

(付記7)

前記ベベルエッチング工程はウェットエッチングを用いる、付記2乃至4の何れか一に記載のウェハ端面処理方法。

(付記8)

前記プラズマエッチングは、前記ハンプを前記下地構造に対して選択的にエッチングする、付記7に記載のウェハ端面処理方法。

(付記9)

半導体装置形成領域及び端面を有する半導体ウェハの前記半導体装置形成領域に、フォトリソグラフィ工程を用いて、半導体装置を製造する方法であって、

少なくとも1つのフォトリソグラフィ工程が、

前記半導体ウェハ上に反射防止膜を成膜する工程と、

前記端面において、前記反射防止膜の外周部をリンス処理により除去するリンス工程であり、前記反射防止膜の最外周部にハンプが形成されるリンス工程と、

前記反射防止膜上に設けられたレジストパターンを用いて、前記反射防止膜及びその下地構造をエッチングするエッチング工程と、

前記エッチング工程の前又は後に、前記端面において、前記半導体装置形成領域にマスクを設けることなく、前記ハンプが形成された位置をエッチングするベベルエッチング工程と、

を有する、半導体装置を製造する方法。

(付記10)

前記少なくとも1つのフォトリソグラフィ工程は、

前記エッチング工程において前記レジストパターンを用いて前記半導体装置のゲート電極を形成するフォトリソグラフィ工程

を含む、付記9に記載の半導体装置を製造する方法。

(付記11)

前記少なくとも1つのフォトリソグラフィ工程は更に、

前記エッチング工程において前記レジストパターンを用いて前記半導体ウェハ内に前記半導体装置のシャロー・トレンチ・アイソレーション用の溝を形成するフォトリソグラフィ工程

を含む、付記10に記載の半導体装置を製造する方法。

【符号の説明】

【0068】

111、211、311、511、611 半導体ウェハ

112、212、312 ストッパ膜(SiN膜)

121、141、221、241、321、341 反射防止膜(BARC)

122、142、222、242、322、342 ハンプ

123、143、223、243、323、343 レジストパターン

124、224、324 トレンチ

125、225、325 STI

131、231、331 ゲート酸化膜(SiO膜)

132、232、332 ゲート電極(ポリSi膜)

151、251、351 ソース・ドレイン

212’、221’、231’、232’、312’、321’、331’、332’ 残渣

224’、324’ 段差

500 プラズマエッチング装置(ベベルエッチャー)

501、502 電極

503 ウェハステージ

504 プラズマ遮断板

505 ガス注入口

601 薬液ノズル

602 気化ノズル

【技術分野】

【0001】

本発明は、反射防止膜の成膜後の半導体ウェハの端面処理方法、及びそれを用いた半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の製造プロセスにおいては、種々のデバイスパターンの形成のために、一般に複数のフォトリソグラフィ工程が用いられている。フォトリソグラフィ工程は、半導体ウェハ等の基板上に塗布したフォトレジスト膜を、所望のパターンが形成されたマスク(レチクル)を介して露光し、その後に現像処理を行うことでレジストパターンを形成する。

【0003】

レジストパターンを所望のパターン通りに形成するために、少なくとも一部のフォトリソグラフィ工程においては、フォトレジスト膜の塗布に先立って反射防止膜(Bottom Anti-Reflection Coating;BARC)が成膜される。BARCは、フォトレジスト膜に入射した露光光が半導体ウェハ又はその上に形成された膜で反射すること、ひいては、入射光と反射光との干渉により露光パターンが変動することを防止する。近年の半導体装置の微細化に伴い、KrF又はArFエキシマレーザ光などの反射しやすい短波長光が露光光として用いられるようになり、ますます多くのフォトリソグラフィ工程でBARCが利用されるに至っている。

【0004】

また、半導体装置の微細化に伴い、微小な付着異物も無視できない状況になっている。このため、ウェハ面内の有効チップエリア内での異物発生のみならず、ウェハ端面(ベベル)での異物発生についても、その抑制が重要となっている。ウェハ端面で発生した異物も、後の工程で飛散し、有効チップエリア内に付着したり製造装置内の環境を汚染したりして、半導体装置の歩留まりを低下させるからである。

【0005】

一例として、シリコン(Si)ウェハに、シャロー・トレンチ・アイソレーション(STI)で素子分離された金属−酸化物−半導体電界効果トランジスタ(MOSFET)を形成するプロセスを考える。図1は、このプロセスの一典型例を、ウェハ端面付近の断面図で示している。

【0006】

先ず、図1(a)に示すように、フォトリソグラフィにより、Siウェハ11上にSTI形成部を定めるレジストパターン23を形成する。Siウェハ11上にはSiNストッパ膜12及びBARC21が形成されている。BARC21は、例えば有機膜であり、ウェハ端面において、エッジリンス(ER)やエッジバックリンス(EBR)等のリンス処理によって除去されている。しかしながら、このようなリンス処理は、BARC21の最外周部に、ハンプ(hump)と呼ばれる局部的にBARCが厚くなった箇所22を生じさせることが知られている。BARC21の厚さは例えば約75nmとすることができ、ハンプ22の高さはBARC21の厚さの2倍程度又はそれを超える高さになり得る。

【0007】

次いで、図1(b)に示すように、レジストパターン23をマスクとして、BARC21、SiN膜12及びSiウェハ11のエッチングを行い、Siウェハ11内にSTI用のトレンチ24を形成する。このとき、ハンプ22が形成されていた箇所で、BARC21及びSiN膜12それぞれの一部21’及び12’が残存する。また、これら膜残渣21’及び12’がマスクとして作用することにより、Siウェハ11の表面に段差24’が発生する。次に、図1(c)に示すように、アッシング等により、Siウェハ11の全面からレジストパターン23及びBARC21を除去する。

【0008】

次いで、図1(d)に示すように、STI25の完成後、酸化膜31、ポリSi膜32及びBARC41を形成し、フォトリソグラフィにより、ゲート電極形成用のレジストパターン43を形成する。BARC41は、BARC21と同様にEBR等のリンス処理を施され、最外周部にBARC41の厚さ(例えば約75nm)の約2倍以上の高さのハンプ42を有し得る。次に、図1(e)に示すように、レジストパターン43をマスクとして、異方性エッチングにより、BARC41、ポリSi膜32及び酸化膜31をエッチングし、ゲート電極32及びゲート酸化膜31を形成する。ハンプ42が存在していた箇所及びSiウェハ11の段差部分24’にポリSi残渣32’及び酸化膜残渣31’が発生する。

【0009】

次いで、図1(f)に示すように、アッシング等により、Siウェハ11の全面からレジストパターン43及びBARC41を除去する。そして、図1(g)に示すように、MOSFETのソース・ドレイン51のイオン注入を行う。この工程は、フォトレジストの塗布及び剥離を伴うが、アッシング等のレジスト剥離処理により、ポリSi残渣32’や酸化膜残渣31’が剥がれて飛散し得る。これらの残渣が飛散して有効チップエリア内のMOSFETに異物として付着すると、MOSFETの動作及び/又は信頼性が損なわれる。

【0010】

なお、図1(e)のゲートエッチングのオーバ量を追加した場合、ウェハ端面ではエッチングレートが低いため、ウェハ端面のポリSi残渣32’を完全に除去しようとすると有効チップエリア内のMOSFETにゲート細りの問題を生じさせる。また、ウェハ全面のバッチ式ウェット洗浄などによりこれらの残渣を完全に除去しようとしても、やはり、MOSFETのゲートにダメージを与えてしまう。従って、これらの手法を用いるためには、有効チップエリアを保護するための追加のマスク工程が必要になる。

【0011】

この問題の原因でもあるBARCのリンス処理によるハンプを除去することに関して、リンス処理に注目した方法が知られている。例えば、ウェハ端面に溶剤を滴下する第1のリンス工程の後に、該工程により形成されたハンプを、ウェハ回転数を上げることにより平坦化し、その後、ウェハ端面に溶剤を滴下する第2のリンス工程を行う手法が提案されている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2006−5344号公報

【特許文献2】特開2005−311339号公報

【特許文献3】特許第3348842号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、上記に示した、ハンプを平坦化した後にウェハ端面に溶剤を滴下する手法は、大口径ウェハにおいては実用的でない。例えば、300mmウェハにおいては、ウェハ外周から数十mmの領域でレジストの膜厚異常が発生する場合があり、また、レジスト端が波打つ現象を示す場合もある。更には、大口径になるほど、ウェハの回転数を増大させる点で制約が大きくなる。

【0014】

ウェハ端面でのBARCのリンス処理の後に、追加のマスク工程を必要とすることなく、該処理により形成されたハンプ、又は該ハンプに起因するエッチング段差や膜残渣を除去する方法、及びそれを用いた半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0015】

一観点によれば、半導体ウェハの端面において該半導体ウェハ上に成膜されたBARCの外周部をリンス処理により除去する工程を含むウェハ端面処理方法が提供される。このリンス工程により、BARCの最外周部にハンプが形成され得る。当該方法は更に、BARC上に設けられたレジストパターンを用いて、BARC及びその下地構造をエッチングする工程と、該工程の前又は後に、ウェハ端面において、ウェハ端面以外の領域にマスクを設けることなく、ハンプが形成された位置をエッチングする工程とを有する。

【0016】

他の一観点によれば、半導体装置形成領域及び端面を有する半導体ウェハの半導体装置形成領域に、フォトリソグラフィ工程を用いて、半導体装置を製造する方法が提供される。少なくとも1つのフォトリソグラフィ工程は、半導体ウェハ上にBARCを成膜する工程と、半導体ウェハの端面において、BARCの外周部をリンス処理により除去する工程とを有する。このリンス工程により、BARCの最外周部にハンプが形成され得る。当該製造方法は更に、BARC上に設けられたレジストパターンを用いて、BARC及びその下地構造をエッチングするエッチング工程と、該工程の前又は後に、ウェハ端面において、半導体装置形成領域にマスクを設けることなく、ハンプが形成された位置をエッチングする工程とを有する。

【発明の効果】

【0017】

BARCのリンス処理により形成されたハンプ、又は該ハンプに起因するエッチング段差や膜残渣がマスクレスで除去され、ウェハ端面からの微小異物の飛散が抑制される。

【図面の簡単な説明】

【0018】

【図1】従来技術に係る半導体装置の製造方法を例示するウェハ端面付近の断面図である。

【図2】第1実施形態に係る半導体装置の製造方法を例示するウェハ端面付近の断面図である。

【図3】第2実施形態に係る半導体装置の製造方法を例示するウェハ端面付近の断面図である。

【図4】第3実施形態に係る半導体装置の製造方法を例示するウェハ端面付近の断面図である。

【図5】ウェハ端面のドライエッチングに使用し得るエッチング装置(ベベルエッチャー)を例示する断面図である。

【図6】ウェハ端面のウェットエッチング方法を例示する図である。

【図7】図5のエッチング装置のエッチング特性の一例を示す図である。

【図8】図5のエッチング装置のエッチング特性の他の一例を示す図である。

【発明を実施するための形態】

【0019】

以下、添付図面を参照しながら実施形態について詳細に説明する。なお、図面において、種々の構成要素は必ずしも同一の尺度で描かれていない。また、図面全体を通して、同一あるいは対応する構成要素には同一又は類似の参照符号を付する。

【0020】

(第1実施形態)

先ず、図2を参照して、第1実施形態に係るウェハ端面処理方法及び半導体装置の製造方法を説明する。図2は、Siウェハの有効チップエリア(半導体装置形成領域)にSTIで素子分離されたMOSFETを形成するプロセスの一典型例を、主な工程群におけるウェハ端面(ベベル)付近の断面図で示している。

【0021】

先ず、図2(a)に示すように、フォトリソグラフィにより、Siウェハ111上にSTI形成部を定めるレジストパターン123を形成する。Siウェハ111上には窒化膜(以下、SiN膜)112及びBARC121が形成されている。SiN膜112は例えば約100nmの厚さを有し、STI絶縁膜埋込後の平坦化時の研磨ストッパとして機能し得る。しかしながら、SiN膜112は使用するSTIプロセスに応じて省略され得る。レジストパターン123となるフォトレジスト膜は、例えば、250nmの厚さに塗布し得る。

【0022】

BARC121は、例えば有機膜であり、ウェハ端面において、薬液によるエッジリンス(ER)やエッジバックリンス(EBR)等のリンス処理によって除去されている。ウェハ搬送時やフォトレジストの剥離時に飛散して異物となることを防止するためである。BARC121の厚さは、露光波長などに応じて決定され、例えば約75nmとされ得る。EBR等のリンス処理はSiウェハ111の外周から例えば約1.0mmまでの領域で行う。このリンス処理により、BARC121の最外周部にはBARC121の厚さの2倍程度又はそれを超える高さのハンプ122が形成され得る。

【0023】

次いで、図2(b)に示すように、ハンプ122を除去する。この工程は、追加のマスクを用いることなく、Siウェハの外周部のみをエッチングするベベルエッチングにより行う。

【0024】

このエッチングは、例えば、図5に示すようなプラズマエッチング装置(ベベルエッチャー)500を用いたドライエッチングによって行い得る。装置500は、電極501、502、ウェハステージ503、プラズマ遮断板504、505、及びガス注入口506を含むセラミック板507を有する。電極501、502、及びウェハステージ503はAl等の金属で製造され、プラズマ遮断板504及び505はイットリア(Y2O3)等のセラミックで製造される。電極501、502とウェハステージ503との間には高周波パワーが印加される。

【0025】

ウェハステージ503の上面とセラミック板507の下面との間の距離d1、すなわち、エッチング対象のウェハ511が挿入される空間の高さは、例えば1mm−2mmとすることができる。この距離d1、及び/又はプラズマ遮断板504の外周とウェハ511の外周との間の距離d2を調整することにより、ウェハ511の有効チップエリアへのプラズマ508の回り込みを阻止し、ウェハ端面の所望の外周領域のみをエッチングすることができる。

【0026】

装置500にてBARC121(故に、ハンプ122)をエッチングするための処理条件は、例えば、d1:1.15mm、O2:200sccm、N2:150sccm、Ar:50sccm、圧力:1.9Torr、パワー:500Wとし得る。これにより発生したO2プラズマで、BARC121の最外周部を例えば厚さ80nmだけエッチングすることにより、ハンプ122を除去することが可能である。

【0027】

図7は、上記条件でのBARC121のエッチングレートとウェハ半径位置Rとの関係を示している。図7は更に、同条件での酸化膜(以下、SiO膜)、ポリSi膜、SiN膜のエッチングレートも示している。ただし、これらの結果はウェハの表面側(半導体装置形成側)で測定したものである。上記条件により、300mmウェハのR>147mmのウェハ端面部において、SiO、ポリSi及びSiNに対して高い選択比でBARCをエッチングすることができる。従って、上述のようなSiウェハ111の外周から約1.0mm(R=149mm)までの領域でのEBR処理により形成されたBARCハンプ122を、その下地のSiN膜112を有意にエッチングすることなく除去することが可能である。一方、有効チップエリアの最外周部は例えばR=146mmの半径位置とすることができ、有効チップエリア内のBARC121及びその上に形成されたレジストパターン123がエッチングされることはない。

【0028】

なお、図2(b)のハンプ除去工程は、図2(a)のBARC121のリンス処理後且つレジストパターン123の形成前に行ってもよい。また、本出願において、“ハンプを除去する”とは、ハンプによるBARC膜厚の増大が完全になくなるまで除去することに限られず、後のBARCエッチング工程において通常のオーバ条件でエッチングされ尽くす程度の厚みまで除去することをも含む。

【0029】

次いで、図2(c)に示すように、レジストパターン123をマスクとして、BARC121、SiN膜112及びSiウェハ111のエッチングを行い、Siウェハ111内にSTI用の溝(トレンチ)124を形成する。トレンチ124の深さは例えば約320nmとし得る。本実施形態においては、ハンプ122が既に除去されているので、レジストパターン123によって覆われていないBARC121及びSiN膜111を実質的に完全に除去することができる。

【0030】

次いで、図2(d)に示すように、アッシング等により、Siウェハ111の全面からレジストパターン123及びBARC121を除去する。ウェハ端面のハンプ122が存在していた箇所においても、Siウェハ111の表面に有意な段差は発生しない。

【0031】

次いで、図2(e)に示すように、STI125の完成後、SiO膜131、ポリSi膜132、及びBARC141を形成し、フォトリソグラフィにより、ゲート電極形成用のレジストパターン143を形成する。

【0032】

STI125の完成のため、先ず、例えば、トレンチ124に二酸化シリコン(SiO2)を充填し、化学的機械的研磨(CMP)法を用いて余分なSiO2を除去する。このとき、SiN膜112がストッパとして機能する。SiN膜112は、上記CMP又はそれに続くエッチングより除去される。なお、STI125の完成後、MOSFETのウェル注入やチャネル注入などのイオン注入工程を行い得る。

【0033】

SiO膜131は、後にMOSFETのゲート酸化膜となるものであり、例えば1.2nmの厚さを有する。ポリSi膜132は、後にMOSFETのゲート電極となるものであり、例えば100nmの厚さを有する。

【0034】

BARC141は、BARC121と同様にEBR等のリンス処理を施され、最外周部にBARC141の厚さ(例えば約75nm)の約2倍以上の高さのハンプ142を有し得る。

【0035】

次いで、図2(f)に示すように、ハンプ142を除去する。この工程は、図2(b)の工程と同様に、追加のマスクを用いることなく、Siウェハ111のベベルエッチングにより行い得る。例えば、O2プラズマでBARC141の最外周部を厚さ80nmだけエッチングする。図7を参照して説明したように、SiO及びポリSiに対して高い選択比でBARCをエッチングし得るエッチング条件を用い、下地のポリSi膜132及びSiO膜131を有意にエッチングすることなく、BARC141のみをエッチングしてもよい。

【0036】

なお、図2(f)のハンプ除去工程は、図2(e)のBARC141のリンス処理後且つレジストパターン143の形成前に行ってもよい。

【0037】

次いで、図2(g)に示すように、レジストパターン143をマスクとして、異方性エッチングにより、BARC141、ポリSi膜132及びSiO膜131をエッチングし、ゲート電極132及びゲート酸化膜131を形成する。本実施形態においては、ハンプ122の除去によりSiウェハ111の表面の段差が抑制されており、且つハンプ142が除去されているので、ハンプ122及び142が形成されていた箇所においても、ポリSi残渣及びSiO残渣の発生を抑制することができる。

【0038】

次いで、図2(h)に示すように、アッシング等により、Siウェハ111の全面からレジストパターン143及びBARC141を除去する。

【0039】

そして、図2(i)に示すように、MOSFETのソース・ドレイン(又は、LDDとも呼ばれるソース・ドレインエクステンション領域)151のイオン注入を行う。さらに、ゲート電極132の側壁スペーサの形成、ゲート電極132やソース・ドレイン151の表面のシリサイド化、バックエンド(配線)プロセス等を適宜行って、有効チップエリア内に半導体装置が完成される。

【0040】

本実施形態においては、BARC121のハンプ122、BARC141のハンプ142自体を、それぞれ、STI形成、ゲート形成のためのエッチングに先立って除去している。従って、STI形成時及びゲート形成時のエッチング工程において、従来見られたハンプに起因する段差や膜残渣の発生を防止し、異物の飛散を回避することができる。また、ハンプ122及び142の除去をウェハ端面のみをエッチングするベベルエッチングを用いて行うので、追加のマスク工程を必要とすることなく、有効チップエリア内のMOSFETのゲート等にダメージを与えることを回避し得る。

【0041】

(第2実施形態)

次に、図3を参照して、第2実施形態に係るウェハ端面処理方法及び半導体装置の製造方法を説明する。図3は、Siウェハの有効チップエリア(半導体装置形成領域)にSTIで素子分離されたMOSFETを形成するプロセスの一典型例を、主な工程群におけるウェハ端面(ベベル)付近の断面図で示している。なお、各種の膜の厚さやSTIの埋込工程など、第1実施形態と共通する事項の説明は省略する。

【0042】

先ず、図3(a)に示すように、フォトリソグラフィにより、Siウェハ211上にSTI形成部を定めるレジストパターン223を形成する。Siウェハ211上にはSiN膜212及びBARC221が形成されている。SiN膜212は、STI絶縁膜埋込後の平坦化時の研磨ストッパとして機能し得るが、使用するSTIプロセスに応じて省略され得る。

【0043】

BARC221は、ウェハ端面において、薬液によるエッジリンス(ER)やエッジバックリンス(EBR)等のリンス処理によって除去されている。EBR等のリンス処理はSiウェハ211の外周から例えば約1.0mmまでの領域で行う。このリンス処理により、BARC221の最外周部にはBARC221の厚さの2倍程度又はそれを超える高さのハンプ222が形成され得る。

【0044】

次いで、図3(b)に示すように、レジストパターン223をマスクとして、BARC221、SiN膜212、Siウェハ211のエッチングを行い、Siウェハ211内にSTI用のトレンチ224を形成する。このとき、ハンプ222が存在していた箇所で、BARC221及びSiN膜212それぞれの一部221’及び212’が残存し得る。また、これら膜残渣221’及び212’がマスクとして作用することにより、Siウェハ211の表面に段差224’が発生し得る。

【0045】

次いで、図3(c)に示すように、アッシング等により、Siウェハ211の全面からレジストパターン223及びBARC221(及び221’)を除去する。SiN膜残渣212’及びSiウェハ211の表面のSi段差224’は残存したままである。

【0046】

次いで、図3(d)に示すように、SiN膜残渣212’の除去及びSi段差224’の平滑化を行う。この工程は、追加のマスクを用いることなく、Siウェハ211の外周部のみをエッチングするベベルエッチングにより行う。

【0047】

このエッチングは、例えば、上述の図5のプラズマエッチング装置(ベベルエッチャー)500を用いたドライプロセスによって行い得る。この場合の装置500におけるエッチング条件は、例えば、d1:1.15mm、CF4:110sccm、N2:110sccm、圧力:1.9Torr、パワー:700Wとし得る。図8は、この条件でのSiO膜、ポリSi膜、SiN膜及びフォトレジスト(RES)膜のエッチングレートとウェハ半径位置Rとの関係を、ウェハの(a)表面(半導体装置形成側)及び(b)裏面のそれぞれについて示している。この条件により、300mmウェハにおいて、(a)表面ではR>148mm、(b)裏面ではR>146mmのウェハ端面部において、SiO、ポリSi、SiN及びフォトレジストを実質的に選択性なくエッチングすることができる。従って、上述のようなSiウェハ211の外周から約1.0mm(R=149mm)までの領域でのEBR処理により形成されたBARCハンプ222に起因するSiN膜残渣212’の除去及びSi段差224’の平滑化を、同一且つ単一のエッチング工程で行い得る。一方、有効チップエリアの最外周部は例えばR=146mmの半径位置とすることができ、有効チップエリア内のSiN膜212やトレンチ224がエッチングされることはない。

【0048】

また、図3(d)にて行うSiウェハ211の外周部のみのエッチング処理は、ウェットプロセスにて行うことも可能である。図6は、そのようなウェットエッチング処理に用い得る方法を概略的に示している。図6(a)は、N2を吹き当てた回転中のウェハ611の端面に、ウェハ611の上方に配置した薬液ノズル601から薬液を拭き付ける方法を示す。薬液としては、例えば、硫酸、硝酸、アンモニア、過酸化水素などを用い得る。図6(b)は、N2を吹き当てた回転中のウェハ611の端面に、ウェハ611の側方に配置した気化ノズル602から、図6(a)と同様の薬液を気化させて拭き付ける方法を示す。このような構成でウェットエッチングを行うことにより、Siウェハ211の有効チップエリアをエッチングすることなく、ウェハ端面のSi段差224’、SiN膜残渣212’、及び後述のポリSi膜残渣232’、SiO膜残渣231’を除去することができる。このようなウェットプロセスは、Si段差224’の平滑化の効果をドライプロセスの場合より高めることが可能である。

【0049】

次いで、図3(e)に示すように、STI225の完成後、SiO膜231、ポリSi膜232、及びBARC241を形成し、フォトリソグラフィにより、ゲート電極形成用のレジストパターン243を形成する。

【0050】

BARC241は、BARC221と同様にEBR等のリンス処理を施され、最外周部にBARC241の厚さ(例えば約75nm)の約2倍以上の高さのハンプ242を有し得る。

【0051】

次いで、図3(f)に示すように、レジストパターン243をマスクとして、異方性エッチングにより、BARC241、ポリSi膜232及びSiO膜231をエッチングし、ゲート電極232及びゲート酸化膜231を形成する。このとき、ハンプ242が存在していた箇所にポリSi残渣232’及びSiO膜残渣231’が発生し得る。なお、本実施形態においては、図3(d)にてSi段差224’が平滑化されているので、Si段差224’故にハンプ222に起因する残渣の発生は抑制されている。

【0052】

次いで、図3(g)に示すように、アッシング等により、Siウェハ211の全面からレジストパターン243及びBARC241を除去する。

【0053】

次いで、図3(h)に示すように、ポリSi膜残渣232’及びSiO膜残渣231’を除去する。この工程は、図3(d)の工程と同様にドライプロセス又はウェットプロセスを用いて、追加のマスクを用いることなく、Siウェハ211のベベルエッチングにより行い得る。例えば、図5のプラズマエッチング装置500及び上述のCF4/N2混合ガス条件を用いることができる。それにより、図8を参照して説明したように、ポリSi膜残渣232’及びSiO膜残渣231’を同一且つ単一のエッチング工程で除去し得る。

【0054】

なお、図3(h)の残渣除去工程は、図3(f)の工程と図3(g)の工程との間に行ってもよい。

【0055】

そして、図3(i)に示すように、MOSFETのソース・ドレイン251のイオン注入を行う。さらに、ゲート電極232の側壁スペーサの形成、ゲート電極232やソース・ドレイン251の表面のシリサイド化、バックエンド(配線)プロセス等を適宜行って、有効チップエリア内に半導体装置が完成される。

【0056】

本実施形態においては、BARC221のハンプ222、BARC241のハンプ242に起因して、それぞれ、STI形成、ゲート形成のためのエッチングにより発生した膜残渣を除去し、異物の飛散を回避することができる。また、膜残渣の除去をウェハ端面のみをエッチングするベベルエッチングを用いて行うので、追加のマスク工程を必要とすることなく、有効チップエリア内のMOSFETのゲート等にダメージを与えることを回避し得る。

【0057】

(第3実施形態)

次に、図4を参照して、第3実施形態に係るウェハ端面処理方法及び半導体装置の製造方法を説明する。図4は、Siウェハの有効チップエリア(半導体装置形成領域)にSTIで素子分離されたMOSFETを形成するプロセスの一典型例を、主な工程群におけるウェハ端面(ベベル)付近の断面図で示している。なお、各種の膜の厚さやSTIの埋込工程など、第1及び/又は第2実施形態と共通する事項の説明は省略する。

【0058】

図4(a)−(c)は、各構成要素の参照符号の一桁目を“3”に代えていることを除いて、図3(a)−(c)と同様である。BARC321のリンス処理によるハンプ322の形成箇所で、Siウェハ311の表面に段差324’が発生する。

【0059】

次いで、図4(d)に示すように、STI325の完成後、SiO膜331、ポリSi膜332、及びBARC341を形成し、フォトリソグラフィにより、ゲート電極形成用のレジストパターン343を形成する。BARC341は、BARC321と同様にEBR等のリンス処理を施され、最外周部にBARC41のハンプ342を有する。

【0060】

次いで、図4(e)に示すように、レジストパターン343をマスクとして、異方性エッチングにより、BARC341、ポリSi膜332及びSiO膜331をエッチングし、ゲート電極332及びゲート酸化膜331を形成する。ハンプ342が存在していた箇所及びSi段差324’にポリSi残渣332’及びSiO膜残渣331’が発生し得る。

【0061】

次いで、図4(f)に示すように、アッシング等により、Siウェハ311の全面からレジストパターン343及びBARC341を除去する。

【0062】

次いで、図4(g)に示すように、ポリSi膜残渣332’及びSiO膜残渣331’を除去する。この工程は、図3(d)、(h)に示した工程と同様にドライプロセス又はウェットプロセスを用いて、追加のマスクを用いることなく、Siウェハ311の外周部のみをエッチングするベベルエッチングにより行い得る。例えば、図5のプラズマエッチング装置500及び上述のCF4/N2混合ガス条件を用いることができる。それにより、図8を参照して説明したように、ポリSi膜残渣332’及びSiO膜残渣331’を同一且つ単一のエッチング工程で行い得る。

【0063】

なお、図4はハンプ322及び342の位置がウェハの径方向にずれているように示しているが、ハンプ322及び342は同一のウェハ半径位置に形成されてもよい。従って、第3実施形態においては、第2実施形態の残渣232’、231’より大きい残渣332’、331’が形成され得るが、エッチング時間を延長することにより、これらの残渣を実質的に完全に除去することができる。

【0064】

そして、図4(h)に示すように、MOSFETのソース・ドレイン351のイオン注入を行う。さらに、ゲート電極332の側壁スペーサの形成、ゲート電極332やソース・ドレイン351の表面のシリサイド化、バックエンド(配線)プロセス等を適宜行って、有効チップエリア内に半導体装置が完成される。

【0065】

本実施形態においては、ハンプ又はそれに起因する段差や膜残渣を除去するウェハ端面処理を、複数のパターニング工程に対して一度用いることにより、追加工程数を削減しながら第1及び第2の実施形態と同様の効果を得ることができる。

【0066】

以上、実施形態について詳述したが、本発明は特定の実施形態に限定されるものではなく、特許請求の範囲に記載された要旨の範囲内において、種々の変形及び変更が可能である。例えば、STI形成工程において第1実施形態におけるハンプ除去のための高選択性エッチングを用い、ゲート形成工程において第2実施形態における非選択性エッチングを用いる等、第1及び第2の実施形態は適宜組み合わせることが可能である。また、これらの実施形態が有するウェハ端面処理は、例えばバックエンドプロセスにおけるフォトリソグラフィ工程及び/又はそれに続くエッチング工程など、その他の半導体装置製造工程においても用いることができる。

【0067】

以上の説明に関し、更に以下の付記を開示する。

(付記1)

半導体ウェハの端面において、該半導体ウェハ上に成膜された反射防止膜の外周部をリンス処理により除去するリンス工程であり、前記反射防止膜の最外周部にハンプが形成されるリンス工程と、

前記反射防止膜上に設けられたレジストパターンを用いて、前記反射防止膜及びその下地構造をエッチングするエッチング工程と、

前記エッチング工程の前又は後に、前記端面において、前記端面以外の前記半導体ウェハの領域にマスクを設けることなく、前記ハンプが形成された位置をエッチングするベベルエッチング工程と、

を有するウェハ端面処理方法。

(付記2)

前記ベベルエッチング工程は前記エッチング工程の後に行われ、前記エッチング工程は前記ハンプが形成された位置で前記下地構造を構成する膜の一部を残存させ、前記ベベルエッチング工程は前記膜の一部を除去する、付記1に記載のウェハ端面処理方法。

(付記3)

前記ベベルエッチング工程は前記エッチング工程の後に行われ、前記エッチング工程は前記ハンプの位置で前記半導体ウェハの表面に段差を残存させ、前記ベベルエッチング工程は前記段差を除去する、付記1又は2に記載のウェハ端面処理方法。

(付記4)

前記ベベルエッチング工程は、ポリシリコン、窒化シリコン、及び酸化シリコンを選択性なくエッチングすることが可能である、付記2又は3に記載のウェハ端面処理方法。

(付記5)

前記ベベルエッチング工程は、前記エッチング工程の前に行われて前記ハンプを除去する、付記1に記載のウェハ端面処理方法。

(付記6)

前記ベベルエッチング工程はプラズマエッチングを用いる、付記1乃至5の何れか一に記載のウェハ端面処理方法。

(付記7)

前記ベベルエッチング工程はウェットエッチングを用いる、付記2乃至4の何れか一に記載のウェハ端面処理方法。

(付記8)

前記プラズマエッチングは、前記ハンプを前記下地構造に対して選択的にエッチングする、付記7に記載のウェハ端面処理方法。

(付記9)

半導体装置形成領域及び端面を有する半導体ウェハの前記半導体装置形成領域に、フォトリソグラフィ工程を用いて、半導体装置を製造する方法であって、

少なくとも1つのフォトリソグラフィ工程が、

前記半導体ウェハ上に反射防止膜を成膜する工程と、

前記端面において、前記反射防止膜の外周部をリンス処理により除去するリンス工程であり、前記反射防止膜の最外周部にハンプが形成されるリンス工程と、

前記反射防止膜上に設けられたレジストパターンを用いて、前記反射防止膜及びその下地構造をエッチングするエッチング工程と、

前記エッチング工程の前又は後に、前記端面において、前記半導体装置形成領域にマスクを設けることなく、前記ハンプが形成された位置をエッチングするベベルエッチング工程と、

を有する、半導体装置を製造する方法。

(付記10)

前記少なくとも1つのフォトリソグラフィ工程は、

前記エッチング工程において前記レジストパターンを用いて前記半導体装置のゲート電極を形成するフォトリソグラフィ工程

を含む、付記9に記載の半導体装置を製造する方法。

(付記11)

前記少なくとも1つのフォトリソグラフィ工程は更に、

前記エッチング工程において前記レジストパターンを用いて前記半導体ウェハ内に前記半導体装置のシャロー・トレンチ・アイソレーション用の溝を形成するフォトリソグラフィ工程

を含む、付記10に記載の半導体装置を製造する方法。

【符号の説明】

【0068】

111、211、311、511、611 半導体ウェハ

112、212、312 ストッパ膜(SiN膜)

121、141、221、241、321、341 反射防止膜(BARC)

122、142、222、242、322、342 ハンプ

123、143、223、243、323、343 レジストパターン

124、224、324 トレンチ

125、225、325 STI

131、231、331 ゲート酸化膜(SiO膜)

132、232、332 ゲート電極(ポリSi膜)

151、251、351 ソース・ドレイン

212’、221’、231’、232’、312’、321’、331’、332’ 残渣

224’、324’ 段差

500 プラズマエッチング装置(ベベルエッチャー)

501、502 電極

503 ウェハステージ

504 プラズマ遮断板

505 ガス注入口

601 薬液ノズル

602 気化ノズル

【特許請求の範囲】

【請求項1】

半導体ウェハの端面において、該半導体ウェハ上に成膜された反射防止膜の外周部をリンス処理により除去するリンス工程であり、前記反射防止膜の最外周部にハンプが形成されるリンス工程と、

前記反射防止膜上に設けられたレジストパターンを用いて、前記反射防止膜及びその下地構造をエッチングするエッチング工程と、

前記エッチング工程の前又は後に、前記端面において、前記端面以外の前記半導体ウェハの領域にマスクを設けることなく、前記ハンプが形成された位置をエッチングするベベルエッチング工程と、

を有するウェハ端面処理方法。

【請求項2】

前記ベベルエッチング工程は前記エッチング工程の後に行われ、前記エッチング工程は前記ハンプが形成された位置で前記下地構造を構成する膜の一部を残存させ、前記ベベルエッチング工程は前記膜の一部を除去する、請求項1に記載のウェハ端面処理方法。

【請求項3】

前記ベベルエッチング工程は、前記エッチング工程の前に行われて前記ハンプを除去する、請求項1に記載のウェハ端面処理方法。

【請求項4】

前記ベベルエッチング工程はプラズマエッチングを用いる、請求項1乃至3の何れか一項に記載のウェハ端面処理方法。

【請求項5】

半導体装置形成領域及び端面を有する半導体ウェハの前記半導体装置形成領域に、フォトリソグラフィ工程を用いて、半導体装置を製造する方法であって、

少なくとも1つのフォトリソグラフィ工程が、

前記半導体ウェハ上に反射防止膜を成膜する工程と、

前記端面において、前記反射防止膜の外周部をリンス処理により除去するリンス工程であり、前記反射防止膜の最外周部にハンプが形成されるリンス工程と、

前記反射防止膜上に設けられたレジストパターンを用いて、前記反射防止膜及びその下地構造をエッチングするエッチング工程と、

前記エッチング工程の前又は後に、前記端面において、前記半導体装置形成領域にマスクを設けることなく、前記ハンプが形成された位置をエッチングするベベルエッチング工程と、

を有する、半導体装置を製造する方法。

【請求項1】

半導体ウェハの端面において、該半導体ウェハ上に成膜された反射防止膜の外周部をリンス処理により除去するリンス工程であり、前記反射防止膜の最外周部にハンプが形成されるリンス工程と、

前記反射防止膜上に設けられたレジストパターンを用いて、前記反射防止膜及びその下地構造をエッチングするエッチング工程と、

前記エッチング工程の前又は後に、前記端面において、前記端面以外の前記半導体ウェハの領域にマスクを設けることなく、前記ハンプが形成された位置をエッチングするベベルエッチング工程と、

を有するウェハ端面処理方法。

【請求項2】

前記ベベルエッチング工程は前記エッチング工程の後に行われ、前記エッチング工程は前記ハンプが形成された位置で前記下地構造を構成する膜の一部を残存させ、前記ベベルエッチング工程は前記膜の一部を除去する、請求項1に記載のウェハ端面処理方法。

【請求項3】

前記ベベルエッチング工程は、前記エッチング工程の前に行われて前記ハンプを除去する、請求項1に記載のウェハ端面処理方法。

【請求項4】

前記ベベルエッチング工程はプラズマエッチングを用いる、請求項1乃至3の何れか一項に記載のウェハ端面処理方法。

【請求項5】

半導体装置形成領域及び端面を有する半導体ウェハの前記半導体装置形成領域に、フォトリソグラフィ工程を用いて、半導体装置を製造する方法であって、

少なくとも1つのフォトリソグラフィ工程が、

前記半導体ウェハ上に反射防止膜を成膜する工程と、

前記端面において、前記反射防止膜の外周部をリンス処理により除去するリンス工程であり、前記反射防止膜の最外周部にハンプが形成されるリンス工程と、

前記反射防止膜上に設けられたレジストパターンを用いて、前記反射防止膜及びその下地構造をエッチングするエッチング工程と、

前記エッチング工程の前又は後に、前記端面において、前記半導体装置形成領域にマスクを設けることなく、前記ハンプが形成された位置をエッチングするベベルエッチング工程と、

を有する、半導体装置を製造する方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−29562(P2011−29562A)

【公開日】平成23年2月10日(2011.2.10)

【国際特許分類】

【出願番号】特願2009−176570(P2009−176570)

【出願日】平成21年7月29日(2009.7.29)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成23年2月10日(2011.2.10)

【国際特許分類】

【出願日】平成21年7月29日(2009.7.29)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]