Fターム[5F046PA04]の内容

半導体の露光(電子、イオン線露光を除く) (57,085) | 光の吸収膜、反射膜 (454) | 吸収膜 (382) | 窒化膜 (13)

Fターム[5F046PA04]に分類される特許

1 - 13 / 13

半導体装置の製造方法

【課題】ロジック回路とメモリ回路を混載した半導体装置において、ロジック回路部に形成されるレジストパターン形状の精度低下抑制に寄与する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、ロジックトランジスタ、不揮発性メモリをそれぞれ形成する第1及び第2の活性領域を画定する素子分離絶縁膜を、STIで形成する工程と、第2の活性領域上方に、フローティングゲートとなる導電層を形成する工程と、導電層上及びその外側の領域を覆って、窒化シリコンを含む絶縁膜を形成する工程と、第1の活性領域の隣接部分の素子分離絶縁膜上の窒化シリコンを含む絶縁膜を覆い、第1の活性領域を露出するマスクを用いてエッチングする工程と、第1の活性領域の隣接部分の素子分離絶縁膜上の窒化シリコンを含む絶縁膜上に端部の配置されたフォトレジストパターンを形成する工程とを有する。

(もっと読む)

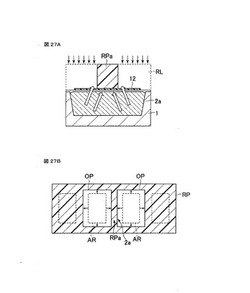

パターン形成方法

【課題】微細化したホール又はラインのパターンを、従来よりも容易に形成する製造方法を提供する。

【解決手段】被加工膜(2)上に第1のカーボン膜(3)と第1のARL(4)を順次堆積し、第1のARLをパターニングする工程、第2のカーボン膜(6)と第2のARL(7)を順次堆積し、第2のARLをパターニングする工程と、第2のARLをマスクとして第2のカーボン膜を除去する工程と、露出した第1のARLとをマスクとして、第1のカーボン膜を除去する工程と、残存している第1及び第2のカーボン膜をマスクとして被加工膜のエッチングを行う工程とを備えている。

(もっと読む)

アモルファスカーボンナイトライド膜の形成方法、アモルファスカーボンナイトライド膜、多層レジスト膜、半導体装置の製造方法および制御プログラムが記憶された記憶媒体

【課題】エッチング耐性に優れ、かつレジスト膜の露光時、反射率の低下が可能なアモルファスカーボン膜を形成する。

【解決手段】半導体装置の製造方法では、ウエハ上にエッチング対象膜を形成する工程、処理容器内にCOガス及びN2ガスを含む処理ガスを供給する工程、供給されたCOガス及びN2ガスからアモルファスカーボンナイトライド膜330を成膜する工程、膜330上に酸化シリコン膜335を形成する工程、膜335上にArFレジスト膜345を形成する工程、ArFレジスト膜345をパターニングする工程、ArFレジスト膜345をマスクとして酸化シリコン膜335をエッチングする工程、酸化シリコン膜335をマスクとしてアモルファスカーボンナイトライド膜330をエッチングする工程、アモルファスカーボンナイトライド膜330をマスクとしてエッチング対象膜をエッチングする工程を有する。

(もっと読む)

乾式または液浸リソグラフィを用いる45nmフィーチャサイズでの、フォトレジスト材料の崩壊およびポイゾニングの解消

90nm以下の範囲内のフィーチャサイズを有する半導体デバイスを製作するための方法および構造が提供される。本発明の一実施形態では、基板を処理する方法であって、基板の表面上に反射防止被覆層を堆積させること、反射防止被覆層上に接着促進層を堆積させること、および接着促進層上にレジスト材料を堆積させることを含む方法が提供される。本発明の別の実施形態では、誘電体基板と、誘電体層上に堆積された非晶質炭素層と、非晶質炭素層上に堆積された反射防止被覆層と、反射防止被覆層上に堆積された接着促進層と、接着促進層上に堆積されたレジスト材料とを含む、半導体基板構造が提供される。  (もっと読む)

(もっと読む)

微細パターンの形成方法、パターン保護材料と半導体装置

【課題】複数のパターンを合成して微細パターンを形成する方法において、プロセスを簡易化し、低コストで実施できる方法を提供する。

【解決手段】第1のパターンを形成する工程と、保護膜を形成する工程と、第2のパターンを保護膜上に形成する工程と、第2のパターンをマスクとして、保護膜と、保護膜により保護されたパターンをドライエッチングする工程と、保護膜を除去する工程とを備え、保護膜の形成工程から保護膜の除去工程までの工程を、単数回または複数回実施する。

(もっと読む)

半導体装置の微細パターン形成方法

【課題】パターンのCD変異を減らすことが可能な半導体素子の微細パターン形成方法を提供すること。

【解決手段】被エッチング層を有する半導体基板上に第1ポリシリコン膜28とバッファ酸化膜29を順次形成し、さらに第2ポリシリコン膜30、研磨停止膜31及び第1酸化膜32が積層された構造のハードマスクを形成する。ハードマスクの側面に窒化膜スペーサ35を形成し、全体に第2酸化膜36を形成する。第2酸化膜、窒化膜スペーサ及び第1酸化膜を研磨し、前記研磨停止膜と窒化膜スペーサを除去する。第2ポリシリコン膜と第2酸化膜をマスクとしてバッファ酸化膜をエッチングする。第2酸化膜を除去し、第2ポリシリコン膜とバッファ酸化膜をマスクとして第1ポリシリコン膜をエッチングし、第2ポリシリコン膜を除去する。バッファ酸化膜と前記第1ポリシリコン膜をマスクとして被エッチング層をエッチングする。

(もっと読む)

アンチレフレクティブコーティング及びその堆積の方法

【課題】 本発明は、アンチレフレクティブ層の堆積のための安定なプロセスを提供する。

【解決手段】 ヘリウムガスを用いてプラズマ励起シラン酸化物プロセス、プラズマ励起シランオキシナイトライドプロセス及びプラズマ励起シランナイトライドプロセスの堆積速度を下げる。また、ヘリウムはプロセスを安定化するためにも用いられ、別々の膜を堆積できるようにした。本発明はまた、プロセスパラメータを制御して、所望の光学挙動を得るための最適な屈折率、吸収率及び厚さを変化させたアンチレフレクティブ層を生成する。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】フォト工程のマージンを向上させること、パターン不良を防止すること、及びフォトマスクのアスペクト比を減らしてフォトマスク崩壊などの不良を防止することが可能なフラッシュメモリ素子の製造方法の提供。

【解決手段】所定の下部パターンが形成された半導体基板上に反射防止及びエッチング停止用膜を形成する段階と、前記反射防止及びエッチング停止用膜上に絶縁膜を形成する段階と、前記絶縁膜上にフォトレジストを形成する段階と、前記フォトレジストをパターニングする段階と、前記パターニングされたフォトレジストをマスクとして前記絶縁膜と前記反射防止及びエッチング停止用膜をエッチングしてトレンチを形成する段階とを含む、フラッシュメモリ素子の製造方法を提供する。

(もっと読む)

パターン形成方法および半導体装置の製造方法

【課題】 被エッチング膜の微細パターンを形成する工程において、半導体基板上に堆積された被エッチング膜をより微細に高精度でパターニングする。

【解決手段】 半導体基板上に被エッチング膜を堆積する工程と、被エッチング膜上にSiCwHxOyNz(w>0、x≧0、y>0、z≧0)で表される有機無機ハイブリッド膜を堆積する工程と、有機無機ハイブリッド膜のパターンを形成する工程と、有機無機ハイブリッド膜の表面部を酸化層に変換する工程と、酸化層を選択的に除去して、有機無機ハイブリッド膜パターンを所定寸法にする工程と、所定寸法にされた有機無機ハイブリッド膜パターンをマスクとして被エッチング膜をエッチングする工程とを含む。

(もっと読む)

パターン化されたイオン注入フォトレジストのウエハーから裏面反射防止膜を除去するのに有用な組成物

裏面反射防止膜(BARC)層をかかるBARC層を有する半導体基板から除去するための方法および組成物について記載する。除去組成物は、超臨界流体と、共溶媒と、エッチング液と、界面活性剤とを含む。かかる除去組成物は、SCCO2の除去剤としての固有の欠陥、すなわちSCCO2の非極性およびそれに関連する半導体基板から除去されなければならない無機塩および極性有機化合物などの種に対する可溶化能の欠如を克服する。

(もっと読む)

(もっと読む)

ハードマスク用塗布型窒化膜形成組成物

【課題】フォトレジスト層とのインターミキシングが起こらず、スピンコート法によって形成することができる、半導体装置製造のリソグラフィープロセスにおいてにハードマスクとして使用できる下層膜を提供すること。

【解決手段】平均粒子径が1〜1000nmである金属窒化物粒子及び有機溶剤を含むことを特徴とする、半導体装置の製造に使用される下層膜形成組成物。当該金属窒化物粒子は、チタン、シリコン、タンタル、タングステン、セリウム、ゲルマニウム、ハフニウム、及びガリウムからなる群から選ばれる少なくとも一種の元素を含む。

(もっと読む)

低温かつ低堆積レートでTEOSキャップ層を形成する方法

本発明は、限界寸法が50nm以下のポリシリコンラインフィーチャをパターニングするためのカーボンハードマスク層のために、二酸化シリコンのキャップ層を形成する方法を開示する。このために、低温のプラズマ支援型CVDプロセスが用いられ、このプロセスにおいては、堆積速度を低く維持して層厚の制御性と二酸化シリコン層の光学特徴とを向上させることができる。  (もっと読む)

(もっと読む)

スピンオンフォトパターン形成性中間層誘電性材料の使用及びそれを利用する中間半導体素子構造体

フォトパターン形成性塗布材料がこれまでに用いられなかった波長で半導体素子構造体の形成に用いられことを可能とするキャップ層。該フォトパターン形成性塗布材料を半導体基板へ層として塗布する。該キャップ層及びフォトレジスト層がそれぞれ該フォトパターン形成性層上に形成される。該キャップ層は放射線を吸収または反射し、そして該フォトパターン形成性層を該フォトレジスト層のパターン化に用いられた第1波長の放射線から保護する。該フォトパターン形成性塗布材料は第2波長の放射線に露光されると二酸化ケイ素系材料へ変換される。 (もっと読む)

1 - 13 / 13

[ Back to top ]