Fターム[5F047BC00]の内容

ダイボンディング (10,903) | 接合構造 (181)

Fターム[5F047BC00]の下位に属するFターム

バリア層 (49)

バインダー層、コンタクト層 (27)

保護層 (28)

絶縁層 (16)

緩衝材 (16)

ヒートシンク (11)

添加物(オーミック性) (1)

その他の層 (20)

Fターム[5F047BC00]に分類される特許

1 - 13 / 13

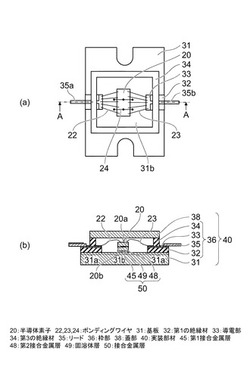

半導体装置、接合金属層付き半導体素子、実装部材、並びに半導体装置の製造方法

【課題】半導体素子と実装部材との接合温度以上でも動作可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、第1の金属を含む面を有する基板31と、外周領域31aに設けられた第1の絶縁材32および前記第1の絶縁材の上に設けられた導電部33を有する枠部36とを有する。半導体素子20は、前記導電部と電気的に接続可能である。接合金属層50は、第2の金属と、前記第2の金属内に分散された第3の金属と、前記第2の金属内に分散された第4の金属とを有する。また、接合金属層は、前記第2の金属の重量百分率が前記第3の金属の重量百分率よりも高く、かつ前記第3の金属の重量百分率が前記第4の金属の重量百分率よりも高い固溶体層により、前記半導体素子と前記内部領域とを接合可能である。

(もっと読む)

レーザ焼結下板を有する基板

【課題】結合構造の製造に応じて、構成要素を取り付ける後続の処理のための基板が提供される。

【解決手段】開示の基板は、金属部分と、この金属部分にレーザ焼結された下板とを備える。金属部分は、下板の焼結温度より低い融点を有する。結合構造20は、金属マトリックス複合材中のアルミニウム金属などの金属部分を有する構造部材22を含む。下板である金属層24が、構造部材22上に配置される。金属層24は、構造部材22と、構造部材22が結合材料28を介して結合される別の構成要素26との間に位置する。すなわち、金属層24は、結合材料28に関して下板になる。

(もっと読む)

半導体チップと半導体装置および半導体チップの製造方法

【課題】基板実装のリフロー時の接合不良を防止する半導体チップと半導体装置およびそれらの製造方法を提供することを目的とする。

【解決手段】半導体チップ1の裏面にシリコン粒子を付着させたシリコン粒子付着領域5bを形成することにより、半導体チップ裏面とダイボンド材との接合面に低密着界面の領域が形成され、リフローの際に生じる接合界面でのひずみが緩和されるため、製造時間の増加を抑制しながら基板実装のリフロー時の接合不良を防止することができる。

(もっと読む)

発光ダイオード装置および電子機器

【課題】放熱性に優れるため、長期にわたって安定的に高輝度の発光を行うことができる発光ダイオード装置、かかる発光ダイオード装置を備える信頼性に優れた電子機器を提供すること。

【解決手段】発光ダイオード装置1は、第1のリードフレーム21および第2のリードフレーム22と、第1のリードフレーム21に接合された基板3と、基板3の第1のリードフレーム21と反対側の面に設けられた発光部4と、基板3と第1のリードフレーム21とを接合する接合膜8とを有する。この発光ダイオード装置1が備える接合膜8は、金属原子と、金属原子と結合する酸素原子と、これらに結合する脱離基とを含み、接合膜8の少なくとも一部の領域にエネルギーを付与することにより、表面付近に存在する脱離基が脱離し、これにより接合膜8の表面に発現した接着性によって、第1のリードフレーム21と基板3とを接合している。

(もっと読む)

接合方法及び接合体

【課題】大面積の接合に有利で、且つ、製造コストの増加を抑制できる接合方法及び接合体を提供する。

【解決手段】第1部材における金属からなる第1接合部と、第2部材における金属からなる第2接合部との間に、金属ナノ粒子を有機溶媒中に分散してなる金属ペーストを介在させ、該金属ペーストを少なくとも加熱して金属ナノ粒子を焼結し、内部に空孔を有する接合部材として第1接合部と第2接合部を接合する接合方法であって、金属ペーストの構成条件及び金属ナノ粒子の焼結条件の少なくとも1つを調整することで、第1接合部と第2接合部との間に、空孔の占める割合である空孔率が互いに異なる複数種類の接合層を、隣接する接合層で空孔率が互いに異なるように積層形成して接合部材とする。

(もっと読む)

化合物半導体装置

【課題】電気的特性を維持しつつ接着強度が改善された化合物半導体装置を提供する。

【解決手段】化合物半導体からなる基板と、前記基板の裏面に設けられ、複数の開口部を有する裏面金電極と、を備え、前記複数の開口部はメッシュ状に設けられ、互いに最も近接している前記開口部を結ぶ直線は、前記基板の端面に形成されたへきかい面と非平行であることを特徴とする化合物半導体装置が提供される。

(もっと読む)

半導体装置、金属接合材料、半田付け方法及び電子機器の製造方法

【課題】回路基板上に半導体素子等の電子部品を誘導加熱で半田付けする際に好適な金属接合材料を提供する。

【解決手段】金属接合材料11は、半田付け温度で溶融可能な接合金属12と、半田付け温度で溶融不能かつ誘導加熱可能な位置決め金属13とが混合されて構成されている。接合金属12は、シート状又はテープ状(リボン状)に形成され、位置決め金属13は、複数の粒として形成されている。粒の形状は球体、立方体、多面体等、平面上に載置された際に載置状態に拘わらず高さがほぼ一定となる形状が好ましい。位置決め金属13には、強磁性材が使用され、Ni、Fe及びCoの少なくとも1つの金属が使用されている。接合金属12には、半田やろう材を使用することができ、半田は鉛半田及び鉛フリー半田のいずれであってもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】最終的な半導体装置としてのサイズの縮小化、及び薄型化が可能で、且つ、製造工程の容易化等を図る。

【解決手段】半導体装置は、平坦な被搭載面を有する回路チップ40と、この回路チップ40よりもサイズの小さな回路チップ20と、シート状の支持体22とを備えている。回路チップ20は、基板上に形成され、この基板に固定された平坦な裏面と、この裏面の反対側に位置する平坦な表面とを有している。支持体22は、回路チップ20の表面に貼着され、この回路チップ20を支持するものである。そして、支持体22により支持された回路チップ20の裏面を前記基板から剥離して前記被搭載面に圧接し、回路チップ20の裏面と前記被搭載面とを分子間結合力(例えば、水素結合)により固定している。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の寿命を向上させる。

【解決手段】接合界面3の密着強度を同一温度において基板1の0.2%耐力の大きさと同じ若しくはそれ以上にすることにより、半導体素子2と基板1間の変位を基板1側で受け止める。これにより、最終的な破壊現象は靱性が高く、ある一定の歪に対する繰り返し疲労強度が高い基板1側において発生するようになり、半導体装置の寿命を飛躍的に向上させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体チップ/絶縁基板間の半田接合について、その半田接合層に発生する熱劣化を抑制して長期信頼性の向上を図る。

【解決手段】絶縁基板2の 銅回路パターン2b上に半導体チップ3を半田マウントした半導体装置において、半導体チップ/銅回路パターン間の半田接合面域Aを半導体チップの中央部下に対応する中央面部Bと、該中央面部を取り囲む外周面部Cとに二分した上で、その中央面部にはSnをベースとする半田組成にSbを添加したSn−Sb系の鉛フリー半田8(第1の鉛フリー半田)を適用して接合し、外周面部にはSnをベースとする半田組成にAg,Cuなどを添加した鉛フリー半田9(第2の鉛フリー半田)を適用して接合するものとし、絶縁基板の銅回路パターン上に前記の鉛フリー半田を載せ、その上に半導体チップを重ね合わせた状態で、Sn−Sb系鉛フリー半田の融点以上の温度に加熱して中央,外周面部を同じ工程で同時に半田接合する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】複数の半導体チップを実装基板上に積層した半導体装置の個々のチップの接着性を向上させ、半導体装置の信頼性を向上させる。

【解決手段】実装基板1上の半導体チップ搭載領域に主として熱硬化性を有する樹脂よりなる接着材7を塗布し、半導体チップ3Aを搭載した後、熱処理することにより接着材7を硬化させ、常温まで自然冷却すると、実装基板1と半導体チップ3Aのα値の差により実装基板1等が凸型に反った形状となるが、この後、パッドP1とパッドPAとをワイヤボンディングし、その後、半導体チップ3A上に熱可塑性を有する樹脂よりなる接着材9Aを貼り付け、その上部にスペーサチップ5を熱圧着する。このように、熱圧着の際の熱で実装基板1や半導体チップ3Aがそれぞれほぼ平坦となり、半導体チップ3Aとスペーサチップ5の接着性が向上する。

(もっと読む)

半田付け方法

【課題】 電子部品の内部接合などに適用できるように、鉛フリーでかつ低コストにて高温半田付けを実現できる半田付け方法を提供する。

【解決手段】 Sn系またはZn系の半田材料3を用いてベース板1とダイオード2の電極4などの2部材を半田付けして接合する方法であって、少なくとも何れかの接合面にCoまたはCrまたはMoなどの金属被覆層8を形成して半田付け時にその金属が半田中に溶け込み、接合部の半田材料3の融点を上昇させて接合するようにした。

(もっと読む)

半導体装置およびその製造方法

【課題】 基材の上に、はんだ材料からなるはんだ層を介して半導体素子を接合してなる半導体装置において、はんだ層中のボイドの大きさを抑制することにより、半導体素子の冷却性能を適切に確保する。

【解決手段】 基材10の上に、はんだ材料からなるはんだ層20を介して半導体素子30が接合されてなる半導体装置100において、半導体素子30は駆動時に発熱することによって、その面内にて温度分布を持つものであり、半導体素子30において駆動時に許容される最大温度をTt、上記温度分布上において半導体素子30の位置xに対応した温度をTcとしたとき、この最大温度Ttから温度Tcを差し引いた値を温度マージンΔTとし、半導体素子30の面内にて温度マージンΔTが大きい位置xほど、はんだ層20中に存在するボイド40の最大直径dtが大きくなっている。

(もっと読む)

1 - 13 / 13

[ Back to top ]