Fターム[5F048BA04]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 多層基板(2層) (997) | 3層以上 (202) | 1エピ層と2エピ層が同型 (53)

Fターム[5F048BA04]に分類される特許

1 - 20 / 53

半導体装置及びその製造方法

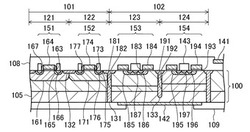

【課題】互いに絶縁分離された複数の素子を有する半導体装置の小型化と、その製造コストの低減とを実現できるようにする。

【解決手段】半導体装置は、第1の素子151、第2の素子152、第3の素子153及び第4の素子154を備えている。基板100は、基板を貫通する第1素子分離領域131により互いに分離された第1の区画101及び第2の区画102を有している。第1の区画は、第2素子分離領域132により互いに分離された第1素子領域121及び第2素子領域122を含む。第2の区画は、第3素子分離領域133により互いに分離された第3素子領域123及び第4素子領域124を含み、基板の裏面に露出した裏面拡散層を有している。第3の素子は、第3素子領域に形成され、第4の素子は、第4素子領域に形成され、第3の素子及び第4の素子は、裏面拡散層105を介在させて互いに接続されている。

(もっと読む)

半導体装置

【課題】不要な寄生素子の影響を排除できる低容量の過渡電圧保護素子を提供する。

【解決手段】半導体基板上に第1のエピタキシャル層210を形成し、第1のエピタキシャル層の表面近傍に埋め込み層220を形成し、埋め込み層上に第2のエピタキシャル層211を形成し、第2のエピタキシャル層内に第1のディープ拡散層250を形成し、第1のディープ拡散層内にツェナーダイオードを形成し、ツェナーダイオードから離れた位置に第1のPNダイオードを形成し、ツェナーダイオードは第1の分離層240により分離されており、第1のPNダイオードは第2の分離層241で分離されており、ツェナーダイオードと第1のPNダイオードが埋め込み層を経由して逆方向に直列接続されることにより、不要な寄生素子の影響を排除でき、かつ低容量の過渡電圧保護素子を実現する。

(もっと読む)

半導体装置の製造方法

【課題】Geをチャネル材料に用いても、素子特性の劣化を抑制することを可能にする。

【解決手段】Geを含むp型半導体領域上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、前記半導体領域の、前記ゲート電極の両側に位置する第1および第2領域に、有機金属錯体および酸化剤を交互に供給して金属酸化物を堆積する工程と、前記金属酸化物の上に金属膜を堆積する工程と、熱処理を行うことにより、前記半導体領域および前記金属酸化物と、前記金属膜とを反応させて前記第1および第2領域に金属半導体化合物層を形成するとともに前記金属半導体化合物層と前記半導体領域との界面に金属偏析層を形成する工程と、を備えている。

(もっと読む)

保護装置

【課題】 差動信号ラインに、第1入力端子と第2入力端子を有し、ダイオードにより構成される1パッケージの保護装置を接続する場合、第1入力端子と第2入力端子間のアイソレーションを十分確保し、また、第1入力端子に接続するダイオードと第2入力端子に接続するダイオードの部品ばらつきを抑制する必要がある。また、差動信号ラインに用いる保護装置の場合、部品容量とESD破壊耐量を所望の範囲に収めるようにする必要がある。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面にpn接合を形成し、互いに離間する第1n+型不純物領域、第2n+型不純物領域、第3n+型不純物領域を設け、第1入力端子に接続する第1n+型不純物領域と、第2入力端子に接続する第3n+型不純物領域との間に、接地端子に接続する第2n+型不純物領域を配置して、横型の双方向pn接合ダイオードによる保護装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】IGBT形成領域とその制御回路等形成領域とをPN接合分離法で分離し、且つIGBTからの漏れ電流が発生せず、制御回路等のCMOSトランジスタがラッチアップ等することのない高品質の半導体装置を実現する。

【解決手段】P型半導体基板1上に多層からなるN型エピタキシャル層3等を形成する。該N型エピタキシャル層3等をP+型分離層13等によりIGBT形成領域50と制御回路等形成領域40に分離する。該IGBT形成領域50の最下層の前記N型エピタキシャル層3と前記P型半導体基板1の双方に延在するN+型埋め込みガード層2を形成する。また該N+型埋め込みガード層2の端部と接続し前記エピタキシャル層3等の表面まで延在するN+型ガードリング9等を形成する。前記N+型埋め込みガード層2と該N+型ガードリング9等に囲まれた前記エピタキシャル層3等にIGBTを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を提供する。

【解決手段】半導体基板SUBの表面に、ソース領域SOおよびドレイン領域DRを有する高耐圧横型MOSトランジスタが完成される。そのトランジスタを平面視において取り囲む溝DTRが半導体基板SUBの表面に形成される。そのトランジスタ上を覆うように、かつ溝DTR内に中空SPを形成するようにトランジスタ上および溝DTR内に絶縁膜IIAが形成される。層間絶縁膜IIにトランジスタのソース領域SOおよびドレイン領域DRの各々に達するコンタクトホールCHが形成される。

(もっと読む)

半導体装置の製造方法

【課題】 一般的なエピタキシャルウエーハを用いて、部分SOI基板を用いた場合と同様、更にはより広範な種類のパワー素子等の縦型素子構造を組み込んだ半導体素子を安価に製造することのできる半導体装置の製造方法を提供する。

【解決手段】 P型シリコン単結晶基板に、N型エピタキシャル層と半導体エピタキシャル層を形成する工程と、半導体エピタキシャル層に半導体素子とトレンチを形成する工程と、半導体素子が形成された側の表面に保持基板を貼り合わせる工程と、N型エピタキシャル層に正電圧を印加して、N型エピタキシャル層をエッチストップ層として電気化学的エッチングによりP型シリコン単結晶基板を除去する工程と、露出した表面に絶縁膜を形成する工程と、絶縁膜のうち、縦型素子とする半導体素子が形成された領域に対応する位置の絶縁膜を除去する窓明けを行う工程と、窓明け部に、裏面電極を形成する工程を有する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】統合型のインテリジェントスイッチデバイス、統合型の入力信号・伝達ICまたは統合型のパワーICなどに用いられる横型MOSFETにおいて、複雑な分離構造を用いずに、より小さいチップ面積で高ESD耐量および高サージ耐量を具えた半導体装置を提供する。

【解決手段】P型半導体よりなるエミッタ領域25、ベース領域として機能するNウェル領域10およびP型エピタキシャル成長層13およびP型半導体基板12をコレクタとするベースオープンの縦型バイポーラトランジスタの表面電極26と、横型MOSFETのドレイン電極22とを金属電極配線27により電気的に接続し、高ESD電圧や高サージ電圧が印加されたときに、ベースオープンの縦型バイポーラトランジスタの動作によりESDおよびサージエネルギーを吸収するとともに、破壊に至る横型MOSFETの降伏耐圧以下の電圧に制限する。

(もっと読む)

半導体装置及び電力変換装置

【課題】静電容量と抵抗の値が異なる複数のスナバ回路を用意する必要がなく、且つ逆バイアス時に還流ダイオードに発生する振動現象の収束時間を短縮できる半導体装置及び電力変換装置を提供する。

【解決手段】アノード端子300とカソード端子400からなる一対の接続端子と、一対の接続端子間に接続されたユニポーラ動作する還流ダイオード100と、一対の接続端子間に還流ダイオード100と並列接続され、少なくともキャパシタ210と抵抗220を含む半導体スナバ回路200と備え、半導体スナバ回路200のキャパシタ210と抵抗220の値が可変である。

(もっと読む)

半導体装置

【課題】ソース・ドレイン領域のエクステンション領域の不純物濃度プロファイルが急峻なp型トランジスタを有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置1aは、半導体基板2上に形成された結晶層13と、結晶層13上にゲート絶縁膜14を介して形成されたゲート電極15と、半導体基板2と結晶層13との間に形成された、ゲート電極15の下方の領域において第1の不純物を含むC含有Si系結晶からなる不純物拡散抑制層12と、半導体基板2、不純物拡散抑制層12、および結晶層13内のゲート電極15の両側に形成され、結晶層13内にエクステンション領域を有する、p導電型を有する第2の不純物を含むp型ソース・ドレイン領域17と、を有し、C含有Si系結晶は第2の不純物の拡散を抑制する機能を有し、第1の不純物は、C含有Si系結晶内の固定電荷の発生を抑制する機能を有する。

(もっと読む)

所望のドーパント濃度を実現するためのイオン注入法

【課題】本発明は、MOSFETのそれぞれが一義的に決る閾値電圧をもつ複数のMOSFETの形成方法を提供する。

【解決手段】各MOSFETのために、ドープされた井戸又はタブが形成される。次に、各半導体井戸に近接して、材料ラインを形成するために、パターン形成されたマスクが用いられる。この場合、ラインの幅はMOSFETに所望の閾値電圧に依存する。イオンビームが材料ラインを通過するように、基板表面に対し鋭い角度で、傾斜イオン注入が行われる。より厚いラインはイオンビームに対し、より低い透過係数をもち、従って隣接した半導体井戸に到達するイオンビームの強度は低下する。ライン幅を適当に選択することにより、タブ中のドーパント濃度、従って最終的なMOSFET閾値電圧は制御できる。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチゲート型VDMOSFETのオン抵抗Ronを増大させることなく、プレーナゲート型MOSFETのソース領域およびドレイン領域と半導体基板との間の分離耐圧を向上させることができる、半導体装置およびその製造方法を提供するこ。

【解決手段】PMOS領域17において、ディープウェル領域16の表層部には、N型ウェル領域20が形成されている。ディープウェル領域16の下方には、ディープウェル領域16に接して、P型の埋込層36が形成されている。これにより、N型ウェル領域20の下方において、P型を有する領域の厚さが増す。その結果、N型ウェル領域20とN型の半導体基板5との間の分離耐圧を向上させることができる。

(もっと読む)

電気回路のスイッチング装置

【課題】逆方向電流を阻止する機能を有するIGFETの逆方向耐圧の向上が要求されている。

【解決手段】スイッチング装置(10)は、逆方向電流を阻止するショットキダイオードD3を内蔵する主IGFET(11)と、保護スイッチ手段(12)と、保護スイッチ制御手段(13)とを有する。保護スイッチ手段(12)は主IGFET(11)のドレイン電極Dとゲート電極Gとの間に接続されている。保護スイッチ制御手段(13)は、主IGFET(11)に逆方向電圧が印加された時に保護スイッチ手段(12)をオンにする。これにより、主IGFET(11)が逆方向電圧から保護される。

(もっと読む)

半導体装置

【課題】高耐圧と速い動作とを共に実現することが可能な半導体装置を提供する。

【解決手段】N型基板1上に形成されたN型の半導体層2と、この半導体層2の表面に形成されたP型の第1拡散層4と、半導体層2の表面に、第1拡散層4と互いに離間し、かつ、第1拡散層4を囲むように形成された、P型の第2拡散層4と、第1拡散層4の表面に形成された、P型の第3拡散層5と、第2拡散層4の表面に形成された、P型の第4拡散層7と、第1拡散層4の表面に形成され、第3拡散層5と電気的に接続された、N型の第5拡散層6と、第2拡散層4の表面と半導体層2の表面とをまたぐように形成され、第4拡散層7と電気的に接続された、N型の第6拡散層8とを含む、PN接合型ダイオードを有する半導体装置を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 従来、半導体層内に高濃度不純物領域を埋め込む構造において、耐圧確保のためにその周囲に低濃度不純物領域を配置していたが、所望の耐圧を確保するために長時間で高温の熱処理工程が必要であった。

【解決手段】 埋め込み高濃度不純物領域の周囲に低濃度半導体層が配置される構造を採用する。半導体層の厚みで耐圧を確保する低濃度不純物領域の幅を調整できるので、従来の不純物の拡散による低濃度不純物領域を省くことができる。高温長時間の熱処理工程が不要となり、製造工程にかかる時間を短縮できる。また低濃度半導体層に追加して不純物拡散による埋め込み低濃度不純物領域を設けてもよく、この場合は従来より熱処理温度を短縮し、高い耐圧を得ることができる。

(もっと読む)

半導体装置

【課題】MOSFETを安定して動作させるとともに、SBD領域における耐圧の低下を防ぐことのできる半導体装置を提供する。

【解決手段】半導体装置は、MOSFET領域10とSBD領域20とが配置されているn+型半導体基板1と、n+型半導体基板1上に設けられたn型エピタキシャル層2とを備える。MOSFET領域10は、p型ベース領域3に設けられ第1の不純物濃度を有するp+型拡散領域5を備える。SBD領域20は、n型エピタキシャル層2の上面に設けられ第2の不純物濃度を有するp型拡散領域21を備える。p型拡散領域21の有する第2の不純物濃度は、p+型拡散領域5の有する第1の不純物濃度よりも低い。

(もっと読む)

MOS型半導体装置

【目的】デバイスサイズを小型化し、通電能力を大きくしたゲート保護用のツェナーダイオードを有するMOS半導体装置を提供する。

【解決手段】ゲート電極5をツェナーダイオードとなるn+ポリシリコン7とp+ポリシリコン8で形成し、厚い絶縁膜6上にp+ポリシリコン8を形成し、このp+ポリシリコン8をソース電極13と接続することで、ツェナーダイオードをゲート端子Gとソース端子Sの間に挿入することができる。このツェナーダイオードは活性領域に形成されるため、ちチップサイズを小型化しつつ、通電能力を大きくできる。

(もっと読む)

半導体装置

【課題】1チップサイズが小さく、しかも安価に具現できる高性能な半導体装置を提供すること。

【解決手段】この半導体装置は、一半導体基板構造(エピタキシャル層11を有するP型半導体基板10)上で過電圧に対するゲート電極保護のためのツェナダイオード(保護素子)2が一つの素子領域E2においてDMOSトランジスタ1に接続されて構成された素子一体化構造となっている。ツェナダイオード2は、DMOSトランジスタ1のドレイン電極領域内のDMOSトランジスタ1とは異なる濃度(或いは同濃度であっても良い)で分離された拡散領域(ツェナダイオード2形成用のP型拡散領域)上に形成されて成る。又、この半導体装置の場合、一つの素子領域E2の両側にだけ素子分離領域E1を設ければ良いので、素子領域E2及び素子分離領域E1の両方が可能な限り少ない個数で占有面積の小さな構造を持つ。

(もっと読む)

半導体装置

【課題】静電放電等の電気的過渡現象に対する耐性に優れた半導体装置を提供する。

【解決手段】第1導電型の第1の活性層と、第2導電型の第2の活性層と、第1の活性層の上に設けられ第2の活性層に接する第2導電型のベース層と、ベース層の表層部に設けられた第2導電型のベースコンタクト領域と、ベース層の表層部に設けられた第1導電型のソース領域と、ソース領域に対して離間して第2の活性層の表層部に設けられた第1導電型のドレイン領域と、ドレイン領域に接して第2の活性層の表層部に設けられた第1導電型のドリフト領域と、第2の活性層におけるソース領域とドリフト領域との間の表面に対向して設けられたゲート電極と、ソース領域とドリフト領域との間に設けられ電子の移動に対して障壁となる障壁層と、ドレイン領域に接続されたドレイン電極と、ソース領域及びベースコンタクト領域と接続されたソース電極とを備えている。

(もっと読む)

半導体装置

【課題】チャネル領域における高いキャリア移動度を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成され、内部におけるキャリアの移動度がSi結晶よりも大きい第1の結晶からなる半導体層と、前記半導体層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層を挟んで形成され、前記半導体層に前記半導体層内のキャリアの移動度が上昇する方向に歪みを与える第2の結晶を含み、前記半導体層に接する深さの浅い領域であるソース・ドレインエクステンション領域を有するソース・ドレイン領域と、を有する。

(もっと読む)

1 - 20 / 53

[ Back to top ]