Fターム[5F048BA13]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 埋め込み層 (425) | 二重埋め込み層 (45)

Fターム[5F048BA13]に分類される特許

1 - 20 / 45

半導体装置の製造方法

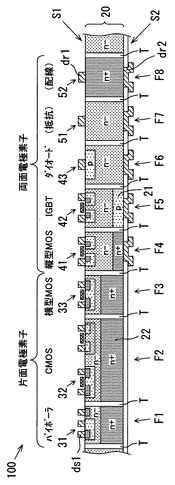

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能向上を図る。

【解決手段】ゲート電極GE1,GE2,GE3,GE4の側壁上にオフセットスペーサを形成した状態で半導体基板1のnMIS領域1A,1BおよびpMIS領域1C,1Dのそれぞれにイオン注入を行うことで、ソース・ドレインのエクステンション領域を形成する。この際、nMIS領域1A,1BおよびpMIS領域1C,1Dのそれぞれに対して別々のフォトレジストパターンを用いて個別にイオン注入を行うが、フォトレジストパターンを形成し直す度に、オフセットスペーサを形成し直すようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】異なる不純物濃度の埋め込み層を有する半導体装置を短時間かつ低コストで製造する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の表面に第1の酸化膜11を形成する第1の酸化膜形成ステップと、フォトダイオードが形成される第1の領域に形成された前記酸化膜の一部を除去して第1の間隔で第1の開口部を形成すると共に、トランジスタが形成される第2の領域に形成された前記酸化膜を除去して前記半導体基板の表面を露出させる第1の開口部12を形成ステップと、前記第1の酸化膜をマスクとして利用して前記第1の開口部及び前記第2の領域に対して第1の不純物を注入する第1の不純物注入ステップと、前記第1の不純物を熱拡散させる第1の熱拡散ステップと、を有する。

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置

【課題】半導体基板に向かって流れ込む回生電流又は寄生バイポーラトランジスタのオン電流を、チップサイズを増大させることなく低減できるLDMOSトランジスタの実現が課題となる。

【解決手段】N+型ドレイン層13等が形成されたN型エピタキシャル層5からなるN型層5aを、N型エピタキシャル層5の表面からN+型埋め込み層2まで延在するP型ドレイン分離層6で取り囲む。P型ドレイン分離層6とP型素子分離層3に囲まれたN型エピタキシャル層5からなるN型層5bにその表面から内部に延在するP型コレクタ層7を形成する。これにより第1導電型のドレイン分離層6をエミッタ、前記第2導電型の分離層5bをベース、前記コレクタ層7をコレクタとする寄生バイポーラトランジスタを形成しサージ電流を接地ラインに流す。

(もっと読む)

トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

【課題】表面上に素子をより高密度に実装する。

【解決手段】第1のトレンチと第2のトレンチとの間の位置において、エピタキシャル層の表面から基板へと下方に延在するドーパントのウェルは、エピタキシャル層の背景ドーピング濃度とは異なるドーピング濃度を有し、エピタキシャル層の残りの部分と第1および第2の接合を形成する。第1の接合は、第1のトレンチの底部から基板に延在し、第2の接合は、第2のトレンチの底部から前記基板に延在する。ウェルおよび第1および第2のトレンチは分離構造を構成し、分離構造は、分離構造の一方側のエピタキシャル層に形成された第1の素子と分離構造の他方側のエピタキシャル層に形成された第2の素子とを電気的に分離する。分離構造による電気的分離は第1および第2のトレンチとPN接合とによってもたらされ、ウェルは第1の導電型の材料でドープされ、基板およびエピタキシャル層は、第1の導電型とは反対の第2の導電型の材料でドープされ、第1および第2の接合はPN接合である。

(もっと読む)

モノリシック集積複合III−V族及びIV族半導体デバイス、並びにその製造方法

【課題】単一のダイの上にIII−V族半導体デバイスをIV族半導体デバイスと共に集積する、複合デバイスの製造方法を提供する。

【解決手段】IV族半導体基板202上にIII−V族半導体本体274a,274bを形成するステップと、III−V族半導体本体にトレンチを形成し、トレンチ内にIV族半導体本体232を形成するステップとを有する。この方法は、IV族半導体本体内に少なくとも1つのIV族半導体デバイス272を製造するステップと、III−V族半導体本体内に少なくとも1つのIII−V族半導体デバイス274を製造するステップも含む。III−V族半導体本体の上面とIV族半導体本体の上面とを平坦化して、それぞれの上面をほぼ同一平面にするステップをさらに含む。一実施形態では、トレンチの側壁に隣接する、前記IV族半導体本体の欠陥領域に、少なくとも1つの受動デバイスを製造するステップをさらに含む。

(もっと読む)

半導体装置

【課題】半導体装置の高耐圧化を図る。

【解決手段】p-基板200の主面上にはドレイン電極119及びVB電極128が形成されている。p-基板200の主面内には、ドレイン電極119に接続されたn型不純物領域117と、n型不純物領域117とは離間するとともにVB電極128に接続された、n型不純物領域117の側面に対向する側面を有するn型不純物領域121とが形成されている。p-基板200の主面内には、n型不純物領域121の底面に接し、n型不純物領域117の側面に接しない側面を有するn埋め込み層29が形成されている。

(もっと読む)

半導体装置

【課題】半導体装置の高耐圧化を図る。

【解決手段】n型不純物領域121の主面内にはpウェル131が形成されている。nMOSFETが有する、COM端子に接続されたn+型ソース領域133は、pウェル131の主面内に形成されている。pMOSFETが有する、VCC端子に接続されたp+型ソース領域126は、n型不純物領域121の主面内に形成されている。n埋め込み層24はn型不純物領域121の底面に接している。

(もっと読む)

半導体装置

【課題】半導体装置の高耐圧化を図る。

【解決手段】p-基板200の主面内にはn型不純物領域121が形成されている。n型不純物領域121の主面内にはpウェル131が形成されている。nMOSFETが有する、VS端子に接続されたn+型ソース領域133は、pウェル131の主面内に形成されている。pMOSFETが有する、VB端子に接続されたp+型ソース領域126は、n型不純物領域121の主面内に形成されている。n+埋め込み層31は、少なくともn+型ソース領域133の下方を覆いつつ、n型不純物領域121の底面に接してp-基板200内に形成されている。n+埋め込み層31は、n型不純物領域121が有する第1の不純物濃度よりも高い第2の不純物濃度を有する。

(もっと読む)

半導体装置

【課題】隣接する保護装置を備える半導体装置において、クロストークノイズの低減を実現する。

【解決手段】本発明に係る半導体装置に備えられた隣接位置に配置される保護装置50A,50Bは、第1導電型半導体基板1と、第1導電型ウェル12と、保護対象の回路の端子に接続された第2導電型の第1の領域22、21cと、第1の電圧が印加される、第2導電型の第2の領域21b、21dと、第1導電型ウェル12を囲むように形成された第2導電型ガードリングウェル23と、ガードリングウェル23の深層部に接触し、第1の領域22、21cに接触せずに隣接して形成された第2導電型深層領域24と、第1導電型ウェル12よりも不純物濃度が高く、第2導電型深層領域24より下層に配置され、第1の領域22の下層から、少なくともその近傍領域の第2導電型深層領域24までに亘って形成された第1導電型深層領域14とを備える。

(もっと読む)

半導体装置

【課題】半導体装置の高耐圧化を図る。

【解決手段】p-基板200の主面上にはアノード電極145及びカソード電極142が形成されている。p-基板200の主面内には、アノード電極145に接続されたpウェル144bと、カソード電極142に接続されたn型不純物領域121と、pウェル144bの側面とn型不純物領域121の側面とによって挟まれた部分を有するn-型不純物領域143とが形成されている。p-基板200の主面内には、n型不純物領域121の側面よりもpウェル144b側に突出しないように、n型不純物領域121の底面に接するn埋め込み層26が形成されている。

(もっと読む)

半導体装置

【課題】ハイサイド素子として用いても誤動作が少なく、かつ耐圧を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が形成されている。p-エピタキシャル領域EP1の主表面側には、p-エピタキシャル領域EP2が形成されている。p-エピタキシャル領域EP2の主表面側には、n型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにフローティング電位のn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。

(もっと読む)

半導体デバイス、半導体基板に分離されたポケットを形成する方法、半導体構成、PNPトランジスタ、横型NチャネルDMOSトランジスタ、横型トレンチDMOSトランジスタ

【課題】モジュール化された、相互作用しないやり方で、単一の半導体ウェハにともに接近して実装され、十分に分離された、最適化されたトランジスタまたは他のデバイスの任意の集合の作製を可能にする。

【解決手段】

一群の半導体デバイスが、エピタキシャル層を含まない基板に形成される。一実施例では、この一群は、5VのCMOSペア、12VのCMOSペア、5VのNPN、5VのPNP、いくつかの形状の横型トレンチMOSFET、および30V横型N−チャネルDMOSを含む。これらのデバイスの各々は、横方向かつ縦方向の双方において極めて小型であり、基板の他のすべてのデバイスから十分に分離され得る。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタの高速化に伴うMOSトランジスタの分離特性の低下を抑制する半導体装置を提供する。

【解決手段】半導体装置1000aは、第一導電型のバイポーラトランジスタ100及びMOSトランジスタ200を備え、MOSトランジスタ200は、第二導電型の半導体基板1と半導体基板1上に形成された第一導電型のエピタキシャル層2との界面付近に形成された、半導体基板1上面から第一の深さに不純物濃度のピークを持つ第一導電型埋込層16と、第一導電型埋込層16上に形成された第二導電型埋込層17及びウェル層18と、第二導電型ウェル層18に形成された第一導電型のソース層19及びドレイン層20と、第一の深さより浅い第二の深さに不純物濃度のピークを持つ第一導電型埋込層27とを有し、第一導電型埋込層27は、第一導電型埋込層16と接し、かつ、第二導電型埋込層17の外縁部を囲むように形成されている。

(もっと読む)

半導体装置

【課題】対基板耐圧が向上しチップシュリンクも実現可能な、DTI構造を有する半導体装置を提供する。

【解決手段】例えばP型の基板1と、この基板1上に形成されたN型のEPI層2と、基板1とEPI層2とにわたって形成されたN型の第1の埋め込み層(埋め込み層3)と、この第1の埋め込み層の下に形成され埋め込み層3よりも不純物濃度の低いN型の第2の埋め込み層(埋め込み層12)と、EPI層2の表面から埋め込み層12、埋め込み層3を貫通して基板1内に達するDTI4と、を備えた半導体装置。

(もっと読む)

BiCDMOS構造及びその製造方法

【課題】DMOS電力回路、CMOSデジタル論理回路、及びコンプリメンタリバイポーラアナログ回路の全てを単一の集積化された回路チップ上に実現するBiCDMOS構造及びその製造方法を提供する。

【解決手段】基層10内に下向きに延出し、且つ基層の上に配置されたエピタキシャル層40内に上向きに延出し、かつエピタキシャル層の上側主面の下に配置された埋め込み絶縁領域21Bと、エピタキシャル層内のみに配置され、かつ埋め込み絶縁領域の上側主面から上向きに延出した埋め込みウェル領域44Bと、エピタキシャル層内に配置され、かつエピタキシャル層の上側主面からエピタキシャル層内に下向きに延出し、かつ埋め込みウェル領域の上側主面に接触する下側主面を備えたウェル領域51Bとを有し、バイポーラトランジスタがウェル領域内に形成され、MOSトランジスタがウェル領域外のエピタキシャル層の上側主面に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧で、基板への電流の漏れが抑制され、かつ、端子に負入力があった場合でも基板から端子への電流の抜けが抑制されたダイオードを基板上に有する半導体装置およびその製造方法を提供すること。

【解決手段】P型基板1と、P型基板1上に順次形成されたN型埋め込み層2、P型埋め込み層3、およびN型エピタキシャル層4と、P型埋め込み層3上に形成されN型エピタキシャル層4を囲むP型拡散層6と、ゲート領域を構成するP型拡散層8およびP型拡散層11と、ソース領域を構成するN型拡散層9、P型拡散層12およびN型拡散層13と、N型エピタキシャル層4の上方に形成されP型拡散層12およびN型拡散層13と短絡したゲート電極と、を備え、N型埋め込み層2はフローティング状態にある。

(もっと読む)

1 - 20 / 45

[ Back to top ]