Fターム[5F048BB09]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 金属、合金、金属化合物(シリサイドを除く) (1,529)

Fターム[5F048BB09]に分類される特許

1,521 - 1,529 / 1,529

大量にドープされたエピタキシャルSiGeを選択的に堆積させる方法

一実施形態においては、基板上にシリコン膜又はシリコンゲルマニウム膜を堆積させる方法であって、プロセスチャンバ内に基板を配置するステップと、基板表面を約600℃〜900℃の範囲の温度に、プロセスチャンバ内の圧力を約13Pa(0.1トール)〜約27kPa(200トール)の範囲に維持しつつ、加熱するステップと、を含む前記が提供される。堆積ガスは、プロセスチャンバに供給され、SiH4、任意のゲルマニウム源ガス、エッチング剤、キャリヤガス、任意に少なくとも1つのドーパントガスを含んでいる。シリコン膜又はシリコンゲルマニウム膜は、基板上に選択的且つエピタキシャル的に成長する。一実施形態は、シリコン含有膜とキャリヤガスとして不活性ガスを堆積させる方法を含んでいる。方法は、また、選択的シリコンゲルマニウムエピタキシャル膜を用いる電子デバイスの製造を含んでいる。 (もっと読む)

格子不整合エピタキシャル拡張領域ならびにソースおよびドレイン領域を有するひずみチャネルCMOSトランジスタ構造体およびその製造方法

【課題】n型電界効果トランジスタ(NFET)およびp型電界効果トランジスタ(PFET)がそれぞれ、第1の半導体の単結晶層内に配置されたチャネル領域を有し、PFETのチャネル領域には第1の大きさの応力が加えられているが、NFETのチャネル領域にはその大きさの応力が加えられていない構造体およびその製造方法を提供すること。

【解決手段】この応力は、第1の半導体とは格子不整合の第2の半導体の層によって加えられる。この第2の半導体の層は、PFETのソースおよびドレイン領域ならびに拡張領域の上の、PFETのチャネル領域から第1の距離のところに形成されており、この第2の半導体の層は、NFETのソースおよびドレイン領域の上の、NFETのチャネル領域からより大きな第2の距離のところにも形成されており、またはNFETには全く形成されていない。

(もっと読む)

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

フィン型電界効果トランジスタを有する半導体装置

n型電界効果トランジスタおよびp型電界効果トランジスタとを含む半導体装置であって、n型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{100}面であり、p型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{110}面である、という条件を満足する半導体装置とする。 (もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

バンド設計超格子を有する半導体装置を製作する方法

複数の積層された層群を有する超格子を形成するステップによって、半導体装置を製作する方法である。また当該方法は、前記超格子を通って、前記積層された層群と平行な方向に、電荷キャリアの輸送が生じる領域を形成するステップを有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。前記エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取りこまれた、少なくとも一つの非半導体分子層を有し、前記超格子は、超格子が存在しない場合に比べて、前記平行な方向において大きな電荷キャリア移動度を有する。また前記超格子は、共通のエネルギーバンド構造を有しても良い。

(もっと読む)

(もっと読む)

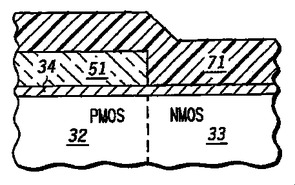

デュアルメタルゲートデバイスの形成方法

異種金属により形成されるデュアルメタルゲートを備えるMOSトランジスタ(10)を形成する方法を提供する。HfO2のようなゲート誘電体(34)を半導体基板(31)の上に堆積させる。次に、犠牲層(35)をゲート誘電体(34)を覆うように堆積させる。犠牲層(35)をパターニングして、基板(31)の第1領域(32)(例えばpMOS)の上のゲート誘電体(34)が露出し、かつ基板(31)の第2領域(33)(例えばnMOS)の上のゲート誘電体(34)が犠牲層(35)によって保護されたままになるようにする。第1ゲート導体材料(51)を残りの犠牲領域(35)の上に、かつ露出したゲート誘電体(34)の上に堆積させる。基板(31)の第2領域(33)の上の第1ゲート導体材料(51)がエッチングにより全て除去されるように第1ゲート導体材料(51)をパターニングする。第1ゲート導体材料(51)を取り除く際に、第2領域(33)上の犠牲層(35)は、下層の誘電体材料(34)にダメージが加わるのを防止するように機能することができる。  (もっと読む)

(もっと読む)

半導体装置および電子機器

【課題】 本発明では剥離技術を用いることにより様々な基板上に薄膜素子を形成し、従来の技術では不可能であると考えられていた部分に薄膜素子を形成することにより、省スペース化を図ると共に耐衝撃性やフレキシビリティに優れた半導体装置を提供する。

【解決手段】 本発明では、剥離技術を用いて一旦基板から剥離させた膜厚50μm以下の素子形成層を基板上に固着することにより、様々な基板上に薄膜素子を形成することを特徴とする。例えば、可撓性基板上に固着された薄膜素子をパネルの裏面に貼り付けたり、直接パネルの裏面に固着したり、さらには、パネルに貼り付けられたFPC上に薄膜素子を固着することにより、省スペース化を図ることができる。

(もっと読む)

D/A変換回路及び半導体装置

【課題】 高いビット数のデジタル信号に対応し、線形性が良く、占有面積の小さいD/A変換回路を提供する。

【解決手段】 複数の容量を有するD/A変換回路であって、複数の容量は、第1電極と、第1電極に接している第1誘電体と、第1誘電体に接している第2電極と、第2電極に接している第2誘電体と、第2誘電体に接している第3電極とをそれぞれ有しており、第2電極は、第1電極及び第3電極と重なっており、第2電極は、第1電極及び第3電極と重なっている部分において開口部を有しており、第2電極が有する開口部において、第1誘電体及び第2誘電体にコンタクトホールが形成されており、コンタクトホールを介して第1電極と第3電極が接続されていることを特徴とするD/A変換回路。

(もっと読む)

1,521 - 1,529 / 1,529

[ Back to top ]