Fターム[5F048BC07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 追加領域の形成 (3,324) | 二重拡散 (380)

Fターム[5F048BC07]に分類される特許

1 - 20 / 380

半導体装置の製造方法及び半導体装置

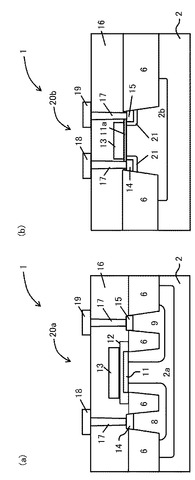

半導体装置およびその製造方法

【課題】低耐圧トランジスタ特性への影響なく、耐圧特性および動作特性が安定した高耐圧素子を組み込む。

【解決手段】同一の半導体基板2上に、トレンチ分離絶縁膜(プラズマ酸化膜6)によって素子分離された高耐圧素子20aと低耐圧素子20bを設けた半導体装置1において、高耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さが低耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さよりも低く形成されている。高耐圧素子形成領域におけるトレンチ分離絶縁膜(プラズマ酸化膜6)の表面高さが、高耐圧素子20aのチャネルを形成する半導体基板2の表面に対して−10〜60nm(より好ましくは−10〜30nm)だけ高くなるように形成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】高耐圧MOSトランジスタと低電圧MOSトランジスタとの両方について良好な特性を得るための技術を提供する。

【解決手段】高耐圧領域に高耐圧トランジスタが形成され、低耐圧領域に低耐圧トランジスタが形成される半導体装置の製造方法が提供される。当該半導体装置の製造方法は、シリコン基板1の表面に、熱酸化膜2とシリコン窒化膜3を形成する工程と、高耐圧領域、低耐圧領域のそれぞれにおいて熱酸化膜2とシリコン窒化膜3に開口を形成する工程と、該開口を通じてシリコン基板1をエッチングしてトレンチ11、12を形成する工程と、トレンチ11、12に埋め込み酸化膜14を埋め込む工程と、熱酸化膜2とシリコン窒化膜3を除去する工程と、厚いゲート酸化膜15と薄いゲート酸化膜16とを形成する工程とを備えている。トレンチ12のテーパー部分8aの深さが、トレンチ11のテーパー部分5aの深さよりも浅い。

(もっと読む)

半導体装置

【課題】 ゲート長方向に対し水平に複数本のトレンチを形成することにより単位面積当たりのゲート幅を増大させる高駆動能力横型MOSにおいて、素子面積を増加させずに更に駆動能力を向上させる。

【解決手段】 半導体基板表面から一定の深さに設けられた高抵抗第一導電型半導体のウェル領域と、前記ウェル領域の表面から途中の深さまで達する複数本のトレンチと、前記トレンチが形成する凹凸部の表面に設けられたゲート絶縁膜と、前記トレンチ内部に埋め込まれたゲート電極と前記トレンチ両端付近を除く前記凹凸部領域において前記トレンチ内部に埋め込まれたゲート電極と接触して基板表面に設けられたゲート電極膜と、前記ゲート電極膜と接触して前記トレンチ両端付近のトレンチ内部に半導体基板表面より深い位置に表面が位置するように埋め込まれたゲート電極膜と、前記ゲート電極膜と接触していない半導体面から前記ウェル領域の深さより浅く設けられた2つの低抵抗第二導電型半導体層であるソース領域とドレイン領域を有する半導体装置とした。

(もっと読む)

横型半導体装置及びその製造方法

【課題】既存のCMOS製造工程に対して工程の追加や変更を行うことなく、素子に要求される耐圧に応じて横型半導体装置が有するLocos酸化膜を最適に制御することができる、横型半導体装置の製造方法を提供する。

【解決手段】半導体基板(100、101)上のLocos形成領域に、遮蔽部及び開口部が所定の幅及び間隔で設けられたパターン(113a、113b)を有するマスク(113)を形成する(工程3a、3b)。マスク(113)を用いた熱酸化処理を施してLocos形成領域を酸化させ、半導体基板(100、101)のドリフト領域上に厚さが異なる(115a、155b)Locos酸化膜(105a、105b)を同時に形成する(工程4a、4b)。

(もっと読む)

半導体装置

【課題】横型DMOSの素子面積の増大を抑制し高耐圧化をはかる。

【解決手段】第1の半導体素子100Aは、第1半導体層12Aと、第2半導体層14Aと、第2半導体層に隣接する第3半導体層16Aと、第1絶縁層20Aと、第2半導体層の表面に選択的に設けられた第1ベース領域30Aと、第1ベース領域の表面に選択的に設けられた第1ソース領域32Aと、第1絶縁層の内部に設けられた第1ゲート電極40Aと、第1ベース領域の下に設けられ、第1半導体層の表面から第1ベース領域の側に延在する第1ドリフト層18Aと、第1ソース領域32Aに対向し、第1絶縁層20Aを挟んで第3半導体層16Aの表面に設けられた第1ドレイン領域34Aを有す。第1ドリフト層18Aの不純物元素の濃度は、第1半導体層12Aの不純物元素の濃度よりも低い。第1ドリフト層の不純物元素の濃度は、第2半導体層14Aの不純物元素の濃度よりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】 寄生ダイオードの逆回復時間を短縮でき、スイッチング損失の低減が図れるLDMOSトランジスタを低コストで提供する。

【解決手段】 LDMOSトランジスタT1が、p型半導体基板1内にp型ボディ領域2とp型埋め込み拡散領域3とn型ドリフト領域6を、ボディ領域2内にn型ソースコンタクト領域4とp型ボディコンタクト領域5を、ドリフト領域6内にn型ドレインコンタクト領域7を、ソースコンタクト領域7とドリフト領域6間のボディ領域2の上方にゲート絶縁膜8を、ゲート絶縁膜8上にゲート電極9を夫々備えて形成され、ドリフト領域6とボディ領域2は相互に接触し、埋め込み拡散領域3が、ボディ領域2の底面と接触するボディ領域2よりも深い位置に、半導体基板1の表面に平行な方向に、少なくともボディ領域2からドレインコンタクト領域7のボディ領域2から最も離間した遠方端の下方まで延在している。

(もっと読む)

半導体装置

【課題】大規模な変更を必要とせず開発上の負荷が小さい半導体装置を提供する。

【解決手段】High SideのIGBTにおける比(コレクタコンタクト面積/コレクタ活性面積)および比(p+領域上コンタクト面積/p+領域面積)の少なくともいずれかが、Low SideのIGBTにおける上記比よりも高い。

(もっと読む)

半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離領域を縮小化しつつ、第1のMISトランジスタの閾値電圧を、第2のMISトランジスタの閾値電圧に比べて低くする。

【解決手段】半導体装置は、第1のMISトランジスタTrlと第2のMISトランジスタTrhとを備えている。第1のMISトランジスタTrlは、第1の活性領域1aにおける第1導電型の第1のエクステンション領域8Aの下に形成された第2導電型の第1のポケット領域9Aと、第1の活性領域1aにおける第1のポケット領域9Aの下に形成された拡散抑制不純物を含む第1の拡散抑制領域7Aとを備えている。第2のMISトランジスタTrhは、第2の活性領域に1bおける第1導電型の第2のエクステンション領域8Bの下に形成された第2導電型の第2のポケット領域9Bとを備えている。第1のポケット領域9Aの拡散深さは、第2のポケット領域9Bの拡散深さに比べて浅い。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

半導体基板およびその製造方法、その半導体基板を用いた半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した厚さを有する半導体層が1つの絶縁膜上に設けられた半導体基板およびその製造方法、その半導体基板を用いた半導体装置を提供する。

【解決手段】実施形態に係る半導体基板10は、第1絶縁層5と、前記第1絶縁層の上に設けられた半導体層7とを有する半導体基板であって、前記半導体層の中に選択的に設けられ、前記半導体層の表面に平行に延在し、その延在方向の長さが前記第1絶縁層よりも短い第2絶縁層13と、前記半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記半導体層の前記第2絶縁層を含む部分と、前記半導体層の残りの部分と、を電気的に分離する第3絶縁層15と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】BiCMOSプロセスにより製造される半導体装置において、V−NPNトランジスタの製造工程を合理化する。また、そのトランジスタのhFEを大きな値に調整する。

【解決手段】N+型エミッタ領域14Eの下のP型ベース領域7の底部に接触してN型ベース幅制御層9が形成されている。N型ベース幅制御層9が形成されることで、N+型エミッタ領域14Eの下のP型ベース領域7が局所的に浅くなっている。また、P型ベース領域7は、P型ウエル領域6の形成工程を用いて形成し、N型ベース幅制御層9は、N型ウエル領域8の形成工程を用いて形成することにより、工程合理化を図ることができる。

(もっと読む)

半導体装置、半導体パッケージ、および半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】N型基板10と、N型基板10の一面側に設けられたP型ウェル40と、P型ウェル40に設けられたP型高濃度不純物領域42と、P型ウェル40に設けられたN型のソース・ドレイン領域を有するMOSトランジスタ20と、N型基板10の一面側に設けられ、かつ一方がP型高濃度不純物領域42と電気的に接続し、他方が接地されているソース・ドレイン領域を有するMOSトランジスタ30と、を備える。

(もっと読む)

半導体基板、その製造方法及び半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した半導体層が1つの絶縁膜上に設けられた半導体基板、その製造方法及び半導体装置を提供する。

【解決手段】実施形態に係る半導体基板は、第1絶縁層と、前記第1絶縁層の上に設けられた第1半導体層と、前記第1半導体層の上に選択的に設けられた第2絶縁層と、前記第2絶縁層を介して前記第1半導体層の上に設けられた第2半導体層と、を備える。さらに、前記第1半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記第1半導体層における前記第1絶縁層と前記第2絶縁層との間の部分と、前記第1半導体層の残りの部分と、を電気的に分離した第3絶縁層を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに絶縁分離された複数の素子を有する半導体装置の小型化と、その製造コストの低減とを実現できるようにする。

【解決手段】半導体装置は、第1の素子151、第2の素子152、第3の素子153及び第4の素子154を備えている。基板100は、基板を貫通する第1素子分離領域131により互いに分離された第1の区画101及び第2の区画102を有している。第1の区画は、第2素子分離領域132により互いに分離された第1素子領域121及び第2素子領域122を含む。第2の区画は、第3素子分離領域133により互いに分離された第3素子領域123及び第4素子領域124を含み、基板の裏面に露出した裏面拡散層を有している。第3の素子は、第3素子領域に形成され、第4の素子は、第4素子領域に形成され、第3の素子及び第4の素子は、裏面拡散層105を介在させて互いに接続されている。

(もっと読む)

半導体装置の製造方法およびCMOSイメージセンサーの製造方法

【課題】 半導体装置に発生するノイズを低減する

【解決手段】 シリコン基板100の第1部分110を覆い、シリコン基板100の第1部分110に隣接する第2部分120を覆わない窒化シリコン膜200をマスクとしてシリコン基板100を熱酸化することにより、酸化シリコン膜300を形成する。窒化シリコン膜200をマスクとして酸化シリコン膜300のバーズビーク部310の下へ斜めイオン注入を行うことにより、不純物領域121を形成する。

(もっと読む)

1 - 20 / 380

[ Back to top ]