Fターム[5F048BF07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 材料 (4,535) | 金属、合金、金属化合物(シリサイドを除く) (1,473)

Fターム[5F048BF07]に分類される特許

1,461 - 1,473 / 1,473

半導体装置及びその製造方法

【課題】MOS−FETの駆動力を向上させる高性能な半導体装置及びその製造方法を提供すること。

【解決手段】CMOS−FET回路を備える半導体装置において、NMOS形成領域周辺の素子分離膜(102)の一部に設けられ引張応力を有する引張応力膜(119)と、PMOS形成領域周辺の素子分離膜(102)の一部に設けられ圧縮応力を有する圧縮応力膜(120)と、の少なくとも一方を備えている。

(もっと読む)

独立して歪むNチャネル型及びPチャネル型トランジスタ

第一ウェハ上に形成された第一の複数のトランジスタと、第二ウェハ上に形成された第二の複数のトランジスタとを備えた集積回路。第一トランジスタのうち少なくとも実質的に大部分が第一導電型であり、第二の複数のトランジスタのうち少なくとも実質的に大部分が第二導電型である。ウェハ同士が結合された後、第二ウェハの一部が除去されて、第二の複数のトランジスタのチャネルの歪みの圧縮性が、第一の複数のトランジスタのチャネルの歪みの圧縮性よりも高くなる。  (もっと読む)

(もっと読む)

チャネルキャリア移動度向上のための高応力ライナーを備えたSi−Geに基づく半導体デバイス

応力ライナーを用いることで、Si−Geデバイスのトランジスタのチャネル領域のキャリア移動度が増加される。一実施形態においては、緩和ソース/ドレイン領域を覆う高圧縮膜あるいは高引っ張り応力膜を適用する。他の実施形態としては、ポストシリサイドスペーサを除去した後、P−チャネルトランジスタあるいはN−チャネルトランジスタのゲート電極(72)および歪みソース/ドレイン領域(71)にそれぞれ、高圧縮応力膜(90)あるいは高引っ張り応力膜(120)を適用する。  (もっと読む)

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

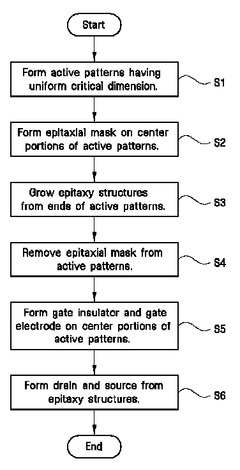

均一な臨界寸法のアクティブパターンで形成されたマルチゲートトランジスタ及びその製造方法

本発明は、均一な臨界寸法のアクティブパターンで構成されたマルチゲートトランジスタの製造方法を提供する。本発明はまた、均一な臨界寸法のアクティブパターンを具備するマルチゲートトランジスタを提供する。マルチゲートトランジスタの製造方法は先に少なくとも一つのアクティブパターンを形成する。以後、前記アクティブパターンの露出した領域から少なくとも一つのエピタキシ構造を成長させる。続いて、前記アクティブパターンの少なくとも2個の面にチャネル領域を形成する。  (もっと読む)

(もっと読む)

パワー半導体装置およびそのための方法

パワー・トランジスタは、複数のトランジスタ・セルを含む。トランジスタ・セルは、それぞれ、第1主表面を覆う第1電極相互接続領域へ結合された第1電極、第1主表面を覆う制御電極相互接続領域へ結合された制御電極、および、第2主表面を覆う第2電極相互接続領域へ結合された第2電極を有する。各トランジスタ・セルは、チャネル領域においてほぼ一定のドーピング濃度を有する。誘電性プラットフォームはエピタキシャル層の終端として使用され、実質的に平坦な等電位線を維持する。パワー・トランジスタは、500メガヘルツを越える周波数で動作し、5ワットを超える電力を放散する無線周波数への応用に特に利用価値がある。パワー・トランジスタがそのような厳しい条件下で効率的に動作することができるように、半導体ダイおよびパッケージが設計される。 (もっと読む)

減少されたコンタクト高さでのバイポーラ及びCMOSの集積回路構造体

【課題】 複数の高さのデバイスを含む集積回路構造体であって、このようなデバイスに形成されたコンタクトの高さを減少させるために保護層の高さを減少させた、改善された構造体を提供すること。

【解決手段】 単一の基板上に配置された複数の相補型金属酸化膜半導体(CMOS)トランジスタ及び複数の垂直バイポーラ・トランジスタを含む集積回路構造体のための方法及び構造体が開示される。垂直バイポーラ・トランジスタは、CMOSトランジスタより高さのあるデバイスである。この構造体においては、保護層が、基板の上に、及び、垂直バイポーラ・トランジスタとCMOSトランジスタとの間に配置される。配線層は保護層の上にある。垂直バイポーラ・トランジスタは、配線層と直接接触しており、CMOSトランジスタは保護層を通って延びるコンタクトによって配線層に接続されている。

(もっと読む)

半導体装置と半導体装置の製造方法

バリア性を有する絶縁膜サイドウォールスペーサを有する半導体装置を提供する。 半導体装置は、半導体基板の上に形成されたゲート酸化膜とゲート電極と;半導体基板内に形成されたソース/ドレイン領域と;ゲート電極側壁上に形成された2層以上の積層サイドウォールスペーサであって、最外層以外の層として窒化膜を含み、最外層は、酸化膜又は酸化窒化膜で形成され、下面が半導体基板またはゲート酸化膜、又は窒化膜以外の他のサイドウォールスペーサ層と接している第1積層サイドウォールスペーサと;を有する。さらに、不揮発性メモリの積層ゲート電極構造と;積層ゲート電極構造の側壁上に形成され、中間層として半導体基板に接しない窒化膜を含む3層以上の第2積層サイドウォールスペーサと;を有することもできる。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

同じ半導体チップ内のPMOSおよびNMOSトランジスタの薄いゲート誘電体を個々に最適化する方法、およびそれによって製造されたデバイス

【課題】半導体基板(12)に形成され、シリコン酸化物およびそれの異なる程度の窒化(18Dと18E)で構成されたPFETゲート誘電体層(16)およびNFETゲート誘電体層(14)でそれぞれ覆われたPFET領域およびNFET領域を有するCMOS半導体(10)材料を形成する方法を提供すること

【解決手段】シリコン基板(12)にPFET領域(16)およびNFET領域(14)を設け、その上にPFETおよびNFETゲート酸化物層を形成する。PFET領域の上のPFETゲート酸化物層の窒化を行って、PFET領域の上のPFETゲート酸化物層に、第1の濃度レベルの窒素原子を有する、PFET領域の上のPFETゲート誘電体層(42)を形成する。NFETゲート酸化物層の窒化を行って、第1の濃度レベルと異なる濃度レベルの窒素原子を有する、NFET領域の上のNFETゲート誘電体層(40)を形成する。NFETゲート誘電体層(40)およびPFETゲート誘電体層(42)は、同じ厚さを有することができる。

(もっと読む)

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

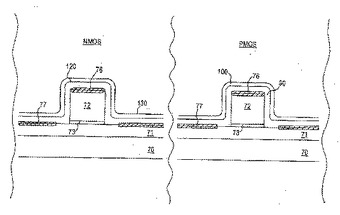

並列相補型FinFETの対を有する集積回路構造体及び該形成方法

【課題】 従来の単一のFinFETのスペースに2またはそれ以上のFinFETを形成すること。

【解決手段】 相補的フィン型電界効果トランジスタ(FinFET)を用いる集積回路構造体のための方法および構造体を開示する。本発明は、第1フィン(100)を含む第1型FinFETと、第1フィン(100)に並列に延在する第2フィン(102)を含む第2型FinFETを含む。また、本発明は、第1型FinFETおよび第2型FinFETのソース/ドレイン領域(130)の間に配置される絶縁体フィンを含む。第1型FinFETと第2型FinFETとの間隔が1個のフィンの幅とほぼ等しくなるように、絶縁体フィンは、第1フィン(100)および第2フィン(102)とほぼ同じ寸法の幅にされる。また、本発明は、第1型FinFETおよび第2型FinFETのチャネル領域を覆うように形成された共通ゲート(106)を含む。ゲート(106)は、第1型FinFETに隣接する第1不純物ドーピング領域と、第2型FinFETに隣接する第2不純物ドーピング領域とを含む。第1不純物ドーピング領域と第2不純物ドーピング領域の差異が、ゲートに、第1型FinFETと第2型FinFETとの差異に関係した異なる仕事関数を与える。第1フィン(100)および第2フィン(102)はほぼ同じ幅である。

(もっと読む)

パンチスルー・ダイオードおよびそれを処理する方法

ショットキーのような動作を有するモノリシック集積パンチスルー・ダイオード。これは、ショットキー金属領域(16)が第1のpドープ・ウェル(9)の表面の少なくとも一部に堆積されるときに実現される。ショットキー金属領域(16)およびpドープ・ウェル(9)は、ショットキー・ダイオードの金属−半導体−遷移を形成する。順方向特性が0.5V未満の電圧降下を有するので、発明のPTダイオードの過電圧保護は改善される。  (もっと読む)

(もっと読む)

1,461 - 1,473 / 1,473

[ Back to top ]