Fターム[5F048BG07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 絶縁体分離 (5,896) | 素子領域側面・底面を絶縁物で分離するもの (666) | 複数MOS(CMOS)ですべて (452)

Fターム[5F048BG07]に分類される特許

441 - 452 / 452

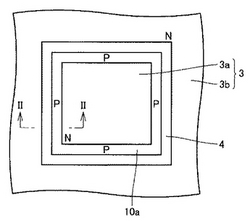

半導体装置およびその製造方法

【課題】 素子形成領域の占有面積を増大させることなく電気的分離が確実に行なわれる半導体装置と、その製造方法を提供する。

【解決手段】 半導体基板上にBOX層を介在させてN−層3が形成されている。そのN−層3には素子形成領域となるN−層3aを取囲むようにトレンチ分離領域4が形成されている。トレンチ分離領域4はN−層3の表面からBOX層に達するように形成されている。トレンチ分離領域4の外側には、他の素子形成領域となるN−層3bが位置している。トレンチ分離領域4とN−層3aとの間には、P型拡散領域10aが形成されている。P型拡散領域10aは、素子形成領域を取囲むトレンチ分離領域4の内側側壁の全面に接するように切れ目なく連続して形成されている。N−層3a等の素子形成領域には、所定の半導体素子が形成される。

(もっと読む)

半導体装置

【課題】 ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】 ソース/ドレイン領域の一方になり、かつビット線にもなる第1の不純物拡散層24の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板表面内に複数の異なる結晶方位を有し、その各部において基板へのリーク電流の増大や消費電力の増大を抑制可能な半導体装置及びその製造方法を実現する。

【解決手段】同じ結晶方位<110>同士が所定の角度(例えば45°)だけずれた状態となるよう、2枚の半導体ウェハを貼り合わせてSOI基板を形成する。そのSOI基板の表面の一部を埋め込み絶縁層までエッチングして、その部分にエピタキシャル成長を行う。そして、SIMOX技術により、エピタキシャル成長層形成部にも埋め込み酸化膜を設け、各部をSOI構造とする。

(もっと読む)

特徴の異なる結晶性半導体領域を有する基板の形成技術

第1結晶性半導体領域104a内に誘電領域111を形成することによって、単一基板上に異なるタイプの結晶性半導体領域が与えられる。その後、この誘電領域111上には、第2結晶領域152aがウェハ接合技術によって位置決めされる。好ましい実施形態では、誘電領域とともに、第1結晶領域にアイソレーション構造が形成されてもよい。特に、結晶方向の異なる結晶性半導体領域が形成されてもよく、高度なフレキシビリティと、現在利用されているCMOSプロセスとの互換性が維持される。  (もっと読む)

(もっと読む)

高速CMOS共存Ge−オン−インシュレータ光検出器の構造および製作方法

【課題】SiCMOS技術と共存可能な高速高効率光検出器を作る問題に対処すること。

【解決手段】本構造は、薄いSOI基板の上のGe吸収層から成り、分離領域、交互になるn型およびp型コンタクト、および低抵抗表面電極を利用する。本デバイスは、下の基板で生成されたキャリアを分離するために埋込み絶縁物を利用して高帯域幅を、Ge吸収層を利用して広いスペクトルにわたった高量子効率を、薄い吸収層および狭い電極間隔を利用して低電圧動作を、さらに平面構造およびIV族吸収材料の使用によってCMOSデバイスとの共存性を、達成する。本光検出器を製作する方法は、薄いSOIまたはエピタキシャル酸化物へのGeの直接成長および高品質吸収層を達成するための後の熱アニールを使用する。この方法は、相互拡散に利用可能なSiの量を制限し、それによって、下のSiによるGe層の実質的な希釈を起こすことなく、Ge層をアニールすることができるようになる。

(もっと読む)

シャロウトレンチ分離プロセスおよび構造

集積回路(IC)を製造する方法は、シャロウトレンチ分離(STI)技術を利用する。シャロウトレンチ分離技術は歪みシリコン(SMOS)プロセス中において使用される。トレンチ(34)を形成した後、歪み材料(36)を形成する。このプロセスは、埋込酸化膜(BOX)層(14)上の化合物半導体層16上で利用される。  (もっと読む)

(もっと読む)

Si:C−OIおよびSGOI上のシリコン・デバイスならびに製造方法

【課題】より費用効果が高くより簡略な、大きな引張り応力および圧縮応力をそれぞれnFETおよびpFETのチャネル中で生成する方法を提供すること。半導体構造および製造方法を提供すること。

【解決手段】この製造方法は、基板中に浅いトレンチ分離(STI)(25)を形成するステップと、基板上に第1の材料(30)および第2の材料(40)を設けるステップとを含む。第1の材料(30)および第2の材料(40)は、熱アニール・プロセスによって基板中に混合され、それぞれnFET領域の第1のアイランド(50)、およびpFET領域の第2のアイランド(55)を形成する。第1のアイランド(50)および第2のアイランド(55)の上に、材料層を形成する。STIは、緩和して、第1のアイランド(50)および第2のアイランド(55)の緩和を促進する。第1の材料(30)は、堆積または成長させたGe材料とすることができ、第2の材料(40)は、堆積または成長させたSi:CまたはCとすることができる。第1のアイランド(50)および第2のアイランド(55)の少なくとも一方の上に、歪みSi層を形成する。

(もっと読む)

半導体基板の製造方法及び半導体基板

半導体基板100は、単結晶シリコン基板の主表面に目的の膜厚のマスクを形成し、主表面に対して高温下で酸素イオンを打ち込み、主表面上に酸素を遮断する表面保護層を形成してアニールを行い、マスク及び表面保護層を剥離することで得られる。二酸化シリコン層102は、マスクが存在しなかった領域に対応する主表面100aからの距離が相対的に大きい第1の頂面102aと、マスクが存在した領域に対応する主表面100aからの距離が相対的に小さい第2の頂面102bとを有する。この主表面100aを所望量だけ研磨することで、単結晶シリコン基板の一部分のみがSOI基板となっている半導体基板が得られる。  (もっと読む)

(もっと読む)

完全空乏型シリコン・オン・インシュレータのCMOSロジック

【課題】SOI技術を用いた部分空乏型CMOSデバイスにおける浮遊ボディの不必要な影響を制御可能とする。

【解決手段】シリコン・オン・インシュレータのCMOSメモリデバイスにおいて、引き出し線を含む領域が用いられる。引き出し線を逆方向にバイアスすることで、部分空乏型メモリセルのボディ領域から少数キャリアを取り除く。これにより、ボディ領域を完全空乏化し、浮遊ボディの不必要な影響を抑制する。

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

並列相補型FinFETの対を有する集積回路構造体及び該形成方法

【課題】 従来の単一のFinFETのスペースに2またはそれ以上のFinFETを形成すること。

【解決手段】 相補的フィン型電界効果トランジスタ(FinFET)を用いる集積回路構造体のための方法および構造体を開示する。本発明は、第1フィン(100)を含む第1型FinFETと、第1フィン(100)に並列に延在する第2フィン(102)を含む第2型FinFETを含む。また、本発明は、第1型FinFETおよび第2型FinFETのソース/ドレイン領域(130)の間に配置される絶縁体フィンを含む。第1型FinFETと第2型FinFETとの間隔が1個のフィンの幅とほぼ等しくなるように、絶縁体フィンは、第1フィン(100)および第2フィン(102)とほぼ同じ寸法の幅にされる。また、本発明は、第1型FinFETおよび第2型FinFETのチャネル領域を覆うように形成された共通ゲート(106)を含む。ゲート(106)は、第1型FinFETに隣接する第1不純物ドーピング領域と、第2型FinFETに隣接する第2不純物ドーピング領域とを含む。第1不純物ドーピング領域と第2不純物ドーピング領域の差異が、ゲートに、第1型FinFETと第2型FinFETとの差異に関係した異なる仕事関数を与える。第1フィン(100)および第2フィン(102)はほぼ同じ幅である。

(もっと読む)

441 - 452 / 452

[ Back to top ]