Fターム[5F048BG11]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 絶縁体分離 (5,896) | 素子領域側面のみを絶縁物で分離するもの (4,648)

Fターム[5F048BG11]の下位に属するFターム

選択酸化(LOCOS)分離 (1,064)

トレンチ(溝)分離 (3,479)

V溝 (2)

Fターム[5F048BG11]に分類される特許

61 - 80 / 103

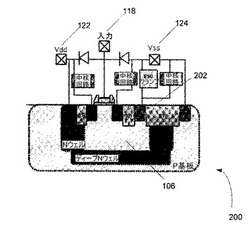

集積回路のためのCDMESD保護

【課題】改良された静電放電(ESD)保護回路、より詳細には、集積回路(IC)の保護回路におけるデバイス帯電モデル(CDM)ストレスの場合に対する改良を提供すること。

【解決手段】本発明は、集積回路(IC)のためのデバイス帯電モデル(CDM)静電放電(ESD)保護回路を提供する。ESD保護回路は、第1の導電タイプの基板と、基板上の第1のウェルに形成され、パッドに結合された第2の導電タイプのMOS構成部分と、第1のウェルと基板を隔離するための第1のウェルと基板との間に形成された第2の導電タイプを有する隔離ウェル/領域と、を含む。加えて、回路は、隔離されたウェル/領域に結合されたESDクランプを含む。通常電力の動作中、ESDクランプは開放されている。CDM ESD事象中、基板およびMOS構成部分内に蓄積されたCDM電荷は、ICへの損傷を防止するためにESDクランプにより取り除かれる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板側への金属材料のリークを防止したフルシリサイドゲートの形成が可能で、これによりフルシリサイドゲートを備えながらも素子特性を維持することが可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上にパターン形成されたゲート絶縁膜3と、ゲート絶縁膜3上にパターン形成されたゲート電極5a’とを備えた半導体装置40であって、ゲート電極5a’は、全層がシリサイド化されたものであり、ゲート絶縁膜3よりも狭い幅でゲート絶縁膜3の中央に設けられている。

(もっと読む)

半導体集積回路装置

【課題】 デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としないSOI基板及び半導体集積回路装置を提供する。

【解決手段】 P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体基板上に引っ張り応力を有する層間絶縁膜や配線用金属膜等の形成された半導体装置において、ウェハの反りを抑制できる半導体装置を提供する。

【解決手段】 半導体素子が形成された半導体基板10と、半導体基板10上に堆積された1または複数層の配線用金属膜16a、16b、18を備えてなる半導体装置であって、1または複数層の配線用金属膜の内、1つの配線用金属膜の堆積によって生じるウェハ反り量の絶対値が最大となる第1配線用金属膜18の下層側及び上層側の少なくとも何れか一方側に、ウェハ反り量を緩和する応力緩和膜17を備え、応力緩和膜17が圧縮応力を有し、第1配線用金属膜18が引っ張り応力を有し、応力緩和膜17の堆積によって生じるウェハ反り量の絶対値が、第1配線用金属膜18の堆積によって生じるウェハ反り量の絶対値より小さい。

(もっと読む)

CMOS半導体素子及びその製造方法

【課題】デュアルメタルゲートCMOS半導体素子を提供する。

【解決手段】金属窒化物層及び多結晶シリコンキャッピング層を備え、nMOS領域及びpMOS領域の金属窒化物層は同種物質で形成され、相異なる不純物含有量により相異なる仕事関数を持つデュアルメタルゲートCMOS半導体素子。同種の金属窒化物層によりメタルゲートを形成するので、工程が単純化して収率が向上すると共に、高性能のCMOS半導体素子を得ることができる。

(もっと読む)

相補型半導体装置

【課題】同一GOI基板上に形成するp型MISFET及びn型MISFETの両方の駆動力を向上させる。

【解決手段】GOI基板上にp型MISFETとn型MISFETを形成した相補型半導体装置であって、絶縁膜12上に形成され、表面の面方位が(110)面であり、一部にエッチングにより(111)面が露出されたGe層13と、Ge層13の(110)面に形成されたp型MISFETと、Ge層13の(111)面に形成されたn型MISFETとを備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトライナー膜の下地依存性を解消できる構造を備えた半導体装置を提供する。

【解決手段】半導体装置は、活性領域100上において、ゲート絶縁膜102と、ゲート電極103と、サイドウォール105と、ソースドレイン領域106と、シリサイド領域107とを備える。さらに、活性領域100上に、ゲート電極103、サイドウォール105、及びシリサイド領域107を覆うように、ALD法によって形成された下地絶縁膜108と、下地絶縁膜108の上に、プラズマCVD法によって形成され、チャネル領域におけるゲート長方向に引張応力を印加する応力絶縁膜からなるコンタクトライナー膜109とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、同一基板に低電圧動作及び高電圧動作の各半導体素子を作り込む場合、素子分離領域の高さを基板表面との間で適切に選択することで高電圧動作の半導体素子に於ける不良発生を抑止する。

【解決手段】半導体基板1に形成された低電圧動作半導体素子及び高電圧動作半導体素子を含む半導体装置に於いて、低電圧動作半導体素子に於ける素子分離領域は、その表面が半導体基板1の表面と等しい高さを維持して形成され、高電圧動作半導体素子に於ける素子分離領域は、その表面が半導体基板1の表面に比較して低い高さを維持して形成されている。

(もっと読む)

半導体装置の製造方法

【課題】所望の特性を有するトランジスタを精度よく形成する。

【解決手段】トランジスタのエクステンション領域を形成するためのオフセットスペーサとしてシリコン窒化膜を用いる場合に、レジスト膜を除去する工程の前に、シリコン窒化膜表面に酸素プラズマ処理により酸化保護表面を形成しておく。

(もっと読む)

半導体装置の製造方法

【課題】不純物注入領域を高濃度に活性化させるとともに、ゲートリーク電流を低減させ得る半導体装置の製造方法を提供する。

【解決手段】浅いソース・ドレインエクステンションを活性化させる際に、nMOSにおいてスパイクRTA(第1のアニール)とこれより昇降温速度の大きい超高速昇降温アニール(第2のアニール)を併用し、pMOSにおいては超高速昇降温アニール(第2のアニール)のみを適用する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリ部とロジックとを含む半導体装置において、工程数を増大させることなく、ロジック部に高さが異なるゲート電極を含むトランジスタを形成できるようにする。

【解決手段】半導体装置は、メモリ部Aとロジック部Bとを有する半導体領域1A、1B、1Cと、半導体領域のメモリ部Aにメモリゲート絶縁膜2を介して形成されたメモリゲート電極31を有するメモリトランジスタ30と、ロジック部Bの第1の領域B1に形成され、第1のゲート電極41を有するp型トランジスタ40と、ロジック部Bの第2の領域B2に形成され、第2のゲート電極51を有するn型トランジスタ50とを有している。メモリゲート電極31は、第1電極4及び第2電極9を含み、第1のゲート電極41は第1電極4及び第2電極9が電気的に接続され、第2のゲート電極51は第2電極9からなり、第1の側壁絶縁膜10の膜厚は、第2の側壁絶縁膜11の膜厚よりも厚い。

(もっと読む)

エージングデバイス及びその製造方法

【課題】エージングデバイスの寿命を正確にコントロールする。

【解決手段】本発明の例に関わるエージングデバイスは、上面が半導体基板11の上面よりも上にある素子分離絶縁層12と、素子分離絶縁層12により分離される第1及び第2素子領域13,14と、第1素子領域13内の半導体基板11内に形成される第1及び第2拡散層15a,15b,16a,16bと、第1及び第2拡散層間15a,15b,16a,16bの半導体基板11上に形成される第1ゲート絶縁膜19と、第2素子領域14内の半導体基板11上に形成される第2ゲート絶縁膜19と、第1及び第2ゲート絶縁膜19上に形成され、第1素子領域13から第2素子領域14まで跨って形成されるフローティングゲート電極20とを備え、第1及び第2拡散層15a,15b,16a,16bの最も深い部分は、素子分離絶縁層12から離れている。

(もっと読む)

半導体装置及びその製造方法

【課題】コーナーラウンディング現象に起因するゲート電極寸法の変化及びトランジスタ特性の劣化を防止することができるゲート電極を備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、素子分離領域102と、素子分離領域102に囲まれた活性領域103と、素子分離領域102及び活性領域103上に形成されたゲート電極105とを備える。素子分離領域102上のゲート電極105における上面のゲート長方向の線幅LbTは、活性領域103上のゲート電極105における上面のゲート長方向の線幅LaTとほぼ等しく、素子分離領域102上のゲート電極105における下面のゲート長方向の線幅LbBは、活性領域103上のゲート電極105における下面のゲート長方向の線幅LaBよりも長い。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】第1導電型の半導体基板上の第2導電型半導体層にDMOSトランジスタを形成する場合において、埋込層を形成せずに素子分離を行い、製造工程数を削減する。

【解決手段】半導体基板10に、ドレインとして機能する第2導電型不純物領域13を形成し、半導体基板10上及び第2導電型不純物領域13上に、半導体基板10より不純物濃度が高い第1導電型半導体層30を形成し、第1導電型半導体層30上に第2導電型半導体層20を形成する。第2導電型不純物領域13の不純物を第1導電型半導体層13に拡散させ、第2導電型不純物領域13を第1導電型半導体層30まで拡張して第2導電型半導体層20に接続させる。その後、第2導電型不純物領域13の周囲の上方に位置する第2導電型半導体層20に第1導電型不純物を導入することにより、第1導電型半導体層30に接続する第1導電型の素子分離領域24c,24dを形成する。

(もっと読む)

半導体装置の製造方法

【課題】メモリアレイ領域のソース・ドレイン拡散層に適した熱処理条件を採用しつつも、周辺回路領域のソース・ドレイン拡散層での不純物の過度の拡散を抑制できるDRAM等の半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、メモリアレイ領域10Aのシリコン基板11内に不純物を注入し、メモリアレイ領域10Aのゲート電極14に対応してソース・ドレイン拡散層を形成する第1拡散層形成工程と、メモリアレイ領域10Aのソース・ドレイン拡散層内の不純物を拡散する熱処理工程と、周辺回路領域10B,10Cのシリコン基板11内に不純物を注入し、周辺回路領域10B,10Cのゲート電極14に対応してソース・ドレイン拡散層を形成する第2拡散層形成工程とをこの順に有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】CVD法により上部電極を成膜する際の下地層へのダメージを防止する半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板11上の層間絶縁膜16に設けられた凹部17の内壁を覆う状態で、層間絶縁膜16上にゲート絶縁膜18を形成する工程と、ゲート絶縁膜18上に、仕事関数を制御する第1ゲート電極層19aを形成する第1工程と、第1ゲート電極層19a上に、下地層へのバリア性を有する第2ゲート電極層19bを形成する第2工程と、第2ゲート電極層19bが設けられた凹部17を埋め込む状態で、第2ゲート電極層19b上に、化学的気相成長法により、第1ゲート電極層19aよりも抵抗の低い第3ゲート電極層19cを形成する第3工程とを行うことを特徴とする半導体装置の製造方法と半導体装置である。

(もっと読む)

半導体装置とその製造方法

【課題】ゲート絶縁膜のリーク電流の増加を抑制することができる半導体装置を得ること。

【解決手段】シリコン基板1上にSiON膜12−1aを形成する工程と、SiON膜12−1a上にハフニウムと酸素とが結合したハフニウムオキサイドを含むハフニウムオキサイド膜12−2aを形成する工程と、ハフニウムオキサイド膜12−2a中にハフニウムをイオン注入する工程と、ハフニウムをイオン注入したハフニウムオキサイド膜12−2aをアニール処理して活性化させる工程と、ハフニウムオキサイド膜12−2a上にゲート電極となるPt膜を形成する工程と、Pt膜、ハフニウムオキサイド膜12−2a、SiON膜12−1aを所定の形状にパターニングする工程と、を含む。

(もっと読む)

グラフェン集積回路

【課題】グラフェンを含む非線形素子を集積化する技術を提供し、半導体の集積度を向上させる。

【解決手段】シリコンカーバイド基板のシリコン面に形成されたグラフェンを含む非線形素子を有するグラフェン集積回路、及びその製造方法。当該製造方法は、絶縁膜で被覆されたシリコン面を有するシリコンカーバイド基板を準備する工程、複数の所望の部位の前記絶縁膜を除去してシリコン面を露出させる工程、前記シリコンカーバイド基板を加熱することによって前記露出部位にグラフェンを形成する工程、及び前記グラフェンにオーミック電極を形成する工程を含むか、或いはシリコン面を有するシリコンカーバイド基板を加熱することによって当該シリコン面にグラフェンを形成する工程、前記グラフェンをアイソレーションする工程、前記アイソレーションにより形成された溝に絶縁膜を形成する工程、及び前記グラフェンにオーミック電極を形成する工程を含みうる。

(もっと読む)

デジタル−アナログ変換器

【課題】構成が簡素で高精度な変換性能を有するデジタル−アナログ変換器を提供する。

【解決手段】本発明に係るデジタル−アナログ変換器は、MOS構造のトランジスタと複数のキャパシタとを備え、前記トランジスタは、半導体基板の主表面に形成されたソースと、前記半導体基板の主表面に形成され、アナログ信号出力端子となるドレインと、前記ソースとドレインとの間の前記主表面上に絶縁膜を介して形成されたゲートと、から構成され、複数の前記キャパシタは、互いに電気的に絶縁されて前記半導体基板の主表面に複数のデジタル信号入力端子として形成された不純物領域からなる複数の第一電極と、前記不純物領域上に絶縁膜を介して前記第一電極と対向するように前記ゲートと一体的に形成された第二電極と、から構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 STIを形成することなく素子間の分離を可能にし、高密度に集積化できる半導体装置及びその製造方法を提供する。

【解決手段】 シリコン基板表面に段差を設けて、互いに異なる表面を形成し、各表面にトランジスタを形成し、トランジスタ間をシリコン層と絶縁性のサイドウォールとによって絶縁分離する。STIを設けていないため、トランジスタを高密度に集積できる。

(もっと読む)

61 - 80 / 103

[ Back to top ]