Fターム[5F048BG11]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 絶縁体分離 (5,896) | 素子領域側面のみを絶縁物で分離するもの (4,648)

Fターム[5F048BG11]の下位に属するFターム

選択酸化(LOCOS)分離 (1,064)

トレンチ(溝)分離 (3,479)

V溝 (2)

Fターム[5F048BG11]に分類される特許

41 - 60 / 103

半導体装置及びその製造方法

【課題】高誘電率ゲート誘電膜を用いるpチャネルFETをゲート先作りプロセスにより形成すると閾値が大きくなる。

【解決手段】High-Kゲート誘電膜104の側面と接触するようにHigh-K誘電膜102を形成した後、酸素雰囲気中でアニールする。

(もっと読む)

半導体装置、およびその製造方法

【課題】良好な形状のキャップ層を形成して、容易に適した仕事関数に制御することができる半導体装置、およびその製造方法を得ることを目的とする。

【解決手段】本発明における半導体装置の製造方法は、high−k膜2および第1のゲート電極膜3が積層したゲートパターンが形成されるとともに、ゲートパターンをマスクとして、第1導電型および第2導電型のソース・ドレイン領域12を形成する。次に、ゲートパターンの周囲を含む全面に層間絶縁膜14を形成する。次に、第1導電型のMISFET形成領域8の第1のゲート電極膜を除去して溝部20aを形成する。次に、溝部20aの底面および側面を含む全面に積層するようにキャップ層15を形成する。次に、溝部20aを埋め込むように第2のゲート電極膜16を形成する。次に、第2導電型のMISFET形成領域9の第1のゲート電極膜3の表面が露出するように除去しキャップ層15を拡散する。

(もっと読む)

半導体装置の製造方法

【課題】逆短チャネル効果を抑制し、かつトランジスタのしきい値電圧を低下させることが可能な半導体装置の製造方法を得ることを目的とする。

【解決手段】本発明の一実施形態における半導体装置の製造方法は、窒素が上面内に注入されたp型の半導体領域2を有する下地1を準備し、この下地1上にゲート絶縁膜5およびゲート電極6をこの順で積層して形成する。次に、ゲート電極6をマスクとして、p型の一対のポケット注入領域7および当該ポケット注入領域7の外方にn型の一対のソース・ドレイン領域10を下地1の上面内に形成する。次に、下地1上を被覆してゲート絶縁膜5下の下地1に応力を印加する応力膜11を積層する。次に、下地1に熱処理を行い前記ソース・ドレイン領域10を活性化した後、積層した応力膜11を除去する。

(もっと読む)

半導体装置

【課題】同一の素子領域に、第1のゲート絶縁膜を備える第1のMIS型トランジスタと、第2のゲート絶縁膜を備える第2のMIS型トランジスタとを設ける半導体装置では、素子領域の周囲を取り囲む素子分離膜の傾斜部の膜減りにより、第1のMIS型トランジスタ、および第2のMIS型トランジスタのリーク電流の発生を防止できなかった。

【解決手段】本発明の半導体装置は、素子分離膜の傾斜部の上部に、第1のゲート絶縁膜、第2のゲート絶縁膜、あるいはそれらの絶縁膜とは膜厚が異なる上部絶縁膜を設ける構造とする。このような構造とすることで、素子分離膜の傾斜部が膜減りすることがなく、リーク電流の発生を防止することが可能となる。

(もっと読む)

DC−DCコンバータ

【課題】一半導体基板上で寄生構造を改良し、昇圧動作起動時に突入電流を十分に抑制でき、常時安定して昇圧動作する高性能なDC−DCコンバータを提供すること。

【解決手段】このDC−DCコンバータの場合、各昇圧用トランジスタTr5〜Tr8を形成するための各P−拡散領域部は、それらの全体を囲うように一領域部として配設されたN−ウエル領域部により素子分離されていると共に、電源電圧VDDの印加されるP−型半導体基板上の電荷伝送用トランジスタTr1、Tr3を形成するためのN−拡散領域部から電気的に遮蔽された状態となるため、電源を投入した昇圧動作起動時に各昇圧用トランジスタTr5〜Tr8の寄生バイポーラ構造に電流トリガが流れても、電源電圧VDD用入力端子と入力電圧VIN用端子との間で過大電流の流れが阻止される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、閾値電圧(Vth)が低く、且つ半導体特性に問題が生じないハイブリッド構造の半導体装置を提供することを目的とする。

【解決手段】本発明は、基板1に設けた第1ソース領域2と第1ドレイン領域3との間の基板1上にhigh−k膜の第1ゲート絶縁膜4と、第1ゲート絶縁膜4上にポリシリコン膜の第1ゲート電極とを備えたn型の半導体素子と、基板1に設けた第2ソース領域2と第2ドレイン領域3との間の基板1上にhigh−k膜の第2ゲート絶縁膜4と、第2絶縁膜上に第1金属膜7,8と、第1金属膜7,8上にポリシリコン膜の第2ゲート電極とを備えたp型の半導体素子とを備えるハイブリッド構造の半導体装置である。そして、本発明の1つの実施形態では、第1金属膜8が、窒化チタン単体よりも仕事関数が高くなる添加物質を添加した窒化チタン膜を有している。

(もっと読む)

半導体装置の製造方法

【課題】プロセスを複雑化することなく、素子分離領域の膜減りによるトランジスタ特性の悪化が生じにくい半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、第1の酸化膜21、第1の窒化膜31及び第2の酸化膜22を順次形成する。次に、第3の領域10C及び第4の領域10Dの上に形成された、第2の酸化膜22及び第1の窒化膜31を除去した後、第3の酸化膜23、第2の窒化膜32及び第4の酸化膜24を順次形成する。次に、第3の領域10Cを除いて、第4の酸化膜24及び第2の窒化膜32を除去した後、第5の酸化膜25を形成する。次に、第2の領域10Bの上に形成された第5の酸化膜25、第3の酸化膜23、第2の酸化膜22及び第1の窒化膜31並びに第3の領域10Cの上に形成された第5の酸化膜25、第4の酸化膜24及び第2の窒化膜32を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域として用いるエピタキシャル成長結晶からゲート絶縁膜への不純物拡散による信頼性の低下を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、第1の面と、前記第1の面に対して傾斜した第2の面とを有するSiGe結晶層を形成する工程と、前記SiGe結晶層上に非晶質Si膜を形成する工程と、加熱処理を施すことにより、前記SiGe結晶層の前記第1および第2の面をシードとして、前記非晶質Si膜の前記第1および第2の面の近傍に位置する部分を結晶化させてSi結晶層を形成する工程と、前記非晶質Si膜の加熱処理により結晶化しなかった部分を選択的に除去、または薄くする工程と、前記Si結晶層の表面に酸化処理を施すことにより、前記Si結晶層の表面にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】電荷移動度を向上させる歪みをチャネル領域に発生させる結晶層をチャネル領域下に有し、かつリーク電流経路が形成されることを抑制できる半導体装置を提供する。

【解決手段】一態様に係る半導体装置は、半導体基板1と、前記半導体基板上に形成された第1の半導体結晶層14と、前記第1の半導体結晶層上にゲート絶縁膜11を介して形成されたゲート電極13と、前記第1の半導体結晶層内の前記ゲート絶縁膜下の領域に形成されたチャネル領域15と、前記第1の半導体結晶層内の前記チャネル領域を挟んだ領域に形成されたソース・ドレイン領域16と、前記半導体基板と前記チャネル領域との間に形成され、前記第1の半導体結晶層を構成する結晶よりも格子定数の大きい結晶からなり、前記半導体基板と前記第1の半導体層の間に、前記第2の半導体結晶層17を挟んで形成された埋込絶縁体層18と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】アクティブ領域間のリークの発生を抑制する半導体装置の製造方法を提供する。

【解決手段】高耐圧MOSトランジスタ領域および低耐圧MOSトランジスタ領域が定義された半導体基板上に耐酸化性膜を成膜する第1工程と、半導体基板表面を露出する高耐圧MOSトランジスタ領域酸化用開口を有する耐酸化性膜パターンを形成する第2工程と、耐酸化性膜パターン上に耐エッチング性膜を成膜する第3工程と、低耐圧MOSトランジスタ領域酸化用開口を有する耐エッチング性膜パターンを形成する第4工程と、耐エッチング性膜を除去し、低耐圧MOSトランジスタ領域酸化用開口及び高耐圧MOSトランジスタ領域酸化用開口の底面の半導体基板の表面を露出せしめる第5工程と、熱酸化法によって、酸化膜を成長させて低耐圧MOSトランジスタ領域用素子分離膜及び高耐圧MOSトランジスタ領域用素子分離膜を形成する第6工程と、を含む。

(もっと読む)

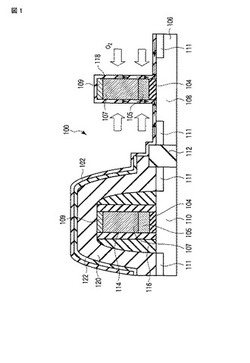

半導体装置およびその製造方法

【課題】ゲートラストプロセスで形成されたゲート構造において、ソース・ドレイン領域に接続するコンタクトとゲート電極とのショートを防ぐ。

【解決手段】半導体装置100は、ゲートラストプロセスで形成された第1のゲート210を含む。第1のゲート210は、絶縁膜中に形成された第1の凹部内の底面に形成されたゲート絶縁膜、当該第1の凹部内のゲート絶縁膜上に形成されたゲート電極、および当該第1の凹部内のゲート電極上に形成された保護絶縁膜140を含む。また、半導体装置100は、第1のゲート210の両側方のN型不純物拡散領域116aに接続され、第1の凹部よりも径が大きい第2の凹部内に埋め込まれたコンタクト134を含む。

(もっと読む)

半導体装置

【課題】複数列のゲート電極を備える半導体装置におけるトランジスタ特性のばらつきを低減する。

【解決手段】半導体基板70の上部にゲート長方向に並んで複数列に設けられたゲート電極10と、複数列のゲート電極10と同層に設けられてこれらを互いに電気的に接続するゲート接続部30と、を備え、ゲート接続部30が、複数列のゲート電極10のうち最も端に位置するゲート電極10bよりもゲート長方向の外側に突出する突出部32を有することを特徴とする半導体装置100。

(もっと読む)

SOI基板を用いた半導体装置およびその製造方法

【課題】信号処理回路や大電力回路のような様々な回路を混載する場合にも1チップで対応でき、かつ、SOI層の厚膜化を抑制できる構造の半導体装置を提供する。

【解決手段】SOI基板4を用い、SOI層1を小電力回路部R1とし、支持層2を大電力回路部R2とする。このため、SOI層1の膜厚を小電力回路部R1を考慮した厚みにすれば良く、大電力回路部R2の耐圧等を考慮した厚みにしなくても良い。したがって、厚いSOI層内にウェル層を形成した場合のようなウェル層の境界部を無くすことが可能となり、寄生容量を無くせると共に、寄生容量に起因する消費電力の増大や演算速度の低下を防止することが可能となる。一方、大電力回路部R2を十分な厚みを有する支持層2に形成しているため、耐圧等も確保することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】微細であり、かつ欠陥の少ない素子分離絶縁膜を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置APは、シリコン基板SBと、熱酸化膜SIと、エピタキシャル膜EFとを有している。シリコン基板SBは第2の主面P2を有している。第2の主面P2に底面RCおよび側面SWを有する凹部が設けられている。熱酸化膜SIは凹部の側面SWを覆っている。エピタキシャル膜EFは、側面SWが熱酸化膜SIで覆われた凹部を第2の主面P2の高さまで埋めるように、底面RCからエピタキシャル成長している。

(もっと読む)

CMOS素子及びその製造方法

【課題】CMOS素子及びその製造方法を提供する。

【解決手段】基板上に形成されたエピ層と、エピ層のそれぞれ異なる領域上に形成された第1及び第2半導体層と、第1及び第2半導体層上にそれぞれ形成されたPMOS及びNMOSトランジスタと、を備えるCMOS素子である。

(もっと読む)

半導体装置

【課題】十分な放電能力を有するESD保護素子を備えた半導体装置を提供する。

【解決手段】基板130上にESD保護素子100を備えた半導体装置であって、ESD保護素子100は、基板130内に形成されたp型ウェル領域101と、p型ウェル領域101に形成された素子分離領域109と、素子分離領域109で取り囲まれた活性領域140上に形成されたn型ESD保護トランジスタ120と、p型ウェル領域101上に形成され、素子分離領域109を挟んで活性領域140を取り囲むp型ガードリング領域106と、p型ウェル領域101上に形成され、活性領域140とp型ガードリング領域106との間に形成されたn型カソード領域107とを備えている。n型カソード領域107と活性領域140との間には素子分離領域109が形成されている。

(もっと読む)

金属ゲート及び高K誘電体を有する回路構造体

【課題】 高k材料含有ゲート誘電体及び金属含有ゲートを有する回路構造体を提供する。

【解決手段】 高k誘電体のゲート絶縁体及び金属含有ゲートを有するPFETデバイス及びNFETデバイスを備えたFETデバイス構造体が、開示される。両方のNFETデバイス及びPFETデバイスにおけるゲート金属層が、単一の共通の金属層から製造された。単一の共通の金属であるために、デバイスの製造が簡単化され、必要とされるマスクの数が減少する。両方の型のデバイスのゲートのために単一の金属層を用いるさらなる結果として、PFET及びNFETの端子電極を、直接物理的に接触した状態で互いに付き合わせることができる。共通の金属材料を選択すること及び高k誘電体の酸素曝露によって、デバイスの閾値電圧が調整される。閾値は、低消費電力のデバイス動作を目的としている。

(もっと読む)

デュアルメタルゲート構造の形成方法

半導体構造(10)の形成方法は、第1および第2ウェル領域(16、18)を含む半導体層上にチャネル領域層(40)を形成すること、チャネル領域層上に保護層(80)を形成すること、第1ウェル領域上に第1ゲート誘電体層(26)を形成すること、第1ゲート誘電体上に第1メタルゲート電極層(28)を形成すること、保護層を除去すること、チャネル領域層上に第2ゲート誘電体層(42)を形成すること、第2ゲート誘電体層上に第2メタルゲート電極層を形成すること、第1ウェル領域上に、第1ゲート誘電体層と第1メタルゲート電極層の各々の一部を含む第1ゲートスタック(58)を形成し、チャネル領域層上に、第2ゲート誘電体層と第2メタルゲート電極層の各々の一部を含む第2ゲートスタック(66)を形成することを含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】3次元トランジスタでメモリセルを構成する際に問題となるチャネル部のフローティングを防止でき、高集積化可能な半導体装置及びその製造方法を提供することを目的とする。

【解決手段】第1基柱2にチャネル部5と、チャネル部5の上下に形成された拡散層6,7と、チャネル部5の周りにゲート絶縁膜を介して形成されたゲート電極8とを備えた3次元トランジスタ1が、導電型の第2基柱3を囲むようにウェル領域上に複数配置され、複数個の3次元トランジスタ1が1つの第2基柱3を共有して、各々のチャネル部5がチャネル連結部4によって第2基柱3に接続されていることを特徴とする。また、6個からなる3次元トランジスタ1が、1個の第2基柱3を共有することができる。

(もっと読む)

集積回路のためのCDMESD保護

【課題】改良された静電放電(ESD)保護回路、より詳細には、集積回路(IC)の保護回路におけるデバイス帯電モデル(CDM)ストレスの場合に対する改良を提供すること。

【解決手段】本発明は、集積回路(IC)のためのデバイス帯電モデル(CDM)静電放電(ESD)保護回路を提供する。ESD保護回路は、第1の導電タイプの基板と、基板上の第1のウェルに形成され、パッドに結合された第2の導電タイプのMOS構成部分と、第1のウェルと基板を隔離するための第1のウェルと基板との間に形成された第2の導電タイプを有する隔離ウェル/領域と、を含む。加えて、回路は、隔離されたウェル/領域に結合されたESDクランプを含む。通常電力の動作中、ESDクランプは開放されている。CDM ESD事象中、基板およびMOS構成部分内に蓄積されたCDM電荷は、ICへの損傷を防止するためにESDクランプにより取り除かれる。

(もっと読む)

41 - 60 / 103

[ Back to top ]