Fターム[5F048CB03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 3次元MOSIC(BiMOSを含む) (767) | 積層型MOSIC(2層) (366) | 層間コンタクト (110)

Fターム[5F048CB03]に分類される特許

81 - 100 / 110

ホットエレクトロントランジスタおよびそれを含む半導体装置

【課題】期待される高周波特性を得ること、ならびに後続の回路で必要とされる駆動電流を得ることが可能なホットエレクトロントランジスタを提供する。

【解決手段】このホットエレクトロントランジスタ100は、コレクタ層3と、ベース層5と、エミッタ層7と、コレクタ層3とベース層5との間に形成されたコレクタバリア層4と、ベース層5とエミッタ層7との間に形成されたエミッタバリア層6とを備えている。そして、エミッタバリア層6とエミッタ層7との間のエネルギー障壁は実質的に存在しないとともに、コレクタバリア層4のエネルギー障壁の高さはエミッタバリア層6のエネルギー障壁の高さよりも低い。

(もっと読む)

半導体装置及びその製造方法並びに液晶表示装置

【課題】段差部の凹角部分における配線層の断線を防止する。

【解決手段】アクティブマトリクス基板42は、ガラス基板22と、ガラス基板22に突出した状態で設けられたドライバ部50と、ドライバ部50の表面とガラス基板22の表面とに沿って形成された段差部53と、段差部53の表面に設けられ、段差部53における少なくとも一部の凹角形状を補償する絶縁性の凹角補償膜54と、凹角補償膜54の表面に沿って形成されると共にドライバ部50に接続された配線層37とを備えている。

(もっと読む)

半導体装置及びその製造方法並びに液晶表示装置

【課題】ベースコート層が除去されて露出したガラス基板22の表面に対し、ドライバ部50を確実に貼り合わせる。

【解決手段】半導体装置の製造方法は、ガラス基板22からTEOS層32をエッチングして、SiN層31を部分的に露出させる第1エッチング工程と、第1エッチング工程とは別個独立に行われ、露出したSiN層31をウェットエッチングして、ガラス基板22を部分的に露出させる第2エッチング工程と、露出したガラス基板22に対し、ドライバ部50を貼り合わせる貼り合わせ工程とを備える。

(もっと読む)

積層型半導体集積装置

【課題】素子形成された複数の半導体層を積層し、集積可能な素子数を飛躍的に高めることができる積層型半導体集積装置を提供する。

【解決手段】本発明に係る積層型半導体集積装置は、基板上に直接、または緩衝層を介して積層されたGaN層と、前記GaN層の表面近傍に形成された複数のトランジスタと、前記トランジスタの表面及び側面を被覆する酸化膜または窒化膜と、前記酸化膜または窒化膜を含む前記GaN層上に、ELOによって積層されたAlGaN層と、を集積すべきトランジスタの数量に応じて繰り返し積層して形成される。

(もっと読む)

チャンネル膜を有する半導体装置の製造方法

【課題】 結晶欠陥が小さくかつ表面粗さの特性が良好なチャンネル膜を有する半導体装置の製造方法を提供する。

【解決手段】 チャンネル膜を有する半導体装置の製造方法は、チャンネルシリコン膜を形成するために、まず単結晶シリコン基板100上に、上部表面から延長して突出した部位を含む第1単結晶シリコン膜110を形成する。第1単結晶シリコン膜110の上部表面に犠牲膜112を形成する。第1単結晶シリコン膜110の前記突出した部位及び犠牲膜112の一部が除去されるように第1単結晶シリコン膜110及び犠牲膜112を1次研磨して第2単結晶シリコン膜及び犠牲膜パターンを形成する。前記犠牲膜パターンを除去し、前記第2単結晶シリコン膜を研磨してチャンネルシリコン膜を形成する。前記工程によると、単結晶シリコン膜の研磨厚さを減少させることができ、チャンネルシリコン膜は表面粗さの特性が良好であり、厚さが平坦となる。

(もっと読む)

絶縁ゲイト型半導体装置

【課題】短チャネル効果を抑制しつつチャネル長の短い微細な絶縁ゲイト型半導体装置を実現する。

【解決手段】絶縁ゲイト型半導体装置はフィールド酸化膜によって素子分離されたNチャネル型FET及びPチャネル型FETを有し、各FETはソース領域、ドレイン領域、チャネル形成領域と、ポリシリコンでなるゲイト電極と、窒化シリコンでなるサイドウォールと、熱酸化膜でなるゲイト絶縁膜と、一端がフィールと酸化膜に揃い、他端がサイドウォールに揃った第1のシリサイドと、端部がサイドウォールの揃った第2のシリサイドと、を有し、チャネル形成領域はドレイン領域側からチャネル形成領域側へと広がる空乏層が抑止された領域を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体製造工程で加わる熱履歴の違いに因り、不純物の拡散具合が異なることから、薄膜トランジスタの閾値にばらつきを生じた。これを低減、防止する対策を施した薄膜トランジスタを有する半導体装置及びその製造方法を提供する。

【解決手段】薄膜トランジスタは、絶縁体層を介して半導体基板上に形成された、不純物を含むソース/ドレイン領域と、前記ソース/ドレイン領域間を充填する絶縁体と、前記ソース/ドレイン領域上に形成された不純物拡散制御膜層と、前記不純物拡散制御膜上に形成されたチャネル層と、前記チャネル層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記チャネル層、ゲート絶縁膜及びゲート電極を充填する層間膜とを具備する。前記不純物拡散制御膜は、熱の加わらない製造工程の段階になって、前記ソース/ドレイン領域とチャネル層との間に所定の電圧を印加することにより絶縁破壊される。

(もっと読む)

薄膜トランジスターおよび薄膜トランジスターの作製方法

【課題】ディスプレイの表示品質を向上させることが可能な薄膜トランジスターを実現すること。

【解決手段】基板と、有機材料又はポリマー材料によって構成されたソース領域及びドレイン領域を含む薄膜トランジスターにおいて、各々の領域は、複数の横方向に延在する区画によって1つの端部で結合される複数の縦方向に延在する区画として形成され、前記ソース領域の縦方向に延在する区画はドレイン領域の縦方向に延在する区画と互いに組み合わされて間隔を置き、それによりソース領域とドレイン領域との間に蛇行形状の間隔を生じ、チャンネル領域を含む薄膜トランジスターは前記間隔の幅に等しいチャンネル長さ、及び前記蛇行形状の間隔の長さに延在するチャンネル幅を有する。

(もっと読む)

半導体集積回路及びその作製方法、並びに半導体集積回路を用いた半導体装置

【課題】半導体基板にスルーホールを形成する工程や、半導体基板を裏面から研磨する工程は、非常に長い時間を要し生産性を低下させる要因となる。また、半導体基板を積層する構造であるため、積層して形成された半導体集積回路は厚くなり機械的な柔軟性に劣っている。

【解決手段】複数の基板上に剥離層を形成し、剥離層上に半導体素子、および貫通配線のための開口部を形成する。そして、半導体素子を有する層を基板から剥離し、重ね合わせて積層し、開口部に導電性を有する層を形成して貫通配線を形成することによって半導体集積回路を作製する。

(もっと読む)

半導体装置及びその製造方法

【課題】 STIを形成することなく素子間の分離を可能にし、高密度に集積化できる半導体装置及びその製造方法を提供する。

【解決手段】 シリコン基板表面に段差を設けて、互いに異なる表面を形成し、各表面にトランジスタを形成し、トランジスタ間をシリコン層と絶縁性のサイドウォールとによって絶縁分離する。STIを設けていないため、トランジスタを高密度に集積できる。

(もっと読む)

バルクシリコン上に1T−DRAMを製造するための方法

【課題】絶縁膜上に形成する1T−DRAMを提供する。

【解決手段】 集積回路は、バルクシリコン層及びバルクシリコン層の上に製造された相補型MOSFET(CMOS)トランジスタを有するバルク技術集積回路(バルクIC)を備えている。この集積回路はまた、バルクICに隣接して設けられ且つ一体化された単一トランジスタのダイナミックランダムアクセスメモリ(1T−DRAM)セル212を備えている。

(もっと読む)

半導体装置、集積回路、及び電子機器

【課題】複数のデバイス層を積層配置してなる半導体装置におけるデバイス層間の接続構造をチップ面積の増大や製造工程の複雑化を招くことなく実現し、好ましくは前記層間接続の信頼性の向上も実現した半導体装置を提供する。

【解決手段】デバイス層101,102が積層され、第2のデバイス層102は、表面に複数の微細孔G1を有する起点部層211と、起点部層211を起点として形成された略単結晶粒を含む半導体膜を用いて形成されたトランジスタQ12(デバイス)を有するデバイス形成層212とを備えており、トランジスタQ12等を構成する結晶化半導体膜201,202の側端面に絶縁材料からなるサイドウォール201s、202sが設けられており、トランジスタ(デバイス)Q11とトランジスタQ12とを接続するコンタクト部C5は、結晶化半導体膜201,202の間の領域に形成されている。

(もっと読む)

シリコン−ゲルマニウム立体構造CMOS上の局所配線の製造方法

【課題】シリコン−ゲルマニウム立体構造CMOSにおいて、シリコンCMOS素子とゲルマニウムCMOS素子との間の局所配線を容易に形成する。

【解決手段】シリコンCMOS素子を有するシリコン基板を準備し(12)、該素子の上部に絶縁層を形成する(14)。上記絶縁層を部分的に開口し(16)、その上にゲルマニウム薄膜を形成する(18)。アニール処理により、上記薄膜のゲルマニウムを流動化する(24)。これにより、開口部に上記ゲルマニウムが流れ込み、該ゲルマニウムと上記シリコン基板および上記シリコンCMOS素子との間に接点が形成される。さらに冷却することで、上記ゲルマニウムがLPE成長により結晶化される(26)。そして、単結晶のゲルマニウム上にゲルマニウムCMOS素子を形成する。

(もっと読む)

半導体装置、集積回路、及び電子機器

【課題】起点部より成長させてなる結晶粒を有する半導体膜を用いたデバイスを3次元配置してなり、いずれの層に配置されたデバイスにおいても所望のデバイス特性を得ることができる半導体装置、及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、表面に複数の微細孔G11,G12を有する起点部層211と、前記微細孔G11,G12を起点として形成された略単結晶粒を含む半導体膜201,202を用いて形成されたデバイス形成層212とを備えたデバイス層101上に、同様の構成を具備したデバイス層102,103を積層してなり、前記デバイス層101〜103に属する前記微細孔(例えば微細孔G21)は、隣接して配置された他の前記デバイス層101〜103に属する前記微細孔(例えば微細孔G11,G31)から平面視で離間した位置に形成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】チップ面積及び製造コストの増大を抑制しつつ、レーザ照射用の冗長回路を備えた半導体装置及びその製造方法を提供する。

【解決手段】基板上に第1の能動層として、本来の機能を有する回路を形成する工程と、前記第1の能動層に絶縁層を形成する工程と、前記絶縁層上に、微細孔を形成する工程と、前記微細孔が形成された絶縁層上に半導体層を形成する工程と、前記半導体層に対してレーザ照射による熱処理を行うことで、前記微細孔を起点として略単結晶化された結晶粒を形成する工程と、前記略単結晶化された結晶粒を用いて第2の能動層としてのレーザリペア用の冗長回路を形成する工程とを有する。

(もっと読む)

半導体装置

【課題】半導体チップに複数の半導体素子が形成されている半導体装置において、従来の半導体装置と比較して、半導体チップの面積を縮小できる半導体装置を提供する。

【解決手段】半導体チップの表面に平行な面方向において、パワー素子領域aよりも領域が狭い制御回路素子領域bがパワー素子領域aと完全に重複するように、半導体チップの内部に、絶縁分離されたパワー素子領域aを有する第1のSOI層4と、絶縁分離された制御回路素子領域bを有する第2のSOI層7とを、半導体チップの表面に垂直な方向に並んで配置させる。

(もっと読む)

半導体装置の製造方法、半導体装置およびウエハ

【課題】 ウエハの薄型化に際して生じる問題を回避し、積層ウエハ間の電気的接続のための工程を短縮できる方法を提供する。

【解決手段】 基板1SAにその主面から所望の深さまで延びる深い分離溝5aを形成した後、深い分離溝5a内に絶縁膜5bを埋め込み貫通分離部5を形成する。続いて、基板1SAの主面にMOS・FET6を形成した後、基板1SAの主面上に層間絶縁膜8aを堆積する。その後、貫通分離部5で囲まれた領域内に、層間絶縁膜8aの上面から基板1SAの厚さの途中深さまで延びる深い導通溝9aを形成する。続いて、深い導通溝9a内に導体膜9bを埋め込み貫通配線部9を形成する。その後、基板1SAの裏面を、貫通分離部5および貫通配線部9が露出しない程度まで研削および研磨した後、貫通分離部5および貫通配線部9の下部の一部が露出する程度までウエットエッチング処理する。

(もっと読む)

フィンFETCMOSとその製造方法及びそれを備えるメモリ素子

【課題】フィンFETCMOSとその製造方法及びそれを備えるメモリ素子を提供する。

【解決手段】基板上に備えられたn型トランジスタ、n型トランジスタ上に積層された層間絶縁層、及び層間絶縁層上に備えられたp型トランジスタ、を備えるが、n型及びp型トランジスタは、共通のゲート絶縁膜とフィンゲートとを有することを特徴とするCMOS素子である。

(もっと読む)

3次元半導体集積回路装置の製造方法および3次元半導体集積回路装置

【課題】開発期間を短縮でき、製造コストを低減でき、しかも、回路特性を安定化させることができ、さらに、製造工程を簡略化でき、集積回路の損傷を防ぐことができる3次元半導体集積回路装置の製造方法および3次元半導体集積回路装置を提供する。

【解決手段】第1の半導体基板とこの第1の半導体基板に形成された第1の半導体集積回路とを有する第1の半導体集積回路基板10上に、絶縁膜15を介して非晶質シリコン層を形成する。非晶質シリコン層の複数の部分を選択的に再結晶化して、複数の再結晶化領域34を含む多結晶シリコン層31を形成する。複数の再結晶化領域34と所定の位置関係を持つように、多結晶シリコン層31に第2の半導体集積回路を形成して、多結晶シリコン層31と第2の半導体集積回路とを有する第2の半導体集積回路基板30を作製する。

(もっと読む)

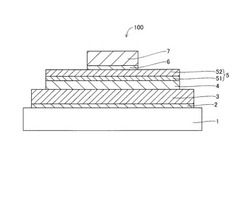

薄膜トランジスタ回路とその製造方法

【課題】本発明は、単位面積当たりの集積度の高いCMOS構造薄膜トランジスタ回路及びその製造方法を提供する。

【解決手段】本願発明は、基板(2)上に配置された第1の半導体層(4)と、前記第1の半導体層上(4)に第1のゲート絶縁層(5)を介して配置されたゲート電極(6)と、前記ゲート電極(6)上に第2のゲート絶縁層(7)を介して配置された第2の半導体層(8)を備え、前記第2の半導体層(8)のソース領域(8s)及びドレイン領域(8d)が、前記第1の半導体層(4)のソース領域(4s)及びドレイン領域(8d)と重なるように構成された積層型薄膜トランジスタ回路に関し、特に平面表示装置に用いられた場合に、面積として従来比70%以下の狭小化が達成できる。

(もっと読む)

81 - 100 / 110

[ Back to top ]