Fターム[5F048CB03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 3次元MOSIC(BiMOSを含む) (767) | 積層型MOSIC(2層) (366) | 層間コンタクト (110)

Fターム[5F048CB03]に分類される特許

61 - 80 / 110

半導体装置

【課題】微細化が進んだ半導体装置の短チャネル効果を防ぎ、特性を向上させることができる半導体装置の提供を課題とする。

【解決手段】単結晶シリコン基板上に形成された酸化膜と、酸化膜上に形成された単結晶シリコン層と、単結晶シリコン層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極を有する半導体装置であって、単結晶シリコン層はチャネル形成領域、ソース領域、ドレイン領域を有し、チャネル形成領域には、ソース領域、ドレイン領域とは逆の導電型の不純物元素が添加され、チャネル形成領域の不純物元素が添加された領域は、上面から見て主軸がソース領域からドレイン領域にかけて伸びるフィッシュボーン形状を有し、フィッシュボーン形状は単結晶シリコン層の表面から底部にかけて形成され、チャネル形成領域の不純物元素が添加された領域は、空乏層を抑止する機能を有することを特徴としている半導体装置を提供する。

(もっと読む)

基板上にチップを移動する方法

【課題】本発明の課題は、部品がウエハ上に移動されることができる新規な方法を見出すことである。

【解決手段】本発明は、少なくとも2つの回路のステージの積層体を形成する方法であって、各々のステージが、基板と、この基板内または基板上に形成された少なくとも1つの部品(10、20)及び金属接続とを含み、前記ステージの組立体が前のステージ上に移動される方法であって、(a)弱体化領域(30)を形成するように、前記部品(10、20)の少なくとも一部を介した、移動される前記ステージの基板(2、25)内におけるイオン注入(29)と、(b)前記部品の金属接続の形成と、(c)前記前のステージへの、この基板の部分の移動及び組立と、(d)前記弱体化領域(30)に沿った破砕による、前記基板の移動される部分を薄くする段階と、を含む方法に関連する。

(もっと読む)

基板上に積層され自己整合された部品の製造方法

【課題】基板上に積層され自己整合された部品の製造方法を提供する。

【解決手段】基板の一表面に層の積層体を形成する段階であって、積層体が第1犠牲層、第2犠牲層及び表面層を備える段階と、第1犠牲層の一領域をエッチングする段階と、第1犠牲層のエッチングされた領域内及び表面層上に樹脂を堆積する段階と、犠牲層上の樹脂の少なくとも1つの領域に位置合わせされる樹脂の少なくとも1つの領域を第1犠牲層のエッチングされた領域に残すために樹脂をリソグラフィする段階と、第1犠牲層のエッチングされた領域内及び犠牲層上の除去された樹脂を残っている樹脂を制限するための材料で置換する段階と、第1犠牲層のエッチングされた領域内及び表面層上の残っている樹脂の領域を除去して部品の製造に対する専用の領域を提供する段階と、専用の領域内に部品の要素を形成する段階と、第2犠牲層の一領域を選択的にエッチングする段階と、を備える。

(もっと読む)

半導体装置の作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子及び第1の電極上に絶縁膜を形成し、絶縁膜中に第1の加速電圧で第1のイオンを添加して、絶縁膜中の第1の深さに第1の欠陥の多い領域を形成し、第1の加速電圧とは異なる第2の加速電圧で、第2のイオンを添加して、絶縁膜中の第1の深さとは異なる第2の深さに第2の欠陥の多い領域を形成し、第1及び第2の欠陥の多い領域上に、金属元素を含む導電材料を形成し、第1及び第2の欠陥の多い領域のうちの上方の領域から下方の領域に、金属元素を拡散させることにより、絶縁膜中に、第1の電極と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

3−D積層型デバイスのESD保護を可能にするシステム及び方法

【解決手段】静電気放電(ESD)保護デバイスが、積層型半導体ダイのアクティブレイヤ間の縦型の空間に形成され、これにより、そうでなければ通信目的のためにしか使用されないであろう空間を利用する。シリコン貫通ビア(TSV:through silicon via)の縦型の表面領域は、ESDイベントに起因する大電圧を緩和するために使用される。一実施形態では、ESDダイオードは、積層型デバイスの半導体ダイのアクティブレイヤ間の縦型TSV内に形成される。このESDダイオードは、積層の半導体ダイの両方の上の回路によって共有され、これによって空間を節約し、そしてESD保護回路によって必要とされるダイ面積を低減し得る。 (もっと読む)

動的に調整可能な閾値電圧を有する3次元集積トランジスタの回路

【課題】低減された集積度および低消費電力の基準を満たすと同時に、電気的性能の改良をもたらす、多重構造トランジスタを有する新規なデバイスを提供する。

【解決手段】積層の所定レベルに位置する第1トランジスタT11と、所定レベルの上方の積層の第2レベルに位置する第2トランジスタT21とを備え、第1トランジスタは第2トランジスタのチャネル区域116に対向するゲート電極108を備え、第1トランジスタと第2トランジスタとは絶縁区域120により分離され、この絶縁区域は第1トランジスタのゲートと第2トランジスタのチャネルとの間の第1領域R1にて第1トランジスタのゲートと第2トランジスタのチャネルとの間の結合を可能にするように規定された組成および厚さを有し、この絶縁区域は、第1トランジスタおよび第2トランジスタのアクセス区域の間の第1領域の周囲に、第1領域とは異なる組成および厚さを有する第2領域R2を備える。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置、および電子機器

【課題】三次元半導体装置における特性を向上させることができる製造方法および装置構成を提供する。

【解決手段】第1半導体膜(9)上にカーボンナノチューブを備えるプラグ電極(15)を形成する工程、形成されたプラグ電極(15)の周囲に層間絶縁膜(16,18)を形成する工程、層間絶縁膜の表面を平滑化してプラグ電極(15)の頂部を露出させる工程、層間絶縁膜およびプラグ電極の頂部上に非晶質の第2半導体膜を形成する工程、非晶質の第2半導体膜にエネルギーを供給して露出したプラグ電極(15)を触媒として機能させて非晶質の第2半導体膜を結晶化させ結晶化した第2半導体膜(23)とする工程を備える。

(もっと読む)

半導体装置、半導体装置の作製方法

【課題】支持基板上に、単結晶半導体層を多層構造とした、多層集積回路を形成する場合の、工程数の簡略化を図る。また同歩留まりの向上を図る。

【解決手段】基板面内の半導体素子の半導体接合界面領域は、支持基板側から、すなわち基板の素子が形成されていない面からレーザを直接照射し加熱することができるよう配置される。1層目の半導体素子層、2層目の半導体素子層が形成された後、支持基板側からレーザを照射することで、1層目の半導体素子層及び2層目の半導体素子層の、半導体接合界面領域の活性化を同時に行う。支持基板と前記半導体素子層との間の層は光透過性とし、レーザを減衰しない構造とする。

(もっと読む)

半導体装置およびその製造方法

【課題】被測定体の表面形状を取得する半導体装置において、表面形状の高解像度化を図る。

【解決手段】被測定体60と各電極28、37との間の静電容量を検出するための各素子29、38が設けられた第1容量検出回路層20および第2容量検出回路層30を積層にし、各素子29、38の各電極28、37を各トレンチ26、35によって保護膜50まで引き伸ばす。これにより、容量検出回路層が一層の場合よりも一定面積当たりに配置できる素子29、38を増加させ、被測定体60の表面形状を高解像度で検出する。

(もっと読む)

半導体装置およびその製造方法

【課題】高密度に搭載可能な構造を有する電界効果トランジスタを備えた半導体装置を提供する。

【解決手段】基板と、この基板上に設けられた第1の絶縁層と、第1の絶縁層に埋め込まれた導電層と、この導電層に電気的に接続し直上に配置された下部拡散層、この下部拡散層上の半導体層、及びこの半導体層上の上部拡散層を有する柱状半導体部と、前記半導体層の周囲側面に設けられたゲート絶縁膜と、このゲート絶縁膜上に設けられたゲート電極と、このゲート電極および前記柱状半導体部を埋め込むように設けられた第2の絶縁層を有する半導体装置。

(もっと読む)

半導体装置

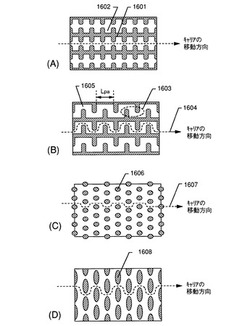

【課題】SOI構造を有する半導体装置において、高性能化、低消費電力化を目的の一とする。また、より高集積化された高性能な半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に複数の電界効果トランジスタがそれぞれ層間絶縁層を介して積層している半導体装置とする。複数の電界効果トランジスタの有する半導体層は半導体基板より分離されており、該半導体層は絶縁表面を有する基板、又は層間絶縁層上にそれぞれ設けられた絶縁層に接して接合されている。複数の電界効果トランジスタはそれぞれ前記半導体層に歪みを与える絶縁膜で覆われている。

(もっと読む)

半導体装置

【課題】SOI構造を有する半導体装置において、高性能化、低消費電力化を目的の一とする。また、より高集積化された高性能な半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上にnチャネル型及びpチャネル型電界効果トランジスタがそれぞれ層間絶縁層を介して積層している半導体装置とする。nチャネル型及びpチャネル型電界効果トランジスタの有する半導体層は半導体基板より分離されており、該半導体層は絶縁表面を有する基板、又は層間絶縁層上にそれぞれ設けられた絶縁層に接して接合されている。応力を有する絶縁膜によって半導体層へ与えられる歪み、半導体層の面方位、又はチャネル長方向の結晶軸を制御することによって、nチャネル型とpチャネル型電界効果トランジスタとの移動度の差を軽減し、電流駆動能力及び応答速度を同等とする。

(もっと読む)

表示装置

【課題】表示装置の画素を構成する電界効果トランジスタの高性能化を実現し、且つ電界効果トランジスタの微細加工技術に依拠することなく、画素内の電界効果トランジスタ数を増やしても電界効果トランジスタ数の増加に伴い低下した画素の開口率を向上及び画素に占める電界効果トランジスタの面積の削減を図ることのできる表示装置を提供することを目的の一とする。

【解決手段】半導体基板より分離され、絶縁表面を有する支持基板に接合された半導体層を有する電界効果トランジスタが、平坦化層を層間に設けて複数積層された画素を複数具備する表示装置とする。

(もっと読む)

半導体装置

【課題】SOI構造を有する半導体装置において、高性能化、低消費電力化を目的の一とする。また、より高集積化された高性能な半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に複数の電界効果トランジスタがそれぞれ平坦化層を介して積層しており、複数の電界効果トランジスタの有する半導体層は半導体基板より分離されており、該半導体層は絶縁表面を有する基板、又は平坦化層上にそれぞれ設けられた絶縁層に接して接合されている半導体装置とする。

(もっと読む)

半導体装置、電子機器、半導体装置の作製方法

【課題】半導体装置の高集積化及び微細化に関する問題点を解決することを課題とする。また、上記の問題点を、低コストにて解決することを課題とする。

【解決手段】絶縁表面を有する基板上に第1の単結晶半導体層を形成し、第1の単結晶半導体層上に第2の絶縁層を形成し、第2の絶縁層上の第1の単結晶半導体層の一部と重なる領域に導電層を形成し、第2の絶縁層及び導電層を覆うように第3の絶縁層を形成し、第3の絶縁層の上面を平坦化し、第3の絶縁層上に第4の絶縁層を形成し、第2の損傷領域を有する第2の単結晶半導体基板の表面と、第4の絶縁層とを貼り合わせ、第2の単結晶半導体基板を、第2の損傷領域において分離して、絶縁表面を有する基板上に第2の単結晶半導体層を形成する。

(もっと読む)

半導体装置

【課題】所要電流の異なる複数の負荷の駆動に対しても、スイッチング速度の劣化やスイッチング損失の増大を伴わず、最適に対応することのできる半導体装置を提供する。

【解決手段】スイッチング電源を構成するスイッチング素子が、許容電流の異なる複数個のパワー素子P1〜P3に分割されてなり、パワー素子P1〜P3の第1電流端子が、共通する電源端子Dに接続され、パワー素子P1〜P3の第2電流端子が、共通する出力端子Tに接続され、パワー素子P1〜P3の各ゲート端子が、トランジスタからなるスイッチS1〜S3を介して、共通するゲート信号端子Gに接続されてなり、パワー素子P1〜P3とスイッチS1〜S3とで構成される出力回路部K1が、一つの第1半導体チップ10に形成されてなり、パワー素子P1〜P3が、スイッチS1〜S3により切り替えられて用いられる半導体装置100とする。

(もっと読む)

半導体装置

【課題】基板上にCMISFETを備えた半導体装置において、Global Strainによる応力印加を有効に活用しつつ、回路のスイッチ動作速度の低下を生じさせない半導体装置を提供する。

【解決手段】基板の一方の面に形成される第1の素子領域と、基板の他方の面に形成される第2の素子領域と、第1の素子領域と第2の素子領域との間の、比誘電率が3.9よりも低い絶縁層とを備え、第1の素子領域にn型MISFETが形成され、第2の素子領域にp型MISFETが形成され、絶縁層中を貫通する配線によって、第1の素子領域と第2の素子領域とが電気的に接続され、第1の素子領域が形成される面が凸形状、第2の素子領域が形成される面が凹形状となるように基板が湾曲していることを特徴とする半導体装置。

(もっと読む)

三次元構造半導体装置

【課題】チップ面積の増大を防ぎ、チップの動作周波数を高くすることが可能な三次元構造の半導体装置を提供すること。

【解決手段】第1の半導体層に形成された複数の領域と該第1の半導体層の上に形成された第1の配線層とを含んで構成された第1の集積回路と、前記第1の配線層に積層された第1の絶縁層と、前記第1の絶縁層に積層された第2の半導体層に形成された複数の領域と該第2の半導体層の上に形成された第2の配線層とを含んで構成された第2の集積回路とを含む3次元構造半導体装置をなす。前記第1の集積回路及び前記第2の集積回路は積層方向に貫通した配線により電気的に接続され、前記第1の集積回路及び前記第2の集積回路間のデータ双方向通信、制御信号供給、およびクロック信号供給の少なくとも一つが前記貫通した配線を介して行われる。

(もっと読む)

半導体装置及びその製造方法

【課題】シリコン基板よりバンドギャップが大きい基板に、動作電圧が互いに大きく異なる2種類のトランジスタを混載することができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、SiC基板1に形成された第1のトランジスタと、第1のトランジスタ及びSiC基板1の上方に形成された第1の層間絶縁膜11と、第1の層間絶縁膜11上に形成された結晶化シリコン膜20と、結晶化シリコン膜20に形成された第2のトランジスタとを具備する。第1のトランジスタの動作電圧は、例えば100V〜1000Vであり、第2のトランジスタの動作電圧は、例えば3V〜5Vである。

(もっと読む)

半導体装置

【課題】小型の半導体装置を提供する。

【解決手段】半導体装置1において、単結晶シリコンからなる基板2を設け、基板2の表面の素子領域Aに素子3を形成する。素子3は、半導体装置1の本来の機能を果たす機能素子である。また、基板2上に層間絶縁膜4を形成し、層間絶縁膜4上における保護領域Bに多結晶シリコン層5を形成し、多結晶シリコン層5内に素子6を形成する。素子6は素子3を静電気から保護する静電耐圧用保護素子である。更に、層間絶縁膜4上に層間絶縁膜7を形成し、層間絶縁膜7上におけるパッド領域Cにパッド8を設ける。そして、保護領域Bは素子領域Aの直上域近傍に設け、パッド領域Cは素子領域A及び保護領域Bの直上域近傍に設ける。

(もっと読む)

61 - 80 / 110

[ Back to top ]