Fターム[5F048CC10]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 保護回路の構成 (4,292) | バイポーラ、サイリスタ (251)

Fターム[5F048CC10]に分類される特許

1 - 20 / 251

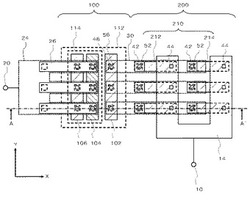

半導体装置

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置に負電流が流れた場合でも、回路素子を構成する深い半導体層の電位に対して、半導体基板の電位が低くなるのを抑制して寄生素子を作動させず、半導体装置の誤動作を防止する。

【解決手段】本発明は、n型の半導体基板3と、半導体基板3の一面に形成し、接続する負荷に電力を供給する電力素子1と、n型のソース・ドレイン領域を有するMOSトランジスタ2cを少なくとも1つ含む回路素子2と、電力素子1および回路素子2に対し独立して配置したp型の半導体層4と、半導体基板3および半導体層4と接続する外部回路とを備えている。外部回路は、電源と、電源に一端を接続する抵抗素子と、抵抗素子の他端にアノード電極を接続し、カソード電極をGND接地するダイオードとを有し、抵抗素子の他端に半導体層4を接続する。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、I/Oセルの高さを低減すると同時に幅の増大を防ぐことでI/Oセルの占める領域の面積を削減すること。

【解決手段】レベルシフタ回路、I/Oロジック回路およびI/Oバッファ回路を含むI/Oセルがコア領域の周囲に配置された半導体集積回路装置であって、I/Oロジック回路が配置されたI/Oロジック領域、および、I/Oバッファ回路が配置されたI/Oバッファ領域は、I/Oセルに対するパッドが配置された領域と重なり合うとともに、コア領域の辺に平行な方向に互いに並んで配置されている。

(もっと読む)

半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、入力電圧ラインと誘導性負荷との間に接続される第1のスイッチング素子と、誘導性負荷と基準電圧ラインとの間に並列接続される第2のスイッチング素子とを備えている。0<(第2のスイッチング素子の閾値電圧)<(第2のスイッチング素子の内蔵ダイオードのオン電圧)である。第2のスイッチング素子のゲート電圧が基準電位の場合に、第1のスイッチング素子と第2のスイッチング素子との接続点の電位が、−(第2のスイッチング素子の閾値電圧)より大きくなると第2のスイッチング素子はオフし、接続点の電位が、−(第2のスイッチング素子の閾値電圧)より小さくなると第2のスイッチング素子はオンする。

(もっと読む)

半導体装置

【課題】静電気放電が印加されたときの熱破壊を抑制すること。

【解決手段】半導体装置1の半導体活性層16には、n型領域23とp型領域26とn型の埋込み領域30が形成されている。n型領域23は、カソード電極Kに電気的に接続している。p型領域26は、アノード電極Aに電気的に接続している。埋込み領域30は、半導体活性層16のうちのp型領域26の裏面側の少なくも一部を含むように形成されており、p型領域26の裏面に接触しているとともに、不純物濃度が半導体活性層16の不純物濃度よりも濃い。

(もっと読む)

半導体装置

【課題】保護素子の異なるクランプ電圧を容易に設定して形成できる構造の保護素子を含む半導体装置を提供すること。

【解決手段】回路内部のMOS型半導体装置のゲート酸化膜を保護するための保護素子を含む半導体装置であって、該保護素子は、該MOS型半導体装置とその前段回路との間に接続される横型バイポーラトランジスタであり、該横型バイポーラトランジスタのパンチスルー耐圧をクランプ電圧として利用することを特徴とする、半導体装置。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

半導体装置及びDC−DCコンバータ

【課題】耐久性が高い半導体装置及びDC−DCコンバータを提供する。

【解決手段】実施形態に係る半導体装置は、高電位側電源電位に接続するための第1の配線と、前記高電位側電源電位に接続するための、前記第1の配線とは別の第2の配線と、前記第1の配線に一端が接続され、他端が出力端子に接続されるスイッチングトランジスタと、前記高電位側電源電位と前記低電位側電源電位との間で前記スイッチングトランジスタと並列に接続される保護素子とを備える。前記保護素子は、前記第1の配線に接続される、第1のp形半導体領域と、前記第2の配線に接続される、前記第1のp形半導体領域に接したn形半導体領域と、前記n形半導体領域に接し、前記第1のp形半導体領域から離隔し、前記低電位側電源電位に接続するための配線に接続される第2のp形半導体領域と、を有する。

(もっと読む)

集積回路

【課題】ESDに対する安定した保護動作を実現する集積回路を提供する。

【解決手段】実施形態によれば、集積回路は、外部電源と接続される第1の外部端子と、第2の外部端子と、接地された第3の外部端子と、出力トランジスタと、ESD保護回路と、ダイオードと、電源回路と、内部回路と、電流源回路と、駆動回路とを備えている。電流源回路は、電源回路の出力ラインと第3の外部端子との間に直列接続されたコンデンサ及び電流源を含む。駆動回路は、コンデンサと電流源との間に接続された第1の入力端子と、内部回路の出力端子と接続された第2の入力端子と、出力トランジスタの制御電極と接続された出力端子とを有する。第2の外部端子に最大定格電圧より大きい電圧が印加すると、駆動回路は出力トランジスタをオフにし、ESD保護回路が動作する。

(もっと読む)

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

集積回路

【課題】ESDに対する安定した保護動作を実現する集積回路を提供する。

【解決手段】実施形態によれば、集積回路は、電源端子と出力端子との間に接続されたハイサイド出力トランジスタと、ハイサイド出力トランジスタの制御電極と第2の電極との間に接続されたトランジスタと、電源端子とトランジスタの制御電極との間に接続されたトリガー回路と、電源端子と出力端子との間に接続されたESD保護回路とを備えている。電源端子に最大定格電圧より大きい電圧が印加すると、トリガー回路が動作し、トランジスタがオンし、ハイサイド出力トランジスタがオフし、ESD保護回路が動作する。

(もっと読む)

過電圧保護回路及び半導体集積回路

【課題】異常な過電圧から内部回路を確実に保護することができる過電圧保護回路を提供する。

【解決手段】過電圧保護回路2Aは、整流素子D10と、互いに並列に接続された第1段から第n段(nは2以上の整数)のスイッチング素子NM1〜NMnとを備える。スイッチング素子NM1〜NMnは、整流素子D10の出力端からの出力電圧が印加される第1から第nの制御端をそれぞれ有する。また、スイッチング素子NM1〜NMnの各々は、第1端子3及び第2端子4にそれぞれ接続された被制御端を有する。整流素子D10は、第1端子3から過電圧が入力されたとき、スイッチング素子NM1〜NMnをオン状態にする制御電圧を出力する。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタとESD保護素子とを有する半導体装置において、製造工程が簡単であるとともに、所望の特性を確保しつつ従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】LDMOSトランジスタ形成領域のゲート電極18aと素子分離膜11bの重なり幅をA1、ゲート電極18aとドレイン領域23bとの間隔をB1とし、ESD保護素子形成領域のゲート電極18と素子分離膜11cとの重なり幅をA2、ゲート電極18bとアノード領域22cとの間隔をB2としたときに、A1≧A2、且つB1<B2の関係を満足するように、ゲート電極18a、素子分離膜11b、ドレイン領域20a、ゲート電極18b、素子分離膜11c及び前記アノード領域22cを形成する

(もっと読む)

保護素子及び保護素子を備えた半導体装置

【課題】比較的小さい面積で形成することができ、かつ、素子サイズの微小化が進んでも保護素子として動作させることを可能にする、保護素子を提供する。

【解決手段】半導体基板1に形成された、第1導電型のウェル領域3と、この第1導電型のウェル領域3に隣接して形成された、第2導電型のウェル領域4と、第1導電型のウェル領域3に形成された、第2導電型チャネルのMOSトランジスタと、第1導電型のウェル領域3とMOSトランジスタのソース領域とMOSトランジスタのゲートとに電気的に接続された第1の配線と、MOSトランジスタのドレイン領域と第2導電型のウェル領域4とに電気的に接続された第2の配線とを含む保護素子を構成する。

(もっと読む)

半導体装置

【課題】ESD保護特性のすぐれたESD保護回路を含む半導体装置を構築することが課題となる。

【解決手段】静電気によるサージ電圧が印加されたときだけオン状態になるように、抵抗素子20と容量素子21で形成されるRCタイマーとPLDMOSトランジスタ5とからなるRCタイマー付き放電部1を形成する。また、NMOSオフトランジスタ10、15のそれぞれのソース電極13とドレイン電極16同士を接続したノイズ発生防止部2を形成する。前記RCタイマー付き放電部1のPLDMOSトランジスタ5のソース電極6を電源ライン3に接続する。また、該PLDMOSトランジスタ5のドレイン電極8と前記NMOSオフトランジスタ10のドレイン電極11とを接続する。NMOSオフトランジスタ15のソース電極18を接地ライン4に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

パワー半導体デバイスおよびその製造方法

【課題】改善されたパワーデバイスに加えてそれらの製造方法,パッケージ化の実施例を提供する。1実施例としては、シールドされたゲートトレンチMOSFETにおいて、多くの電荷調整技術と寄生容量を低減する他の技術とを組み合わせて、改善された電圧性能,速いスイッチング速度および低いオン抵抗を有するパワーデバイスを提供する。

【解決手段】シールドポリ311の上にゲートポリ310を含み、垂直方向電荷制御のために、ゲートトレンチ302より深い位置にある非ゲートトレンチを含み、電荷制御トレンチ301は、トレンチの最上部でソース金属に接続する導電材料の単層を有し得るが、独立してバイアスがかけられ、多重に積み重ねられたポリ電極313を使用する。また、デュアルゲート構造を用いることによってゲートとドレインとの間の容量Cgdを低減する。

(もっと読む)

半導体集積回路

【課題】ESD保護回路の面積を増大させることなく、サージに対する耐性に優れた半導体集積回路を実現する。

【解決手段】半導体集積回路は、互いに隣接する入出力セル1及び入出力セル2間には、アノードが入出力端子3に接続され、且つ、カソードが入出力端子7に接続されたサイリスタ13と、カソードが入出力端子3に接続され、且つ、アノードが入出力端子7に接続されたサイリスタ14とが構成されている。

(もっと読む)

1 - 20 / 251

[ Back to top ]