Fターム[5F048DA23]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 製造方法 (5,886) | ゲート側壁(サイドウォール) (5,329)

Fターム[5F048DA23]の下位に属するFターム

Fターム[5F048DA23]に分類される特許

741 - 759 / 759

半導体装置及びその製造方法

【課題】MOS−FETの駆動力を向上させる高性能な半導体装置及びその製造方法を提供すること。

【解決手段】CMOS−FET回路を備える半導体装置において、NMOS形成領域周辺の素子分離膜(102)の一部に設けられ引張応力を有する引張応力膜(119)と、PMOS形成領域周辺の素子分離膜(102)の一部に設けられ圧縮応力を有する圧縮応力膜(120)と、の少なくとも一方を備えている。

(もっと読む)

基板への相互接続を有する集積回路およびその製造方法

ソース/ドレイン(20)とゲート(26)との間の接点(32)が、ゲート誘電体(46)の選択部分(35)へ埋設物を注入することによりゲート誘電体(46)の選択部分(35)を導電性にすることで行われる。ゲート材料は集積回路全体(10)の上の層に位置する。ゲート(26)がソース/ドレイン(20)に接続する領域(32)が識別され、この識別位置(35)においてゲート誘電体(46)が導電性となるよう埋設物が注入される。ソース/ドレイン(20)が導電性ゲート誘電体(35)のそのような導電性領域の下を延び、該位置で埋設物が注入されたゲート誘電体(35)がゲート(26)をソース/ドレイン(20)に短絡するように、ソース/ドレイン(20)は形成される。これによって集積回路(10)上のスペースが節約され、相互接続層の必要性が低減され、露出したシリコン基板上にポリシリコンを堆積およびエッチングさせることに付随する問題を回避することができる。  (もっと読む)

(もっと読む)

独立して歪むNチャネル型及びPチャネル型トランジスタ

第一ウェハ上に形成された第一の複数のトランジスタと、第二ウェハ上に形成された第二の複数のトランジスタとを備えた集積回路。第一トランジスタのうち少なくとも実質的に大部分が第一導電型であり、第二の複数のトランジスタのうち少なくとも実質的に大部分が第二導電型である。ウェハ同士が結合された後、第二ウェハの一部が除去されて、第二の複数のトランジスタのチャネルの歪みの圧縮性が、第一の複数のトランジスタのチャネルの歪みの圧縮性よりも高くなる。  (もっと読む)

(もっと読む)

半導体装置及びそのような装置を製造する方法

本発明は、基板(11)と、第1及び第2半導体層(2、3)を連続して備える半導体層構造体と第1導電型の表面領域を有するシリコンの半導体本体(1)とを備え、表面領域には第1導電型と逆の第2導電型のチャネルを有する電界効果トランジスタ(M)が設けられ、表面領域は、電界効果トランジスタ(M)のための第2導電型のソース及びドレイン領域(4A、4B)と、第2半導体層(3)の一部分を形成する、前記ソース及びドレイン領域間に挿入されたより低いドーピング濃度を有するチャネル領域(3A)と、チャネル領域(3A)の下に埋め込まれ、チャネル領域(3A)のものよりはるかに高いドーピング濃度を有し、第1半導体層(2)の一部分を形成する第1導電型の埋め込み半導体領域(2A)とが設けられる、半導体装置(10)に関する。本発明によれば、半導体本体(1)には、電界効果トランジスタ(M)だけでなく、それぞれ第2、第1及び第2導電型のエミッタ、ベース及びコレクタ領域(5A、5B、5C)を有するバイポーラ・トランジスタ(B)も設けられ、エミッタ領域(5A)は第2半導体層(3)内に形成され、ベース領域(5B)は第1半導体層(2)内に形成される。このようにして、高周波用途に非常に適した、本発明による方法を使用して製造するのが容易なBi(C)MOS IC(10)が得られる。好ましくは、第1半導体層(2)はSi−Geを備えデルタドープされるが、第2半導体層(3)はひずみSiを備える。  (もっと読む)

(もっと読む)

平面デュアルゲート半導体装置

デュアルゲート半導体装置の製造方法は、シリコン体(16)の第1の表面(14)の一部分上に第1のゲート(12)が形成された後であるが、前記第1の表面の反対側のシリコン体の第2の表面(44)上に第2のゲート(52)を形成する前に行われるソース及びドレインコンタクト領域(34,36)のシリサイド化を備える。第1のゲート(12)はソース及びドレインコンタクト領域がシリコンチャネル(18)に位置合わせされることを保証するマスクの働きをする。さらに、製造の早い段階でシリサイド化を行うことにより、第2のゲートの材料の選択が高温処理により制限されない。シリサイド化によるシリコン体の第2の表面での材料特性の違いがシリサイドのソースコンタクト領域とドレインコンタクト領域との間に前記第2のゲートを横方向に位置合わせされることを可能にすることが有利である。  (もっと読む)

(もっと読む)

2種類の金属酸化物ゲート誘電体に1種類の金属ゲート電極が設けられる半導体プロセス及び集積回路

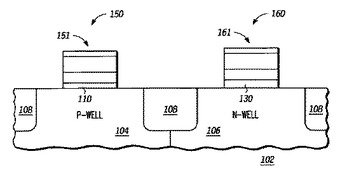

半導体形成プロセスでは、第1及び第2トランジスタを第1及び第2ウェル領域のそれぞれの上に形成し、第1トランジスタは第1ゲート誘電体を有し、そして第2トランジスタは第1ゲート誘電体とは異なる第2ゲート誘電体を有する。第1トランジスタは第1ゲート電極を有し、そして第2トランジスタは第2ゲート電極を有する。第1及び第2ゲート電極は組成が同じである。第1ゲート誘電体及び第2ゲート誘電体は共に、酸化ハフニウム及び酸化アルミニウムのような高k誘電体を含むことができる。第1及び第2ゲート電極は共に、ゲート電極層を該当するゲート誘電体の上に含む。ゲート電極層は、TaSiN及びTaCのいずれかであることが好ましい。第1及び第2ゲート電極は共に、導電層をゲート電極層の上に含むことができる。このような一の実施形態では、導電層はポリシリコン及びタングステンからなる。  (もっと読む)

(もっと読む)

分離トレンチ

分離トレンチ(209)をウェハ(201)に形成するプロセスである。このプロセスでは、(例えば、異方性堆積法により)第1誘電体材料(307)をトレンチ(209)の中に堆積させ、次に第2誘電体材料(309)を(例えば、異方性堆積法により)トレンチ(209)内の第1誘電体材料(307)を覆うように堆積させる。第3材料(501)をトレンチ(209)内に、かつ第2誘電体材料(309)の上に堆積させる。第2材料(309)及び第3材料(501)の内の一方の材料は、他方の材料をエッチングしないように選択的にエッチングすることができる。一の例では、第1材料(307)は第2材料(309)よりも小さい誘電率を有する。  (もっと読む)

(もっと読む)

複数の狭区画レイアウトを用いたひずみデバイス

大きな引張応力を有する半導体デバイスを提供することを目的とする。半導体デバイスは、ソース領域及びドレイン領域を備える基板を有する。ソース領域及びドレイン領域の各々は、それぞれ、複数の分離されたソース区画及びドレイン区画を含む。シャロートレンチ分離(STI)領域がソース領域の2つの分離されたソース区画間及びドレイン領域の2つの分離されたドレイン区画間に形成される。ゲート積層体が基板に形成される。引張誘起層が基板上に形成される。引張誘起層はSTI領域、ソース領域、ドレイン領域及びゲート積層体を覆っている。引張誘起層は基板に引張応力を生じさせることが可能な絶縁体である。

(もっと読む)

(もっと読む)

ダイアモンド状のカーボンチャネルを有する電界効果トランジスタの製造方法、及び該製造方法により製造されるトランジスタ

ダイアモンド状のカーボンチャネルを有する電界効果トランジスタの製造方法、及び該製造方法により製造されるトランジスタ。

前記電界効果トランジスタは、ゲート絶縁膜(3)によりチャネル(7)から分離されたゲート電極(5)により制御されるチャネル(7)により接続されるソース(10)及びドレイン(11)を含む。前記チャネル(7)はダイアモンド状のカーボン層により形成される。前記トランジスタの製造方法は、続いて、ダイアモンド状のカーボン層を基板上(2)に堆積させ、ゲート絶縁層(3)を堆積させ、そして、少なくとも1つの導電層(4)を堆積させることを含む。前記導電層(4)は前記ゲート電極(5)からエッチングされる。次に、側面の絶縁膜(6)を形成するために、前記ゲート電極(5)の側面に絶縁材料が堆積される。次に、前記ゲート絶縁層(3)がエッチングされ、そして、前記ダイアモンド状のカーボン層がチャネル(7)の輪郭を描くようにエッチングされる。次に、前記ソース(10)を形成するための半導体材料、及び前記ドレイン(11)を形成するための半導体材料がチャネル(7)の両側に堆積される。  (もっと読む)

(もっと読む)

垂直型FIN−FETMOSデバイス

【課題】 トランジスタ本体として働く垂直方向のシリコン「フィン」を用いて、低い接触抵抗を持つ高密度の垂直型Fin−FETデバイスを生成すること。

【解決手段】 低い接触抵抗を示す新しいクラスの高密度の垂直型Fin−FETデバイスが説明される。これらの垂直型Fin−FETデバイスは、トランジスタ本体として働く垂直方向のシリコン「フィン」(12A)を有する。ドープされたソース領域及びドレイン領域(26A、28A)が、それぞれフィン(12A)の下部及び上部内に形成される。ゲート(24A、24B)が、フィンの側壁に沿って形成される。適切なバイアスがゲート(24A、24B)に印加されると、電流は、ソース領域(26A)とドレイン領域(28A)との間で、フィン(12A)を通して垂直方向に流れる。pFET、nFET、マルチ・フィン、シングル・フィン、マルチ・ゲート、及びダブルゲートの垂直型Fin−FETを同時に形成するための統合プロセスが説明される。

(もっと読む)

直流ノード拡散領域の下に埋め込み酸化物を有さず、酸化物ホールを有する差別化SOI構造

直流ノード拡散領域の下に埋め込み酸化物を設けず、すべてのデバイスのための本体接触部を有する選択的SOI構造を提供する。印加電圧Vdd、接地GND、基準電圧Vrefおよびその他の類似DCノードなどのDCノード拡散領域の直下に存在する埋め込み酸化物を設けずに、すべてのデバイスのための本体接触部を有する選択的SOI構造を提供する。本発明の選択的SOI構造をIC中に用いて回路の性能を改善することができる。本発明の選択的SOI構造は、上に配置された複数のSOIデバイスを有する上部Si含有層を備える絶縁体上シリコン(SOI)基板材料を含む。本SOIデバイスは、本体接触部領域を介して下地のSi含有基板と接触する。下地の埋め込み酸化物領域を備えないDCノード拡散領域がSOIデバイスの一つに隣接する。

(もっと読む)

(もっと読む)

半導体装置および半導体集積回路装置

pチャネルMOSトランジスタおよびnチャネルMOSトランジスタの各々においてチャネル方向を<100>方向に設定し、STI型素子分離構造に、引っ張り応力を蓄積した第1の応力補償膜を形成し、さらにシリコン基板上に素子分離構造を覆うように引っ張り応力を蓄積した第2の応力補償膜を形成する。 (もっと読む)

Si:CおよびSiGeエピタキシャル成長ソース/ドレインを用いた高性能で応力が向上されたMOSFETおよび製造方法

【課題】 半導体デバイスおよび半導体デバイスの製造方法を提供する。

【解決手段】 半導体デバイスはpFETおよびnFETのためのチャネルを含む。SiGe層はpFETチャネルのソースおよびドレイン領域に選択的に成長され、Si:C層はnFETチャネルのソースおよびドレイン領域に選択的に成長される。SiGe層およびSi:C層は、下に位置するSi層の格子ネットワークに一致して応力成分を生成する。1つの実施形態では、これによって、pFETチャネルでは圧縮成分が引き起こされ、nFETでは引張成分が引き起こされる。

(もっと読む)

高性能の歪みCMOSデバイス

【課題】 デバイス内の酸化に起因する圧縮応力を防止するために界面に覆い被さる浅いトレンチ分離領域(STI)を有する相補型金属酸化物半導体(CMOS)デバイスを提供すること。

【解決手段】 この半導体デバイス及び製造方法は、電流の流れの方向に平行な方向及び電流の流れに対し横方向に、Si−SiO2界面に覆い被さる張出し部を備えた浅いトレンチ分離領域を有するn型チャネル電界効果トランジスタ(n型FET)を提供する。また、このデバイス及び方法は、電流の流れに対し横方向に、Si−SiO2界面に覆い被さる張出し部を備えた浅いトレンチ分離領域を有するp型チャネル電界効果トランジスタ(p型FET)を提供する。しかしながら、p型FETの浅いトレンチ分離領域は、電流の流れの方向に平行な方向には張出し部を備えない。

(もっと読む)

ナノクラスターを備えた半導体デバイス

ナノクラスターを備えたデバイスを形成するプロセス。本プロセスは、ナノクラスター(例えばシリコンナノ結晶)を形成する段階と、デバイスの誘電体を形成する次の段階中に酸化剤によるナノクラスターの酸化を抑制するためにナノクラスターを覆って酸化バリア層を形成する段階とを含む。酸化バリア層の少なくとも一部は、誘電体の形成後に除去される。1つの実施例では、本デバイスは、ナノクラスターがメモリの電荷蓄積トランジスタの電荷蓄積位置として利用されるメモリである。この実施例では、酸化バリア層が、メモリの高電圧トランジスタ用のゲート誘電体を形成することにより、ナノクラスターを酸化剤から保護する。 (もっと読む)

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。また装置は、電荷キャリアが積層された層群と平行な方向に超格子を通って輸送される領域を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

格子不整合のソースおよびドレイン領域を有する歪み半導体CMOSトランジスタを有する集積回路および製作方法

【課題】 p型電界効果トランジスタ(PFET)およびn型電界効果トランジスタ(NFET)を有する集積回路を提供することにある。

【解決手段】 第1の歪みは、NFETではなくPFETのみのソースおよびドレイン領域内に配置されたシリコン・ゲルマニウムなどの格子不整合半導体層を介してNFETではなくPFETのチャネル領域に加えられる。PFETおよびNFETを形成するプロセスが提供される。PFETのソースおよびドレイン領域になるためのエリア内にトレンチがエッチングされ、それに隣接するPFETのチャネル領域に歪みを加えるために、格子不整合シリコン・ゲルマニウム層をそこにエピタキシャル成長させる。シリコン・ゲルマニウム層の上にシリコンの層を成長させ、シリコンの層からサリサイドを形成して、低抵抗ソースおよびドレイン領域を提供することができる。

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

741 - 759 / 759

[ Back to top ]