Fターム[5F048DA23]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 製造方法 (5,886) | ゲート側壁(サイドウォール) (5,329)

Fターム[5F048DA23]の下位に属するFターム

Fターム[5F048DA23]に分類される特許

161 - 180 / 759

半導体装置およびその製造方法

【課題】金属シリサイド膜の膜厚が薄くなってきたり、拡散層幅が小さくなってくると、拡散層上の金属シリサイドが凝集反応を起こしやすくなる、という問題があった。

【解決手段】半導体装置100は、半導体基板2と、半導体基板内に設けられた拡散層4と、半導体基板上に設けられたゲート絶縁膜12と、ゲート絶縁膜上に設けられたゲート電極14と、拡散層上に選択的に設けられたNiシリサイド層8と、を含み、Niシリサイド層8上にはCoを主成分とするメタルキャップ膜18が選択的に設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動能力に優れたPMOSトランジスタを実現する。

【解決手段】半導体装置は、半導体基板101における素子分離領域102によって分離された活性領域104上に形成されたPMOSトランジスタであって、このPMOSトランジスタは、活性領域104上に形成されたゲート絶縁膜105bと、ゲート絶縁膜上に形成されたゲート電極106bと、サイドウォール108bと、ソース・ドレイン拡散層領域107bとを備える。ソース・ドレイン拡散層領域107bは、半導体基板101の主面に対して傾斜面101Bを有している。

(もっと読む)

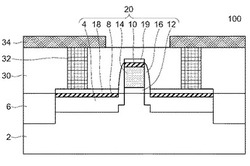

デュアル・ストレス・ライナ・プロセスと共存できる逆テーパ・コンタクト構造

【課題】デュアル・ストレス・ライナ・プロセスと共存できる逆テーパ・コンタクト構造を提供する。

【解決手段】半導体デバイスは、シリコン層と、該シリコン層中に電気的接続領域を有するトランジスタと、該電気的接続領域上に形成されかつ該領域と電気的に接触する導電性プラグとを有し、該プラグは該シリコン層から離れると内側に傾斜する側壁を有する。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート絶縁膜が大気やメタル電極のエッチング液等に曝されて劣化することなく、仕事関数の異なるnMOS、pMOSに適したメタルゲートMISFETを含む半導体装置の製造方法を提供する。

【解決手段】 メタル電極を有するn型MISトランジスタ及びp型MISトランジスタを備えた半導体装置の製造方法であって、単結晶シリコン基板100上に設けられたゲート絶縁膜102と、ゲート絶縁膜102上に設けられた第一の金属膜103、第二の金属膜104、第三の金属膜105、導電層106を備えたゲート電極108とを備えた構造であって、熱工程によって第二の金属膜104の構成元素を第一の金属膜103を通してゲート絶縁膜102中へ拡散させることによって、n型MISトランジスタ及びp型MISトランジスタそれぞれに適した仕事関数に変化させる。

(もっと読む)

半導体装置の製造方法

【課題】 窒素導入量を低減させることなく、絶縁膜へのダメージの導入を抑制し、かつ絶縁膜と半導体基板との界面における窒素濃度の増大を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板の表面上に、シリコンと酸素とを含む絶縁膜を形成する。(b)前記絶縁膜を活性窒素雰囲気に晒し、該絶縁膜に、その表面側から窒素を導入する。(c)前記工程(b)の後、酸素原子含有ガス中で熱処理を行う。(d)前記工程(c)の後、前記工程(b)と工程(c)とを、この順番に少なくとも1回繰り返す。

(もっと読む)

熱処理装置及び方法、並びに半導体装置の製造方法

【課題】例えば表面に様々なパターンが形成される被処理体に適宜対応した正確な光反射率を得ることができ、この光反射率に基づいて被処理体の温度を所望に保持する熱処理を可能とする。

【解決手段】半導体基板の表面における実効吸収率を正確に求めるべく、当該実効吸収率の算出に用いる第1の光源による照射光強度の角度分布(角度強度分布)を、アニール処理に用いる第2の光源による角度強度分布に適合させる。このように第1の光源を第2の光源と同等のものとして、第1の光源の照射光の光照射角度に対する光強度分布に依存した半導体基板の表面における光反射率、即ち実効反射率を求める。

(もっと読む)

半導体装置の製造方法

【課題】熱処理により抵抗素子に生じる抵抗値のばらつきを抑制する方法を提供する。

【解決手段】容量素子領域に溝部を形成する工程と、前記溝部側壁面および底面に、キャパシタ絶縁膜を形成する工程と、前記溝部を充填するように、また半導体基板上の抵抗素子領域を覆うように、非ドープシリコン膜を堆積する工程と、前記容量素子領域の、前記シリコン膜中に第1の不純物元素を、選択的にイオン注入する工程と、前記シリコン膜をパターニングして、前記容量素子の上部電極パターン及び抵抗パターンを形成する工程と、更に熱処理し、前記シリコン上部電極パターンにおいて、前記第1の不純物元素を拡散させる工程と、前記抵抗素子領域において、前記シリコン抵抗パターン中に不純物元素を、選択的にイオン注入する工程と、前記半導体基板上の論理素子領域に、ゲート絶縁膜と前記ゲート絶縁膜上のゲート電極パターンを有する半導体素子を形成する工程を含む。

(もっと読む)

半導体装置の製造方法

【課題】p−MISトランジスタとn−MISトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供する。

【解決手段】第1および第2領域13、14にゲート絶縁膜17を介して第1金属を含む第1金属膜18を形成する工程と、第1領域13における第1金属膜18を保護膜で被覆し、第2領域14における第1金属膜18を除去してゲート絶縁膜17を露出させる工程と、第1金属膜18上およびゲート絶縁膜17上に第1金属と異なる第2金属を含む第2金属膜19を形成する工程と、ゲート電極パターンを有するマスク材を用いて第2金属膜19を異方性エッチングし、第2領域14に第2ゲート電極を形成する工程と、第1金属膜18および第2金属膜19の露出部に酸化処理を施す工程と、第1領域13における第1金属膜18を異方性エッチングし、第1領域13に第1ゲート電極を形成する工程とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

静電気破壊保護素子、静電気破壊保護回路、半導体装置および半導体装置の製造方法

【課題】静電サージ電流によりソース・ドレイン間にかかる負荷をより軽減することが可能な静電気破壊保護素子を提供する。

【解決手段】この静電気破壊保護素子50は、シリコン基板1の表面にチャネル領域3を挟むように所定の間隔を隔てて形成されたn型のソース領域4およびドレイン領域5と、ソース領域4を覆うように形成されたp型ウェル領域7と、p型ウェル領域7の下方に形成されたn型の埋込層8と、ドレイン領域5と埋込層8との間に電流経路を構成するように形成されたn型層9とを備えている。

(もっと読む)

半導体集積回路の静電気保護装置、その製造方法および静電気保護装置を用いた静電気保護回路

【課題】サリサイド工程が用いられた場合であっても、製造工程に何等特別な工程やフォトマスクを迫加しないで形成できる静電気保護装置、その製造方法および静電気保護装置を用いた静電気保護回路を提供する。

【解決手段】静電気保護装置は、サイリスタと、サイリスタを低電圧でオン状態にトリガーするトリガーダイオードAとを備えており、ダイオードAは、n型カソード高濃度不純物領域9と、p型アノード高濃度不純物領域8と、領域9と領域8との間に形成され、半導体集積回路のMOSトランジスタのゲートを形成するゲート酸化膜13と、酸化膜13の上に積層されたポリシリコン14と、酸化膜13とポリシリコン14との側壁に形成され、領域9の表面に形成されるシリサイド層と領域8の表面に形成されるシリサイド層とを電気的に絶縁するゲート側壁絶縁体12とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】素子分離部の製造工程が増加するのを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】この発明の半導体装置100の製造方法は、半導体基板11を準備する工程と、互いに隣接する素子領域間に素子分離絶縁膜12を形成する工程と、半導体基板11の電界効果型トランジスタ2が形成される領域Bと、互いに隣接する素子領域間に配置される素子分離領域Cとに不純物を導入することにより、電界効果型トランジスタ2が形成される領域Bを覆うpウェル22と、素子分離領域Cの素子分離絶縁膜12の下面に接触するように配置されるpウェル28とを同時に形成する工程とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に格子歪を導入したMISFETを有する半導体装置の製造方法に関し、効率よくチャネル領域に格子歪みを導入してMISFET特性を向上しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板10上に、ポリシリコンよりなるゲート電極26nを形成し、ゲート電極26nの側壁部分にサイドウォールスペーサ28,38,40を形成し、ゲート電極26nの上端部がサイドウォールスペーサ28,38,40の上端部よりも低くなるように、ゲート電極26nをエッチングし、ゲート電極26nの一部をアモルファス化しゲート電極26nを覆うようにキャップ絶縁膜を形成し、アモルファス化したゲート電極26nを再結晶化するための熱処理を行う。

(もっと読む)

膜形成方法、半導体装置およびその製造方法

【課題】Vfbシフトと移動度低下を低減し、界面特性にすぐれたゲート絶縁膜構成を有する半導体装置を提供する。

【解決手段】シリコン基板を直接窒化して、シリコン窒化膜を形成し、前記シリコン窒化膜を、N2OとH2を含む混合ガスでアニールして、シリコン酸窒化(SiON)膜を形成する。このようなシリコン酸窒化膜は、半導体装置のゲート絶縁膜に適用することができる。

(もっと読む)

半導体装置

【課題】供給される電力を効率的に用いるためのチャージポンプ方式の昇圧回路を具備し、通信装置との通信距離が大きくなっても動作することのできる半導体装置を提供することを課題とする。

【解決手段】アンテナと、ダイオード及び容量素子より構成される複数のチャージポンプと、当該チャージポンプ間に設けられたスイッチとを具備する昇圧回路と、基準電圧を生成する参照電圧源回路と、コンパレータを有する電圧比較回路と、を有し、昇圧回路が具備するチャージポンプの各段の出力電圧を、コンパレータを用いて基準電圧と比較する。基準電圧と昇圧回路が具備するチャージポンプの各段の出力電圧の大小関係により、コンパレータの出力信号に基づいて昇圧回路のスイッチのオン又はオフを切り替えて出力を制御する。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、各ゲートについて均一で十分なフル・シリサイド化を実現する、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極の表層部分及びソース/ドレイン領域16a,16bの表層部分がシリサイド化されている状態において、半導体基板1にフラッシュランプアニールを施す。この処理により、ソース/ドレイン領域16a,16bには(NiPt)2Si層19bが形成された状態が保持されて、ゲート電極のみが選択的にフル・シリサイド化され、フル・シリサイドゲート電極21が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、活性領域と素子分離絶縁膜の界面に形成されるディボット(窪み)を抑制して、シリサイド化による接合リークの発生を防止する。

【解決手段】第1の活性領域の素子分離絶縁膜近傍の領域と第2の活性領域とを除く領域の前記第2のゲート絶縁膜を除去する工程と、前記第2のゲート絶縁膜を除去した半導体基板上に前記第1のゲート絶縁膜を形成する工程と、前記第1および第2の活性領域上にそれぞれゲート電極を形成する工程とを有する。これにより、第1の活性領域の素子分離絶縁膜近傍、並びに第2の活性領域の全体では、この第2のゲート絶縁膜が残っているため、ディボットが生じることがないか、生じたとしてもサイズが小さくなるのである。

(もっと読む)

プラズマ酸化処理方法およびシリコン酸化膜の形成方法

【課題】 複雑なプロセスを必要とせずに、同一のシリコン層に形成されたp型拡散領域およびn型拡散領域に、それぞれ異なる膜厚でシリコン酸化膜を形成する。

【解決手段】 酸素およびArを含有する処理ガスのプラズマにより、p型拡散領域103とn型拡散領域105とを、それぞれ異なる酸化レートで酸化処理する。p型拡散領域103の表面には膜厚T1の厚膜部107aが形成され、n型拡散領域105の表面には、厚膜部107aよりも薄い膜厚T2の薄膜部107bが形成される。

(もっと読む)

相補型半導体装置の製造方法

【課題】製造工程を簡略化する。

【解決手段】一枚の絶縁性基板3上にnチャネル型MOSトランジスタ21およびpチャネル型MOSトランジスタ22からなる相補型半導体装置を形成する製造方法において、nチャネル型MOSトランジスタ21のチャネル領域7と接合するソース領域5Sおよびドレイン領域5Dのいずれか一方をショットキー接合とし、他方をp−n接合とする際、前記p−n接合を前記ショットキー接合より先の工程で形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】

STIによる新たな課題を抑制できる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、(a)Si基板上方に素子分離領域を包含する平面形状の開口を有するマスク層を形成する工程と、(b)マスク層の開口側壁上に、マスク層に対して選択的に除去可能な材料のサイドウォールスペーサを形成する工程と、(c)マスク層、サイドウォールスペーサをエッチングマスクとして、Si基板をエッチングしてトレンチを形成する工程と、(d)トレンチを埋める絶縁素子分離領域を形成する工程と、(e)サイドウォールスペーサを選択的に除去する工程と、(f)Si基板上方から、窒素をイオン注入する工程と、(g)マスク層を除去する工程と、(h)絶縁素子分離領域によって画定された活性領域に半導体素子を形成する工程と、を含む。

(もっと読む)

161 - 180 / 759

[ Back to top ]