Fターム[5F048DA23]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 製造方法 (5,886) | ゲート側壁(サイドウォール) (5,329)

Fターム[5F048DA23]の下位に属するFターム

Fターム[5F048DA23]に分類される特許

121 - 140 / 759

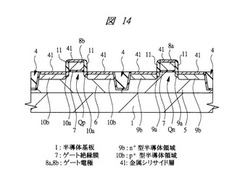

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細で精度が高く、歩留まりが向上した半導体装置を提供する。

【解決手段】半導体装置は、第1トランジスタ2と第2トランジスタ5とを具備する。第1トランジスタ2は、半導体基板100上に第1ゲート絶縁膜51を介して形成された第1ゲート電極21と第1ソース・ドレイン領域31と第1共通ソース・ドレイン領域30とを備える。第2トランジスタ5は、半導体基板100上に第2ゲート絶縁膜51を介して形成された第2ゲート電極22と第2ソース・ドレイン領域31と第1共通ソース・ドレイン領域30とを備える。第1ゲート電極21及び第2ゲート電極22は、第1共通ソース・ドレイン領域30のコンタクトである第1ノード電極41の両側壁に設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】 周辺回路領域の電荷蓄積層へのホットキャリア注入の影響を少なくする半導体装置等を提供する。

【解決手段】 半導体装置であって、少なくとも1つの不揮発性記憶セルの少なくとも1つの第1のトランジスタと、前記少なくとも1つの不揮発性記憶セルを駆動するための少なくとも1つの第2のトランジスタと、を含む。第1のトランジスタは、第1のゲート絶縁層と、第1のゲート電荷蓄積層と、第2のゲート絶縁層とを有する。第2のトランジスタは、第3のゲート絶縁層と、第2のゲート電荷蓄積層と、第4のゲート絶縁層とを有する。フッ素系ガスおよび/または水素系ガスを用いるイオン注入が実施された前記第2のゲート電荷蓄積層(22b’)の全部または一部の第1の電荷蓄積能力は、フッ素系ガスおよび/または水素系ガスを用いるイオン注入が実施される前の前記第2のゲート電荷蓄積層(22b’)の前記全部または前記一部の第2の電荷蓄積能力より低い。

(もっと読む)

半導体装置

【課題】インダクタ下方の半導体基板内における渦電流の発生をなくすことにより、インダクタのQ値の向上を図り、このインダクタを用いて形成される半導体装置の性能を向上させる。

【解決手段】低濃度P型の半導体基板101の上面内には素子分離層102および導電型層103が形成されており、また、その上面上には配線層間絶縁膜104およびスパイラル形状のインダクタ105が積層されている。このような半導体装置では、インダクタ105下方の低濃度P型シリコン基板内101にシリコン基板101の表面から厚み方向に空乏層106が形成されているため、インダクタ105を流れる電流によって誘起される渦電流は空乏層106によって遮断される。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの特性が劣化するのを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、シリコン基板11の領域A上にプレーナ型のバイポーラトランジスタ1を形成する工程と、プレーナ型バイポーラトランジスタ1が形成される領域を覆うようにシリコン窒化膜からなるカバー膜32aを形成する工程と、その後、プレーナ型のバイポーラトランジスタ1が形成される領域Aがカバー膜32aに覆われた状態で、バイポーラトランジスタ1が形成される領域にイオン注入する工程とを備える。

(もっと読む)

半導体装置、キャパシタ、および電界効果トランジスタ

【課題】半導体と金属との界面において、接合する金属の実効仕事関数を最適化した半導体装置を提供することを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aとを備え、酸化膜がHf酸化膜或いはZr酸化膜であって、酸化膜に、V、Cr、Mn、Nb、Mo、Tc、W、Reから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】側面方位とキャリア極性に応じて歪み方向が最適化されたFinFETおよびナノワイヤトランジスタと、これを実現するSMTを導入した製造方法を提供する。

【解決手段】半導体基板14と、半導体基板14の上部に形成され、半導体基板14主面に平行な上面と、半導体基板14主面に垂直な(100)面の側面を有する直方体状半導体層40と、直方体状半導体層40内に形成されるチャネル領域18と、チャネル領域18の少なくとも側面上に形成されるゲート絶縁膜20と、ゲート絶縁膜20上のゲート電極30と、直方体状半導体層40内に、チャネル領域18を挟み込むよう形成されるソース/ドレイン領域とを備え、チャネル領域18に、半導体基板14主面に対して垂直方向の圧縮歪みが印加されているpMISFETを有することを特徴とする半導体装置およびその製造方法。

(もっと読む)

ESD保護素子及びその製造方法

【課題】LSI製造工程の最終段階においても、内部素子の基本性能を変えることなく、内部素子と同一プロセスで形成されたESD保護素子のブレークダウン電圧を調整可能とすることを目的とする。

【解決手段】MOS構造のドレイン領域とMOS構造を囲む素子分離領域との間にドレイン領域に接してこれとPN接合を形成する接合形成領域を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】バイポーラトランジスタの耐圧の確保と電流増幅率hFEの向上とが容易な半導体装置およびその製造方法を提供する。

【解決手段】SOI基板のSOI層SLにバイポーラトランジスタBTと、nMOSトランジスタNTと、pMOSトランジスタPTとが形成されている。バイポーラトランジスタBTのコレクタ領域CLのn-領域CLLは、SOI層SLの厚み方向に対してpMOSトランジスタPTのn-チャネル形成領域NCと同じ不純物濃度分布を有している。バイポーラトランジスタBTのベース領域BAは、pMOSトランジスタPTのn-チャネル形成領域NCのn型の不純物濃度よりも高いp型の不純物濃度を有している。

(もっと読む)

トランジスタおよびその製造方法

【課題】レベルシフタ回路等に使用する、例えば耐圧が30V以上のトランジスタを提供する。

【解決手段】デプレッション型トランジスタが、第1導電型の半導体基板と、半導体基板の表面に形成された第2導電型のカウンタドープ層と、カウンタドープ層の上に設けられ、誘電体膜と、その上に形成された導電体層とを含むゲート電極と、ゲート電極の両側の半導体基板に形成された第2導電型層とを含み、ゲート電極の下方のカウンタドープ層がチャネル領域となり、第2導電型層がソース/ドレイン領域となり、ソース/ドレイン領域は、更に、第2導電型層と半導体基板の表面との間に形成された第1導電型層を含む。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの性能の低下を抑制できる半導体装置を提供する。

【解決手段】第一のトランジスタ11、第二のトランジスタ12、ゲート構造13を被覆する応力付与層16を設ける工程の前段で、第二のトランジスタ12上に他のシリコン酸化膜14を形成し第二のトランジスタ12上に所定の厚みのシリコン酸化膜18を形成する。第二のトランジスタ12及びゲート構造13上の応力付与層16を除去し第一のトランジスタ11上に応力付与層16を残す工程にて、第二のトランジスタ12上のシリコン酸化膜が第一のトランジスタ11上のシリコン酸化膜よりも過剰に薄くなってしまうことが防止される。第一のトランジスタ11及び第二のトランジスタ12上のシリコン酸化膜15,18等を除去する際に第二のトランジスタ12上のシリコン酸化膜が薄いため第二のトランジスタ12のソース領域、ドレイン領域が削れてしまうことを防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】P、Nchそれぞれのチャネル部の応力を最適化するために、片方ずつ異なる応力の応力制御膜を成膜する半導体装置の提供。

【解決手段】半導体装置は、P、Nch共通で、膜厚方向で膜の応力の方向性が異なる応力制御膜5を用いて、その膜厚によって、P、Nchのチャネル部応力をそれぞれ最適化する。即ち、応力制御膜5の膜厚はNch領域の方をPch領域に比べて薄い膜厚とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、閾値電圧(Vth)が低く、且つ半導体特性に問題が生じないハイブリッド構造の半導体装置を提供することを目的とする。

【解決手段】本発明は、基板1に設けた第1ソース領域2と第1ドレイン領域3との間の基板1上にhigh−k膜の第1ゲート絶縁膜4と、第1ゲート絶縁膜4上にポリシリコン膜の第1ゲート電極とを備えたn型の半導体素子と、基板1に設けた第2ソース領域2と第2ドレイン領域3との間の基板1上にhigh−k膜の第2ゲート絶縁膜4と、第2絶縁膜上に第1金属膜7,8と、第1金属膜7,8上にポリシリコン膜の第2ゲート電極とを備えたp型の半導体素子とを備えるハイブリッド構造の半導体装置である。そして、本発明の1つの実施形態では、第1金属膜8が、窒化チタン単体よりも仕事関数が高くなる添加物質を添加した窒化チタン膜を有している。

(もっと読む)

半導体装置、およびその製造方法

【課題】p型トランジスタのゲート電極へのダメージを抑えつつ形成することのできる半導体装置、およびその製造方法を提供する。

【解決手段】第1のチャネル領域側に導電型不純物が偏析して形成されたエクステンション領域を有する第1のソース・ドレイン領域、および前記第1のソース・ドレイン領域上に前記第1のスペーサに接して形成された第1のシリサイド領域を含むn型トランジスタ10と、第2のチャネル領域側にエクステンション領域を有する第2のソース・ドレイン領域、および前記第2のソース・ドレイン領域上に前記第2のスペーサと離間して形成された第2のシリサイド領域を含むp型トランジスタ20と、前記第1のチャネル領域にチャネル方向の伸張歪みを与える伸張応力膜18と、第2のチャネル領域にチャネル方向の圧縮歪みを与える圧縮応力膜28と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】リーク電流の発生なくp型領域やn型領域を半導体基板上に結晶成長させてなるサイリスタ構成の素子を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1の表面側にp型領域、n型領域、p型領域、およびn型領域がこの順に接して設けられた素子を備え、少なくとも1つの領域が半導体基板1の表面に結晶成長させた結晶成長層からなる半導体装置の製造方法において、第1n領域25および第2p領域27を結晶成長層として形成する際には、半導体基板1上に第1絶縁膜17と第2絶縁膜19との積層膜を成膜する第1工程と、第2絶縁膜19のエッチングに続けて第1絶縁膜17をウェットエッチングすることによって半導体基板1に達する開口を形成する第2工程と、開口底部に露出する半導体基板1の表面に、第1n領域25および第2p領域27を選択的に結晶成長させる第3工程とを行う。

(もっと読む)

半導体装置

【課題】ESD保護機能を有した半導体装置を少ない工程で製造可能な半導体装置を提供する。

【解決手段】半導体基板上に異なる導電型の少なくとも2つのウェル(Nウェル12a,Pウェル12b)を設け、ウェル内に、そのウェルと同一導電型であるウェルコンタクト用の拡散領域13a,13bと、ソース領域16a,16bまたはドレイン領域17a,17bの一方に電源を接続したMOSFETと、ソース領域16a,16bまたはドレイン領域17a,17bと同じ導電型であり抵抗として機能するとともに、拡散領域13a,13bとの間でダイオードとして機能する拡散領域14a,14bとを設ける。ソース領域16a,16bまたはドレイン領域17a,17bの他方と拡散領域14a,14bの一端を接続し、拡散領域14a,14bの他端を出力端子OUTに接続する。

(もっと読む)

半導体装置とその製造方法

【課題】

ロジックプロセスとの整合性の高い、メモリセルを含む半導体装置及びその製造方法を提供する。

【解決手段】

半導体装置は、半導体基板の主面側に画定され、各々が、長尺状の平面視形状を有し、トランジスタ部とキャパシタ部を含む、複数の活性領域と、活性領域を取り囲んで半導体基板に形成された溝部と、該溝部を埋め込んだ絶縁材とを含むSTIと、各活性領域のキャパシタ部の幅方向両側のSTIの絶縁材を底部を残して掘り下げ、活性領域側壁を露出するキャパシタ用凹部と、各活性領域のトランジスタ部上面上に形成され、第1絶縁膜とその上の第1導電層とを含む絶縁ゲート電極構造と、各活性領域のキャパシタ部の上面上と露出された側面上に形成され、第1絶縁膜と同一材料で形成された第2絶縁膜と、第2絶縁膜を覆い、複数の活性領域に亘って、第1導電層と同一材料で形成された第2導電層とを含むMISキャパシタ構造と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】膜厚の異なるSOI層に複数種のトランジスタを形成した半導体装置において、複数種のトランジスタ間の素子分離が精度良く行える半導体装置及びその製造方法を得る。

【解決手段】SOI層3は厚膜SOI領域101及び薄膜SOI領域102を有し、厚膜SOI領域101の上層部はエピタキシャルSOI層で形成され、このエピタキシャルSOI層の膜厚分、厚膜SOI領域101のSOI膜厚t1は、薄膜SOI領域102のSOI膜厚t2より厚い。厚膜SOI領域101,薄膜SOI領域102間は完全分離酸化膜10fにより素子分離される。厚膜SOI領域101内及び薄膜SOI領域102内はそれぞれ部分分離酸化膜10pにより隣接するトランジスタ間が素子分離される。完全分離酸化膜10f及び部分分離酸化膜10pの上面は厚膜SOI領域101及び薄膜SOI領域102におけるSOI層3の上面よりも高く形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】NMOSとPMOSとの境界を明確化して更なる微細化を可能とし、NMOSとPMOSとの閾値電圧を共に実用レベルの低い値に設定できる半導体装置を提供する。

【解決手段】 この半導体装置1は、ゲート電極Gnが金属シリサイド層111/La含有層105/ゲート絶縁膜103の積層構造のNMOSトランジスタと、ゲート電極Gpが前記金属シリサイド層111と同一組成の金属シリサイド層111/前記La含有層105と同一組成のLa含有層105/メタル層104/ゲート絶縁膜103の積層構造のPMOSトランジスタとを備える。

(もっと読む)

半導体装置の製造方法および半導体ウエハ洗浄装置

【課題】カロー酸を用いたウエハ(基板)洗浄工程において、H2O2の使用量を低減しつつ、フォトレジスト膜(感光性マスキング層)の除去性を向上できる技術を提供する。

【解決手段】基板1の洗浄(フォトレジスト膜の除去)時以外のSPM液中のH2O2の濃度は、フォトレジスト膜の少なくとも一部を除去できる最低限の第1濃度以上で制御する。そして、基板1をSPM槽51(内槽51A)へ浸漬する直前に、SPM液中のH2O2の濃度がフォトレジスト膜を確実に除去できる第2濃度以上となり、また基板1をSPM槽51(内槽51A)へ浸漬した時にSPM液中のH2O2の濃度がその第2濃度未満とならないように、過酸化水素水供給系54からSPM槽51(内槽51A)へ所定量のH2O2を供給する。

(もっと読む)

121 - 140 / 759

[ Back to top ]