Fターム[5F048DA26]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 製造方法 (5,886) | ゲート側壁(サイドウォール) (5,329) | 材料 (3,524) | 高融点金属硅化物 (13)

Fターム[5F048DA26]に分類される特許

1 - 13 / 13

半導体装置の製造方法

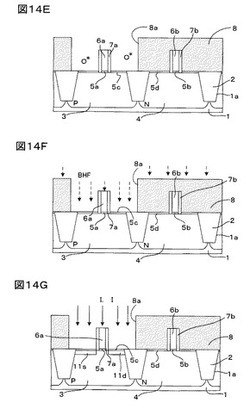

【課題】レジストパターンの下地層への悪影響を及ぼすことなくスカムを最適に除去する半導体装置の製造方法を提供する。

【解決手段】半導体基板1の上に酸化膜5cを形成し、前記酸化膜5c上にフォトレジスト8を塗布し、前記フォトレジスト8を露光し、露光された前記フォトレジスト8を現像することにより前記フォトレジス8トに開口部8aを形成し、前記フォトレジスト8をマスクとして、前記酸化膜5cを酸素プラズマ処理し、前記酸素プラズマ処理の後、前記酸化膜5cと前記フォトレジスト8に希釈フッ酸を供給し、前記希釈フッ酸を供給する工程の後、前記フォトレジスト8をマスクとして前記酸化膜5cを通して記半導体基板1に一導電型不純物をイオン注入する工程を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETのしきい値を調整する目的でLaなどが導入された高誘電率膜を含むゲート絶縁膜と、その上部のメタルゲート電極との積層構造を有する半導体装置において、ゲート電極のゲート幅を縮小した際、基板側からメタルゲート電極の底面に酸化種が拡散してnチャネル型MISFETの仕事関数が上昇することを防ぐ。

【解決手段】HfおよびLn含有絶縁膜5bとその上部のメタルゲート電極である金属膜9との間に、酸化種の拡散を防ぐためにAl含有膜8cを形成する。

(もっと読む)

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

電気的にプログラムされたソース/ドレイン直列抵抗を有するMOSトランジスタ

【課題】高速度MOSFETを形成するための半導体デバイス技術が要請されている。

【解決手段】トランジスタゲートサイドウォールスペーサ(27)に埋め込まれた導電層(24)を形成することによって高速MOSトランジスタ(32)は、用意される。この埋め込まれた導電層(24)は、トランジスタ(32)のゲート電極(18)とソース/ドレイン領域(28)から電気的に絶縁している。埋め込まれた導電層(24)は、ソース/ドレイン伸長領域(30)を覆うように配置され、ソース/ドレイン領域(28)直列抵抗を低くすることでソース/ドレイン伸長領域内に電荷を蓄積する。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

電子装置の製造方法および半導体装置の製造方法

【課題】露光装置の解像限界を超えた微細なパターンを有するDRAMやFeRAMおよびクロスバー素子等の電子装置の製造方法を提供する。

【解決手段】基板10上にダミー11膜を基板10上の素子領域10Aおよびその外側の外部領域10Bを覆うように形成してパターニングし、ダミーパターン11を素子領域10Aにおいては第1の高さH1に、外部領域10Bにおいては第1の高さH1よりも小さい第2の高さH2を有するように形成し、基板10上に別の膜12をダミーパターン11A,Bを覆うように形成し、膜12を異方性エッチングして素子領域中のダミーパターン11Aの側壁面に沿って第1および第2のパターン12A、Bを形成し、かつ、外部領域10Bにおいては膜12消失させ、素子領域10Aにおいて、第1および第2のパターン12A,Bを使って電子装置を形成する。

(もっと読む)

珪化コバルトを含んだトランジスタゲート、そのトランジスタゲートを含んだ半導体装置構造、前駆構造、および製造方法

珪化コバルトを含んだ導電性要素を持つトランジスタゲートを製造するための方法であって、高温工程(迫り上げ式ソースドレイン領域の作成など)が完了する後までに、トランジスタゲートの側壁スペーサー同士のあいだにて、犠牲材料を仮置きとして用いることを含む。加えて、珪化コバルトをその導電性要素内に有するトランジスタゲートを具えた半導体装置(DRAM装置およびNANDフラッシュメモリ装置など)も開示しており、同様に、迫り上げ式ソースドレイン領域および珪化コバルトをそのトランジスタゲート内に持つトランジスタも開示する。側壁スペーサー同士の上部のあいだに犠牲材料もしくは空隙を持つトランジスタゲートを含んだ、中途半導体装置構造についても開示をしている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体製造工程で加わる熱履歴の違いに因り、不純物の拡散具合が異なることから、薄膜トランジスタの閾値にばらつきを生じた。これを低減、防止する対策を施した薄膜トランジスタを有する半導体装置及びその製造方法を提供する。

【解決手段】薄膜トランジスタは、絶縁体層を介して半導体基板上に形成された、不純物を含むソース/ドレイン領域と、前記ソース/ドレイン領域間を充填する絶縁体と、前記ソース/ドレイン領域上に形成された不純物拡散制御膜層と、前記不純物拡散制御膜上に形成されたチャネル層と、前記チャネル層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記チャネル層、ゲート絶縁膜及びゲート電極を充填する層間膜とを具備する。前記不純物拡散制御膜は、熱の加わらない製造工程の段階になって、前記ソース/ドレイン領域とチャネル層との間に所定の電圧を印加することにより絶縁破壊される。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】半導体装置のソース/ドレインとゲートおよびウェル間の漏洩電流を低減する。

【解決手段】電界効果トランジスタ2は、ゲート電極4のいずれかの側面に配置された第1および第2ソース/ドレイン領域28を備え、第1および第2ソース/ドレイン領域28に挟まれた、ゲート電極4の直下に位置する半導体基板24内に、チャネル領域26が形成される。基板上にゲート酸化物層22が形成される。ゲート電極4は、ゲート酸化物層22の表面と接触しており、少なくとも第1導電体層10および第2導電体層12を備える。第1導電体層10および第2導電体層12は互いに異なる仕事関数を有する材料から構成されている。ゲート電極4の第1導電体層10はゲート酸化物層22表面の第1部分40と接触しており、第2導電体層12はゲート酸化物層の表面の第2部分42と接触している。第1導電体層10は、さらに第2導電体層12と導電接続されている。

(もっと読む)

異なる絶縁体の側壁スペーサを有するメモリ回路を形成するための方法

本発明はメモリ回路を形成する方法を含んでいる。一つの実施の形態として、メモリアレイ回路領域(14)および周辺回路領域(16)を有する基板(12)を設けている。前記メモリアレイ回路領域は、第一の最小配線間隙(D1)をともなうトランジスタゲート配線(15)を含んでいる。前記周辺回路領域は、前記第一の最小配線間隙よりも大きい第二の最小配線間隙(D2)をともなうトランジスタゲート配線(17)を含んでいる。前記メモリアレイ領域内の個々の前記トランジスタゲート配線の向かいあう側壁上方に異方性エッチングされた絶縁体の側壁スペーサ(40)を形成するよりも先に、前記周辺回路領域内の個々の前記トランジスタゲート配線に向かいあう側壁上に異方性エッチングされた絶縁体の側壁スペーサ(34)を形成している。他の特徴と実施の形態が考えられる。 (もっと読む)

半導体装置の製造方法および半導体装置

【課題】相対的に高いON電流と、相対的に低いしきい値電圧とを有するMISFETを形成する。

【解決手段】ゲート溝19の内壁に沿って高誘電率膜20を形成し、高誘電率膜20上に相対的に低い温度により酸化する金属膜を積層し、金属膜に不純物をイオン注入した後、相対的に低い温度で金属膜を酸化させて酸化金属膜を形成すると同時に、不純物を高誘電率膜20と酸化金属膜との界面に偏析させる。次いで、酸化金属膜を実質的に全て除去した後、改めて相対的に抵抗の低い金属膜をゲート溝19の内部に埋め込むことにより、金属ゲート24を形成する。

(もっと読む)

半導体装置

【課題】 完全空乏型MISFETでは、単結晶SOI層が数十nm程度と薄くなると、不純物濃度によるしきい値電圧Vthの制御には原理的に限界があり、相補型MISFETにおいてp型とn型の双方の所期のVthを同時に実現することは困難であった。

【解決手段】MISFETのゲート絶縁膜を金属酸化物4と酸窒化膜3の積層とし、ゲート電極5はソース・ドレイン6と同じ導電型の多結晶Si半導体膜を用いて形成する。ゲート絶縁膜と半導体膜のゲート電極に発生するフラットバンド電圧のシフトにより、エンハンスメントの所期のVthが同時に達成される。不純物濃度によりVthを制御する場合に較べ、1つのMISFETに対する不純物の個数の統計的なゆらぎによるVthのばらつきを低減できるため、Vth、電源電圧ともに低く設定することが可能となる。

(もっと読む)

CMOSシリサイド金属ゲート集積化

本発明は、ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。本発明の集積化方式を用いて形成される各シリサイド金属ゲートは、シリサイド金属ゲートの寸法に関わりなく、同じシリサイド金属相および実質的に同じ高さを有する。本発明は、半導体構造物の表面全体にわたってポリSiゲート高さが実質的に同じであるシリサイド接点を有するCMOS構造物を形成するさまざまな方法も提供する。

(もっと読む)

(もっと読む)

1 - 13 / 13

[ Back to top ]