Fターム[5F064AA04]の内容

ICの設計・製造(配線設計等) (42,086) | ICの形式 (1,534) | カスタムIC (1,426) | セミカスタムIC (1,415) | 標準セル、スタンダードセル (922)

Fターム[5F064AA04]の下位に属するFターム

ポリセル (86)

ビルディングブロック (241)

Fターム[5F064AA04]に分類される特許

201 - 220 / 595

集積回路設計方法及び集積回路設計装置

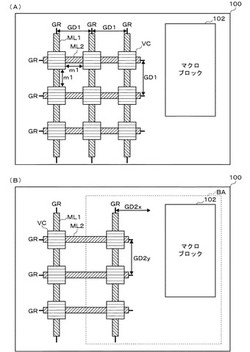

【課題】処理負荷の増大を抑えながら、所定のマクロブロック周辺において複数の配線の影響を確実に低減できる集積回路設計方法及び集積回路設計装置を提供する。

【解決手段】集積回路設計方法は、所与の領域を配線グリッド変更領域として設定する配線グリッド変更領域設定ステップと、前記配線グリッド変更領域設定ステップにおいて前記配線グリッド変更領域として設定された前記領域内の配線グリッドの間隔をより大きく変更する配線グリッド変更ステップと、前記領域内において、前記配線グリッド変更ステップにおいて前記間隔が変更された配線グリッドに所与の配線を配置すると共に、前記配線グリッド変更ステップにおいて変更された前記配線グリッドの間隔に対応したセルグリッド間隔でその構成が指定されたセルを、前記配線グリッド変更ステップにおいて前記間隔が変更された配線グリッドに配置する配置配線ステップとを含む。

(もっと読む)

集積回路設計方法、集積回路設計装置、集積回路及び電子機器

【課題】処理負荷の増大を抑えながら、これまで配線が混雑していた領域でも確実にセルや配線を配置できる集積回路設計方法等を提供する。

【解決手段】集積回路設計方法は、所与の領域を配線グリッド変更領域として設定する配線グリッド変更領域設定ステップと、前記配線グリッド変更領域設定ステップにおいて前記配線グリッド変更領域として設定された前記領域内の配線グリッドの間隔をより小さく変更する配線グリッド変更ステップと、前記領域内において、前記配線グリッド変更ステップにおいて前記間隔が変更された配線グリッドに所与の配線を配置すると共に、前記配線グリッド変更ステップにおいて変更された前記配線グリッドの間隔に対応したセルグリッド間隔でその構成が指定されたセルを、前記配線グリッド変更ステップにおいて前記間隔が変更された配線グリッドに配置する配置配線ステップとを含む。

(もっと読む)

半導体集積回路及び多電源レイアウト設計方法

【課題】セルに供給される電源に依存しない自由な配置を実現し、常時通電用電源線と電源遮断用電源線を並層で構成しても、電源幹線から基準電位線への配線接続が容易な半導体集積回路を提供すること。

【解決手段】複数の回路セルを有する半導体集積回路は、当該半導体集積回路の電源幹線と、電源幹線から縞状に配線された電源配線群と、一時的に回路セルへの電源供給を遮断する電源スイッチセルと、電源スイッチセルを介して遮断用電源が供給される電源遮断対象セルと、電源スイッチセルを介さず、常時通電用電源が供給される常時通電セルと、を備える。電源配線群は、第1層メタル配線を介して電源スイッチセルと電源遮断対象セルを接続する遮断用電源供給線と、第2層メタル配線を介して電源スイッチセルと常時通電セルを接続する基準電位供給線とを含む。

(もっと読む)

動的アレイアーキテクチャにおけるセル位相整合及び配置の方法及びその実施

半導体チップは、レイアウト特徴部が第1の仮想格子に従って配置される第1のチップレベルと、レイアウト特徴部が第2の仮想格子に従って配置される第2のチップレベルとを有する論理ブロック区域を含むように定められる。第1の仮想格子と第2の仮想格子の間には、有理空間的関係が存在する。論理ブロック区域内には、複数のセルが配置される。複数のセルの各々は、複数のセル位相のうちの適切な1つに従って定められる。複数のセル位相のうちの適切な1つは、所定の配置セルの第1及び第2のチップレベル内のレイアウト特徴部を所定の配置セルに位置決めされた第1及び第2の仮想格子と整合させる。 (もっと読む)

半導体集積回路の設計方法、製造方法、回路設計プログラム、及び半導体集積回路

【課題】レイアウト修正による遅延変動を抑制しつつ半導体集積回路のプラズマダメージを軽減する製造方法を提供する。

【解決手段】半導体集積回路の製造方法は、コンピュータによって実行され、第1ゲート電極21に接続する金属配線と、第1ゲート電極21とのアンテナ比を検証するステップと、アンテナ比の検証結果に基づいて半導体集積回路のレイアウトを変更するステップとを具備する。レイアウトを変更するステップは、複数の論理セルから、アンテナ比の検証結果に応じたゲート面積の論理セルを選択するステップと、論理セルを、論理動作しないフィルセル40として空き領域に配置するステップと、フィルセル内の第2ゲート電極41を金属配線に接続するステップとを備える。

(もっと読む)

半導体集積回路装置

【課題】OPC補正のデータ量や処理時間の増大を伴うことなく、セル境界線に近いメタル配線の細りや断線を防止可能な半導体集積回路のレイアウト構造を提供する。

【解決手段】第1の方向に延びるように配置された電源配線m1および接地配線m2に挟まれた領域に、回路機能を実現するトランジスタおよびセル内配線をそれぞれ有する第1および第2のセルが、第1の方向において隣接するように配置されている。第1および第2のセルの境界部に、第1の方向と直交する第2の方向に延びるメタル配線d2が、電源配線m1と接地配線m2とを短絡しないように、配置されている。

(もっと読む)

回路設計装置、回路設計方法、及び回路設計プログラム

【課題】 本発明の課題は、電源のオン・オフのタイミングの異なる複数のセルアレイ領域を伝播する信号のタイミングを最適化することを目的とする。

【解決手段】 上記課題は、異なる電源制御のタイミングを有する複数のパワードメインにおいて伝播する信号のタイミングエラーを検出するエラー検出手段と、前記信号が伝播する経路におけるエラーセルに対する隣接パワードメインと該エラーセルが配置されているパワードメインとの電源制御のタイミングに基づいて該隣接パワードメインに挿入するためのセル種別を決定するセル種別決定手段と、前記セル種別決定手段によって決定されたセル種別のセルを該隣接パワードメインに挿入配置するセル挿入配置手段とを有する回路設計装置により達成される。

(もっと読む)

集積回路装置の設計方法及び製造方法並びに電子機器

【課題】ライブラリ開発工数を低減することができる集積回路装置の設計方法及び製造方法並びに電子機器を提供すること。

【解決手段】本発明の集積回路装置の設計方法は、第1〜第Nの異なる論理をそれぞれ有する第1〜第Nの論理セルの特性情報と第1〜第Mの異なる電流供給能力をそれぞれ有する第1〜第Mの電流供給セルの特性情報とを含むライブラリを作成し(ステップS20)、ライブラリを用いて論理回路の回路接続情報及びレイアウトパターンを作成し(ステップS30)、論理回路の回路接続情報及びレイアウトパターンに基づいて論理回路を含む集積回路の回路接続情報及びレイアウトパターンを作成する(ステップS40)。ステップS30において、論理回路が第n(1≦n≦N)の論理と第m(1≦m≦M)の電流供給能力を有する回路を含む場合には、第nの論理セルと第mの電流供給セルを用いて回路接続情報及びレイアウトパターンを作成する。

(もっと読む)

半導体集積回路

【課題】ウェハプロセス後にゲートパターン(ゲート形状)の仕上がりが均一の値を保つことができるセルベース方式による半導体集積回路を提供する。

【解決手段】半導体基板上(図示せず。)に、p型の活性領域1とn型の活性領域2とが形成されている。そして、このp型の活性領域1とn型の活性領域2上に、3本のゲート配線3,4,5が形成され、p型の活性領域1には、n型の活性領域2と向かい合う側の反対の側(図ではp型の活性領域1の上側)にコンタクトホール6,7を設けるための突出部が形成されている。この突出部に形成されたコンタクトホール6は、ゲート配線3とゲート配線4との間に形成されている。また、突出部に形成されたコンタクトホール7は、ゲート配線4とゲート配線5との間に形成されている。

(もっと読む)

集積回路装置のレイアウト設計方法及び製造方法並びに電子機器

【課題】設計工数をほとんど増加させることなく、マクロセルの配置ミスを容易に発見することができる集積回路装置のレイアウト設計方法及び製造方法並びに電子機器を提供すること。

【解決手段】本発明の集積回路装置のレイアウト設計方法は、マクロセルに形成されたデザインルールを満たす第1のダミーパターンに対応させて、マクロセルの配置予定領域の一部にデザインルールを満たす第2のダミーパターンを作成し(S20)、マクロセルを配置し(S30)、マクロセル配置後のレイアウトパターンが所定のデザインルールを満たすか否かをチェックする(S40)。マクロセルが配置予定領域に配置された場合には第1のダミーパターンと第2のダミーパターンによって形成されるダミーパターンは所定のデザインルールを満たし、マクロセルが配置予定領域に対して所定の範囲内でずれて配置された場合には当該ダミーパターンは所定のデザインルールを満たさない。

(もっと読む)

素子配置配線装置、半導体集積回路の製造方法、素子配置配線方法、制御プログラム、および記録媒体

【課題】半導体集積回路の設計の早い段階で遅延改善を行うことができ、しかも、回路素子間の配線の自己発熱による温度上昇を考慮して回路素子間の配線の正確な抵抗値を求めることができ、これにより配線に対するリピータ挿入による遅延削減を効果的に行う。

【解決手段】素子配置配線装置100において、半導体集積回路の各配線の平均温度を考慮して該各配線での信号遅延時間を導出する信号遅延時間導出手段101と、該各配線での平均温度を考慮した信号遅延時間に基づいて、該配線に該配線での信号遅延時間が低減されるよう挿入されるリピータセルの最適サイズおよび最適個数を決定するリピータ最適値決定手段100aとを備え、半導体集積回路の基本レイアウトを、該リピータセルの挿入が必要な配線に、該決定されたサイズのリピータが該決定された個数だけ挿入されたレイアウトに変更する。

(もっと読む)

半導体集積回路

【課題】回路セルの電源分岐線の太さに無駄を抑制して、その分セル面積を縮小する。

【解決手段】電源制御対象の回路セル10と、起動後は電源供給が常時オンの回路セル群(50,50A)とを含むセル配置領域A1と、セル配置領域A1に配置される基準電圧幹線VSSと、セル配置領域A1内で基準電圧幹線VSSから分岐して配置されるVSS上層分岐線72およびVSS下層分岐線71と、を有する。回路セル10が、電源スイッチM1,M2とVSS上層分岐線72を介して基準電圧幹線VSSに接続されている。常時オンの回路セル50A(分岐接続回路セル)が、共通のVSS下層分岐線71を介して基準電圧幹線VSSに接続され、他の常時オンの回路セル50(個別接続回路セル)が、個別の接続線51によって基準電圧幹線VSSに接続されている。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】回路動作の信頼性向上および設計期間の短縮化を図ること。

【解決手段】設計対象回路の配線領域内の各ネットグループ固有の始点座標から終点座標に辿り着くまでの各ネットグループ固有の配線幅の配線経路を探索する。そして、探索された配線経路間で相互に交差関係を有するネットグループの組み合わせを検出し、検出された組み合わせのネットグループがそれぞれ異なる配線層に割り当てられるように、設計対象回路に与えられた複数の配線層の中から各ネットグループに割り当てる配線層を決定し、決定された決定結果を出力する。

(もっと読む)

半導体装置

【課題】入出力部と機能ブロック間、機能ブロックと機能ブロック間の狭い領域にセルを配置する場合にも、信号配線領域を確保しつつ、基板バイアス制御を行う。

【解決手段】半導体装置1は、それぞれが所定の機能を有する複数の機能ブロック14a〜14cと、信号線が設けられる基板上における配線領域18a、18bとを有する。また、半導体装置1は、配線領域18a、18bに配置され、及び信号線の途中に設けられ、それぞれが基板バイアス電位により動作する複数のスタンダードセル16と、配線領域18a、18bに信号線の配線方向に平行に配置され、及び複数のスタンダードセル16のそれぞれに対応して設けられ、それぞれが基板バイアス電位を対応する各スタンダードセル16に供給するための複数の基板コンタクトセル17とを有する。

(もっと読む)

半導体集積回路、および半導体集積回路のレイアウト方法

【課題】消費電力及びクロックスキューが小さく、かつ、大規模な半導体集積回路においても、クロック信号を供給するクロック駆動セルの負荷容量が小さいクロック分配回路を提供する。

【解決手段】機能ブロック100の領域10,20にそれぞれ、第1の方向に延びるクロック基幹配線11,21、第2の方向に延びるクロック支線配線群12,22、およびクロック駆動セル13,23が、それぞれ配置されている。領域10のクロック同期セル群14は、クロック基幹配線11またはクロック支線配線群12と接続されている一方、領域20のクロック同期セル群24は、クロック基幹配線21またはクロック支線配線群22と接続されている。クロック基幹配線11,21は、第1の方向においてクロック支線配線群12,22が存在する範囲に限って延びている。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、外部からの電源が供給される電源配線と回路毎に設けられる電源配線とを接続するスイッチトランジスタにより回路の配置に大きな制約が課される問題があった。

【解決手段】本発明にかかる半導体装置の一態様は、半導体基板1と、半導体基板1上に形成されるトランジスタ(セル)に電源を供給する第1の下層配線と、第1の下層配線層に接続され、第1の下層配線よりも電流許容量の大きい第1の中間層配線と、第1の中間層配線よりも上層に配置され、外部から入力される電源を受ける上層配線と、を有し、第1の中間層配線は、半導体基板1上に形成されたスイッチ回路SWを介して上層配線に接続されるものである。

(もっと読む)

半導体集積回路

【課題】大規模マクロセルが搭載されていても、入出力用セルと論理ゲートセルとの配線長を短くすることができる半導体集積回路を提供する。

【解決手段】半導体集積回路のチップ100には、チップの外周部領域にチップの辺に沿って大規模マクロセル1a〜1jが配置され、その大規模マクロセルの配置領域よりも内側の入出力セル配置領域20に入出力セル2が配置され、その入出力セル配置領域20よりも内側の論理セル配置領域30に論理セル3が配置される。

(もっと読む)

半導体集積回路の設計方法と設計装置並びにプログラム

【課題】スタンダードセルの設計方式を用いて、品質の高いレイアウトを、短時間で作成することを可能とする設計方法と装置の提供。

【解決手段】

回路図情報(11)を入力し、回路図情報に対してセルの相対的な配置順序を自動的に決定し(12)、前記回路図情報に付与された配置順序に従ってセルを相対的な位置関係に自動配置する(13)。

(もっと読む)

レイアウト設計装置、レイアウト設計プログラム、および記録媒体

【課題】LSIチップの無駄な電力消費の抑制およびレイアウト設計期間の短縮化を図ること。

【解決手段】未配置位置511には、ダミーFF701が配置されている。このダミーFF701は、未配置位置511に隣接配置されたFF504、505間をバイパスしてスキャン信号を伝搬させるバイパス素子であり、他のFF501〜508のような信号処理はおこなわない。この配置処理により、分断されていたスキャン信号線500を、ダミーFF701、702によって接続することができる。

(もっと読む)

回路設計検証方法

【課題】漏れがない設計検証を、作業者の負担を軽減して行うことができる回路設計検証方法を提供する。

【解決手段】ライブラリ3にセルを登録する場合、標準セルの回路素子を製品の仕様に応じて変更したものを特殊セル4として登録し、特殊セル4のGDSファイルについて素子のサイズを抽出する際に、バイポーラトランジスタ及びダイオードについては、セル単体GDSファイル5を作成すると共に、当該セルのデータとセル名とに基づいてセル単位でLVSを実行するための分離スクリプトを作成すると、その分離スクリプトに基づいてLVS用のインクルードファイルを生成する。

(もっと読む)

201 - 220 / 595

[ Back to top ]