Fターム[5F064CC06]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | トランジスタ (1,639) | FET (1,516)

Fターム[5F064CC06]の下位に属するFターム

JFET (4)

ショットキFET (1)

MOS−FET(MISも含む) (1,456)

ディプレッション、エンハンスメント型の特定 (6)

Fターム[5F064CC06]に分類される特許

41 - 49 / 49

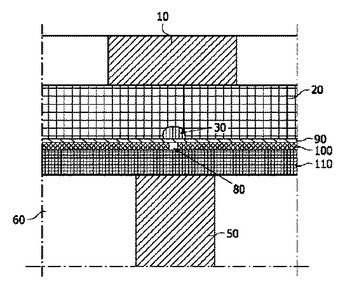

熱電プログラマブル装置のアンチヒューズ

熱プログラマブルメモリは、熱プログラマブル抵抗材料、好適には、相変化材料のプログラマブル素子(20)と、プログラマブル材料に隣接するように配置された破壊可能な又は破壊されたアンチヒューズ(80)とを有する。そのような破壊されたアンチヒューズは、製造中に誘電体に小さな孔を形成するよう高電圧を短時間誘電体の両端間に印加できるようにするために導電層(90,110)に包囲された誘電層(100)から有して、材料をプログラミングする際のきわめて小さいヒータとして用いることができる小さい導通経路を形成することができる。孔による電流の制限のために、高抵抗状態に切り替えるために加熱する必要がある材料の量が非常に少なくなる。その結果、プログラム電力を低くすることができる。  (もっと読む)

(もっと読む)

パターンレイアウト方法、その装置およびそのプログラム

【課題】液晶表示装置用の液晶アレイパターンを効率良く短時間で整列配置できるパターンレイアウト方法を提供する。

【解決手段】整列対象セル群の配線情報を配置して、見本セル群と整列対象セル群のセル名とを比較して一致か確認する。見本セルの見本座標と整列対象セル群の座標に基づいて整列対象セル群を見本座標に整列する。液晶アレイパターンのパターンレイアウトが効率的にできる。液晶アレイパターンの設計時間の短期間化を実現できる。横展開設計時のCAD上に描画された液晶アレイパターンの整列配置を効率的にできる。

(もっと読む)

予備リソースを備えた集積回路

【課題】電力を無駄にしない予備リソースを提供する。

【解決手段】一実施形態において、集積回路チップ(100)は、半導体基板(102)と、該半導体基板上に形成された金属層(106)と、未使用の予備リソース(400、500、600)とを備える。該予備リソースは、アースか又は供給電圧へと接続され、それにより、該リソースを介して電流が流れなくなり、且つ、該リソースによって電力が浪費されなくなる。該予備リソースを、チップの動作を修正するために、集積回路内へと接続することができる。

(もっと読む)

半導体装置、ICカード、ICタグ、RFID、トランスポンダ、紙幣、有価証券類、パスポート、電子機器、バッグ及び衣類

【課題】 IDチップに用いる半導体装置において、役割が終了したり、失効したときにその後の動作を停止する半導体装置を提供することを課題とする。

【解決手段】 本発明は、絶縁基板上にアンテナ回路と、電圧検出回路と、電流増幅回路と、信号処理回路と、ヒューズとを有し、アンテナ回路に大電力が印加されたときに、電圧検出回路にて電圧を検出し、その電流に応じた電流を電流増幅回路で増幅し、ヒューズを溶断する。また、アンチヒューズが用いられる時は過大な電圧を加えて、アンチヒューズを短絡させる。このように信号処理回路の動作を停止させ、役割が終了した、または失効したときに無効とする機能を有する半導体装置であることを特徴とする。

(もっと読む)

表示装置

【課題】

表示装置において、機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置及び表示装置を提供する。

【解決手段】

本発明は、薄膜トランジスタにより構成される機能回路を同一基板上に有する表示装置であって、前記機能回路に電源電圧を供給する電源配線及び接地電圧を供給する接地配線が格子状に配置されていることを特徴とする表示装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、の電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

半導体装置

【課題】 半導体装置の冗長用ヒューズの切断面で発生するESDサージから内部回路のトランジスタを保護することを目的とする。

【解決手段】 第1導電型不純物が添加された半導体基板と、前記半導体基板表面に形成された絶縁膜と、前記絶縁膜上に形成されたヒューズと、前記ヒューズと電気的に接続され、かつ第2導電型不純物が添加されて前記半導体基板表面に形成された第1拡散層と、

基板電位に接続され、かつ第1導電型不純物が、前記半導体基板に添加された前記第1導電型不純物よりも高濃度に添加されて前記半導体基板表面に形成された第2拡散層であって、前記第1拡散層、前記半導体基板とともにダイオードを構成する前記第2拡散層と、前記第1拡散層に電気的に接続されたトランジスタとを備えることを特徴とする半導体装置。

(もっと読む)

薄膜トランジスタ回路、薄膜トランジスタ回路の設計方法、薄膜トランジスタ回路の設計プログラム、設計プログラム記録媒体、設計ライブラリデータベース、および表示装置

【課題】結晶化半導体薄膜に対して適正かつ効率的なフォトマスクの作成を可能にする。

【解決手段】薄膜トランジスタ回路は各々所定サイズを越える結晶粒SXを収容する複数の結晶粒規定領域10に2次元的に区画される結晶化半導体薄膜5と、各々のチャネル領域CHが対応結晶粒規定領域10内の中央に配置される複数の薄膜トランジスタと、複数の薄膜トランジスタを相互接続する配線部とを備える。

(もっと読む)

半導体装置及びその製造方法

並列接続されているトランジスタTr1、Tr2、Tr3のゲート電極1−1、2−1、3−1のゲート幅、及び、隣接し合うゲート電極間の距離が異なり、また、ソース領域やドレイン領域の対応するゲート電極のゲート幅に沿う方向の長さや面積がトランジスタTr1、Tr2、Tr3で種々異なる値を持っている。したがって、同一のトランジスタ群内のトランジスタTr1、Tr2、Tr3間でゲート長などの特性の相関が低下し、それによって、複数のトランジスタ群間における特性のばらつきが小さくなる。  (もっと読む)

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】半導体素子の発熱に起因する半導体集積回路装置の温度上昇を低減する。

【解決手段】多層配線構造を備えた半導体集積回路装置において、多層配線構造を構成する接続孔及び金属配線層と同じ導電材料からなり、信号伝送用の接続孔及び金属配線層(領域C参照)とは異なる経路で上層側に延びる熱伝導部33,35,37を備えている(領域A,E,F参照)。領域Aにおいて、完全空乏型SOIトランジスタのゲート動作により発生した熱は、コンタクト層19、メタル配線層M1、ビア層21、メタル配線層M2に伝導され、さらに熱伝導部33を介して最上層のメタル配線層M6まで伝導され、絶縁層17の上面側から放熱される。これにより、半導体集積回路装置の温度上昇を低減することができる。

(もっと読む)

41 - 49 / 49

[ Back to top ]