Fターム[5F064CC09]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | トランジスタ (1,639) | FET (1,516) | MOS−FET(MISも含む) (1,456)

Fターム[5F064CC09]の下位に属するFターム

ポリシリコンゲートを有するもの (142)

CMOS (629)

Fターム[5F064CC09]に分類される特許

1 - 20 / 685

半導体集積回路

半導体集積回路

【課題】回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

(もっと読む)

半導体集積回路およびそれを用いた光センサ機器

【課題】修正前の特性値がその特性値の出現頻度分布における平均値±2×(標準偏差)の範囲に入る製造品に対するヒューズ溶断本数を少なくする。

【解決手段】素子アレイ14には抵抗アレイを設け、特性値の分布の平均値を素子アレイ14で得られる合成抵抗値の中央値に対応付け、トリミング情報生成回路12における上記中央値より大きい合成抵抗値に対応するトリミング情報の配列を、10進数で「15」〜「8」の降順に、上記中央値以下の合成抵抗値に対応するトリミング情報の配列を、10進数で「0」〜「7」の昇順に設定する。変換回路13は、トリミング情報生成回路12からのトリミング情報を変換して、素子アレイ14の抵抗アレイから各合成抵抗値を得るためにオフする抵抗を選択する素子選択情報を生成する。こうして、上記分布における「平均値±2σ」の範囲内に対応付けられトリミング情報を生成する場合のヒューズ溶断数を大幅に削減する。

(もっと読む)

半導体集積回路の製造方法

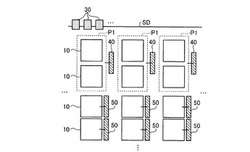

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

トリミング回路及び調整回路

【課題】ヒューズ素子の仮想切断を可能にすると共に、高電圧又は大電流によるヒューズ溶断の際に、周辺回路を破損する確率も低減できる信頼性の高いトリミング回路を提供する。

【解決手段】ヒューズトリミングを行うための回路であって、トリミングヒューズと、

前記トリミングヒューズに接続されるトリミング用のパッド端子と、仮想切断時に制御信号を入力するテスト端子と、入力端子の一方が前記テスト端子に接続され他方が前記トリミングヒューズに接続され、入力された制御信号に応じた制御信号を出力する制御回路と、を有し、前記トリミングヒューズの切断により、前記制御回路の他方の入力端子がGNDレベルへプルダウンする手段を備えたことを特徴とする。

(もっと読む)

ESD耐量検証方法及びESD耐量検証装置

【課題】 ESD耐量の低いパス及びその原因素子を安易且つ良好に特定できる検証方法及び検証装置を提供する。

【解決手段】 設計用回路データから2つの検証対象端子とその間に接続される検証対象素子を特定し、電流方向を設定し、検証対象素子の夫々を識別情報、電流方向別の特性情報及び耐量情報を記憶した素子シンボル情報を備える素子シンボルで表した等価回路データを作成し、2ノード間の特性情報及び耐量情報を記憶可能な分岐点シンボルを用い、検証対象端子に対応する分岐点シンボルを頂点とし、等価回路データをツリー構造データに変換し、素子シンボル情報に基づいて分岐点シンボル情報を作成し、頂点の分岐点シンボルの耐量情報が基準耐量以下の場合に、耐量情報に基づいて耐性が最も低い最低耐量経路と耐量制限シンボルを特定し、当該耐量制限シンボルに対応する設計用回路データの素子を特定する。

(もっと読む)

高耐圧MOSFETの回路シミュレーション用モデルの作成方法と装置並びにプログラム

【課題】高耐圧MOSFETのモデルにおいて、ドレイン電流の精度を広いバイアス範囲で得ることができ、シミュレーションの精度を向上させる。

【解決手段】ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、ソース領域のソース拡散層の幅とウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFET1、2と、第2のMOSFET2のソースに一端が接続された第1の可変抵抗素子3を備え、第2のMOSFET2のソースと第1の可変抵抗素子3の他端との接続点をソース端子Sとし、第1及び第2のMOSFETの共通接続したドレイン、共通接続したゲート、共通接続したバックゲートをそれぞれドレイン端子D、ゲート端子G、バックゲート端子Bとするモデルを作成し、モデリング対象の高耐圧MOSFETの電気特性データに基づき、第1の可変抵抗素子3の抵抗値を調整する。

(もっと読む)

レイアウトデータ作成装置及び半導体装置

【課題】従来のようにピラーの分割単位が小数点数とならず、単位ピラートランジスタのピラーの径の変更を行う必要が無くなり、半導体装置を製造するプロセスを複雑化することなく、ピラー型のトランジスタによりセルを、セルロウ内に効率的に配置するレイアウトデータ作成装置を提供する。

【解決手段】本発明のレイアウトデータ作成装置は、集積回路における複数の単位ピラー型トランジスタで構成されるピラー型トランジスタを、配置領域内に配置可能な単位ピラー型トランジスタの整数単位に分割し、配置領域内に配置するサブピラー型トランジスタを生成するトランジスタ調整部2を備えている。

(もっと読む)

半導体記憶素子及び半導体記憶装置

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

半導体装置

【課題】配線間の寄生容量を削減可能にした半導体装置を提供する。

【解決手段】X方向に配列する複数のトランジスタについて、夫々が、対応するダミーゲートDG1,DG2を挟む複数のソース拡散層S1,S2に接続する第2及び第3の金属配線M12,M13は、2つのS1,2つのS2に夫々接続する複数の第1のビアV1の両方を含む第1の幅L1と、V1を含まず、L1よりも短い第2の幅L2と、を有する。ドレイン拡散層D1に接続する第1の金属配線M11と、M12との間、並びにM11及びM13の間の夫々は、L1に対応する第1のギャップSP1と、L2に対応する、L1よりも大きな第2のギャップSP2と、を有する。好ましくは、M11〜M13の夫々と第2のビアV2を介して接続される第4〜第6の金属配線M24〜M26の夫々は、L1よりも短い第3の幅L3を有する。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置、パラメータ最適化方法、及びプログラム

【課題】トランジスタの容量の各成分や配線容量を分離してパラメータを最適化することが可能な半導体装置、パラメータ最適化方法、及びプログラムを提供すること。

【解決手段】MOSトランジスタから構成されたプリミティブゲート回路11aを奇数段でリング状に結合した第1リングオシレータ部11の各前記プリミティブゲート回路の出力部と電気的に接続された負荷部12となる第1配線を有する配線負荷パターンと、第2リングオシレータ部の各プリミティブゲート回路の出力部が第2配線を介して負荷部となるMOSトランジスタのゲートに電気的に接続された複数のゲート負荷パターンと、第3リングオシレータ部の各プリミティブゲート回路の出力部が第3配線を介して負荷部となる拡散層に電気的に接続された複数の拡散層負荷パターンと、を備え、複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、複数の拡散層負荷パターンは、パターンごとに容量負荷が異なる。

(もっと読む)

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

半導体集積回路装置

【課題】過電圧がLSIの電源端子に印加されたことを確認できるようにする。

【解決手段】半導体集積回路装置(10)は、内部回路(11)と、上記内部回路に電源電圧を供給するための電源端子(15,16)とを含む。このとき、上記内部回路の電源電圧として想定されるレベルを越える電圧(過電圧)が上記電源端子に印加された事実を記録するための過電圧印加情報記録回路(12)を設ける。過電圧印加情報記録回路には、過電圧が上記電源端子に印加された事実が記録されているため、それに基づいて、過電圧がLSIの電源端子に印加されたことを確認することができる。

(もっと読む)

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

回路動作の検証装置及び回路動作の検証方法

【課題】電圧規格や電流規格を満たさない箇所があった場合に、その影響を反映させて検証を行うことができる回路動作の検証装置を提供する。

【解決手段】回路動作の検証装置は、結線情報4と、定格情報6とを用い、回路に入力する信号パターン7が与えられると、その入力パターン7に基づいて回路動作を検証する(S1〜S5)。そして、検証の結果、回路素子に印加される電圧や通電される電流等が定格値を超えることで破壊に至る回路素子が存在すると、当該回路素子を破壊の態様に応じた破壊状態モデルに置換し(S6)、破壊状態モデルに置換した回路について検証を継続する。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

基板導通を利用した積重ねダイ式の構成をもつ集積回路

【課題】積重ねダイ式の集積回路で使用するのに適した基板導通技術を提供すること。

【解決手段】集積回路が、積み重ねて配置された複数の集積回路のダイを備え、積重ねの頂部のダイを除く任意のダイが、それ自身および追加のダイ少なくとも1つのための電流を基板導通により担持する。1つの形態では、積重ねの底部のダイを除く各ダイが、下側のダイのバスまたはその他の電源導体を介して基板導通によりその電源電流を担持する。

(もっと読む)

1 - 20 / 685

[ Back to top ]