Fターム[5F064CC10]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | トランジスタ (1,639) | FET (1,516) | MOS−FET(MISも含む) (1,456) | ポリシリコンゲートを有するもの (142)

Fターム[5F064CC10]に分類される特許

1 - 20 / 142

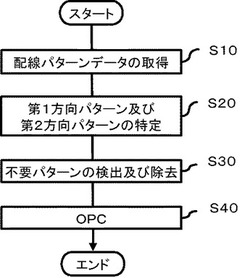

半導体装置の設計方法及び半導体装置の製造方法

【課題】半導体装置の歩留まりが低下することを抑制する。

【解決手段】配線パターンを示す配線パターンデータを取得する(ステップS10)。次いで、配線パターンデータを解析して、第1方向パターン及び第2方向パターンを特定する(ステップS20)。第1方向パターンは、第1の方向に延伸するパターンであり、第2方向パターンは、第1の方向に直交する方向に延伸するパターンである。次いで、第1方向パターと第2方向パターンの交点を検出する。そして、この交点から延伸するパターンのうち、ビア、コンタクト及び他のパターンのいずれにも接続していないパターンを不要パターンとして検出し、検出した不要パターンを除去する(ステップS30)。そしてその後、設計した配線パターンに対して光近接効果補正を行う(ステップS40)。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

半導体集積回路装置

【課題】標準論理セルのセル高さを縮小する。

【解決手段】第1,第2,第3の電源配線(WP1,WP2,WP3)および複数の第1の信号配線(WS1)は、半導体基板の上層に形成され、少なくとも1つの第2の信号配線(WS2)は、複数の第1の信号配線(WS1)の上層に形成される。第1および第2の電源配線(WP1,WP2)は、セル高さ方向に互いに離間してセル幅方向に延伸する。第3の電源配線(WP3)は、第1および第2の電源配線(WP1,WP2)の間をセル幅方向に延伸する。複数の第1の信号配線(WS1)は、第1,第2,第3の電源配線(WP1,WP2,WP3)から離間し、複数の回路要素(DF,GW)の少なくとも1つに電気的に接続される。少なくとも1つの第2の信号配線(WS2)は、セル幅方向に延伸し、複数の回路要素(DF,GW)および複数の第1の信号配線(WS1)の少なくとも1つに電気的に接続される。

(もっと読む)

半導体装置の製造方法

【課題】ロジック回路を含む半導体装置に関し、処理時間を短縮し製造コストを低減する。

【解決手段】ロジック回路の形成領域(114)は、所定の精度で光近接補正処理された第1領域(114b,170)と、所定の精度より低い精度で光近接補正処理された第2領域(114a,180)とを備える。特に第1領域(114b,170)は、トランジスタとして動作するゲート配線(172)を有し、第2領域(114a,180)は、トランジスタとして動作しないダミーレイアウト(182)を有する。

(もっと読む)

半導体装置の製造方法、半導体装置、設計方法、設計装置、及び、プログラム

【課題】集積度及び歩留まりの低下を抑制しつつ、アニール処理に起因した素子の特性ばらつきを軽減する。

【解決手段】半導体基板1上に素子2、3、5を形成する素子形成工程と、素子形成工程の後、半導体基板1上に、選択的に、半導体基板1よりも高い光吸収率を有するか、又は、半導体基板1への光の吸収率を向上させる機能を有する加熱安定化膜7を形成する加熱安定化膜形成工程と、加熱安定化膜7を有する面側から半導体基板1に光を照射し、半導体基板1に注入された不純物を活性化するアニール工程と、を有する半導体装置の製造方法。

(もっと読む)

不揮発プログラマブルロジックスイッチ

【課題】 誤動作を防ぐとともに、サイズが小さい不揮発プログラマブルロジックスイッチを提供すること。

【解決手段】 本発明の実施形態による不揮発プログラマブルロジックスイッチは、制御ゲートが第1の配線に接続され、第1のソースドレイン端が第2の配線に接続され、電荷を蓄積する膜を有する第1のメモリセルトランジスタと、制御ゲートが前記第1の配線に接続され、第3のソースドレイン端が前記第1のメモリセルトランジスタの第2のソースドレイン端に接続され、第4のソースドレイン端が第3の配線に接続され、電荷を蓄積する膜を有する第2のメモリセルトランジスタと、前記第1のメモリセルトランジスタの前記第2のソースドレイン端と前記第2のメモリセルトランジスタの前記第3のソースドレイン端にゲート電極が接続されたパストランジスタと、前記パストランジスタのウェルに基板電圧を印加する第1の基板電極を有する。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層211P上の半導体層212N,213N間に対応する領域に設けられた下層側の誘電体膜216および上層側の導電体膜217と、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bと、導電体膜217と電気的に接続された電極215Cとを有する。駆動対象の記憶素子21に対して、電極215B,215C間に所定の閾値以上の電圧V1を印加して、誘電体膜216の少なくとも一部分を絶縁破壊させて導電体膜217,半導体層213N間に電流を流し、半導体層212N,213N間の領域にフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】半導体集積回路の遅延時間の変動を抑制すること。

【解決手段】回路設計支援装置1は、選択部1bと配置部1cとを有している。選択部1bは、設計対象の半導体集積回路モデルが備えるレジスタモデル2bにクロック信号を供給するクロック信号線の分岐点P1からレジスタモデル2bのクロック信号入力端子に至る第1の経路と、分岐点P1からレジスタモデル2bのデータ信号入力端子に至る第2の経路の、配線に関する物理パラメータの差分値に基づいて、物理パラメータが異なる配線負荷を有する複数の遅延回路モデルから遅延回路モデルBを選択する。配置部1cは、選択された遅延回路モデルBをデータ信号入力端子に接続されるデータ信号線に配置する。

(もっと読む)

半導体集積回路

【課題】動作特性を劣化させることなくセル面積の縮小化を図ったマクロセル構造の半導体集積回路を得る。

【解決手段】Pウェル領域1の中央部にNウェル領域2が形成される。Nウェル領域2の平面視上方及び下方にN活性領域4a及び4bが形成される。Pウェル領域1内においてN活性領域4aの平面視上方及び下方にPウェルコンタクト領域5a及び5bが横方向に延びて形成される。Nウェル領域2内において中央にP活性領域3が形成され、P活性領域3の左横に縦方向に延びてNウェルコンタクト領域6が形成される。P活性領域3の中心部を横断するVDD用メタル配線層14の一部であるウェルコンタクト部14cは、Nウェルコンタクト領域6上にも形成され、ウェルコンタクト部14cとNウェルコンタクト領域6とは複数のコンタクトホール21を介して電気的に接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

不揮発性プログラマブルロジックスイッチおよび半導体集積回路

【課題】回路サイズを減少させることを可能にする。

【解決手段】素子分離領域102によって分離された、隣接する第1導電型の第1半導体領域101aおよび第2導電型の第2半導体領域101cと、第1半導体領域101a上に設けられた不揮発性メモリセルトランジスタ10と、第2半導体領域101c上に設けられ、第1半導体領域101aに設けられた第1ドレイン領域10bと電気的に接続されたゲート電極20C2とを有するパストランジスタ20と、第1半導体領域101aに設けられ第1半導体領域に基板バイアスを印加する第1電極8と、第2半導体領域101cに設けられ第2半導体領域に基板バイアスを印加する第2電極9と、を備えている。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、ヒューズの微細化を図ること。

【解決手段】シリコン基板1に素子分離絶縁膜2を形成する工程と、素子分離絶縁膜2の上に第1の絶縁膜13を形成する工程と、第1の絶縁膜13にスリット13xを形成する工程と、スリット13xを通じて素子分離絶縁膜2をウエットエッチングして凹部2bを形成する工程と、凹部2bとスリット13xの各々の内面に第2の絶縁膜24を形成することにより、第2の絶縁膜24によりスリット13xを塞ぎつつ、凹部2b内にボイド24aを形成する工程と、ボイド24aの上の第2の絶縁膜24にホール25bを形成し、ホール25b内にボイド24aを露出させる工程と、露出したボイド24aとホール25bのそれぞれの中に導電膜27を形成することによりヒューズFを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】本発明は、工程を増やすこと無く、ヒューズカット時間を短縮することができる半導体装置を提供する。

【解決手段】半導体装置は、ヒューズ配線(10)と、加熱用配線(21、22)とを具備し、ヒューズ配線(10)と加熱配線(21、22)とに電圧を印加してヒューズ配線の溶断部を切断する。ヒューズ配線(10)は、回路素子を形成する配線層と同じ層に形成され、電気的に切断されうる溶断部を備える。加熱用配線(21、22)は、回路素子を形成する配線層と同じ層のうちのヒューズ配線(10)より上層の配線層に絶縁層を介して溶断部を複数回横断するように形成され、溶断部の配線幅より広い配線幅を有して溶断部を加熱する。

(もっと読む)

半導体装置

【課題】低消費電力かつ低占有面積で、パッケージ実装後においてもプログラムを行なうことができるヒューズ素子を備えるヒューズプログラム回路を実現する。

【解決手段】ヒューズプログラム回路(FPK1−FPKn)において、ヒューズ素子FSを、多層メタル配線の第3層以上のメタル配線(M(i))を用いて実現する。各ヒューズプログラム回路において、スキャンフリップフロップ(FSSRおよびPSR)を用いてプログラム情報およびヒューズ選択情報を順次転送して、選択的に、1本ずつヒューズを電気的に切断する。

(もっと読む)

半導体装置の設計方法、設計支援装置

【課題】ランプアニール工程での基板の温度ばらつきを抑制する。

【解決手段】半導体チップ(22)に導入、配置される複数の回路ブロック(A1〜E6)の初期レイアウト(31)を決定する。複数の回路ブロック(A1〜E6)の各々に対し、製造時にアニール用光源から照射される光の影響を受ける受光面を特定する。複数の回路ブロック(A1〜E6)の各々の面積に対する受光面の面積の比率を、受光面積率として算出する。初期レイアウトを、面積が均等な複数の領域の集合(A1〜E6、A2’、B2’、C5’、C6’、D5’、D6’、E3’、E4’)として特定する。基準ブロックの周辺の領域を周辺ブロックとして特定し、基準ブロックの受光面積率と周辺ブロックの受光面積率との和を周辺和とする。複数の領域の各々の周辺和のばらつきが最小となるように、複数の回路ブロックのレイアウトを変更する。

(もっと読む)

1 - 20 / 142

[ Back to top ]