Fターム[5F064DD14]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 素子、セル、ブロックの位置、座標 (576)

Fターム[5F064DD14]の下位に属するFターム

対称性 (163)

Fターム[5F064DD14]に分類される特許

81 - 100 / 413

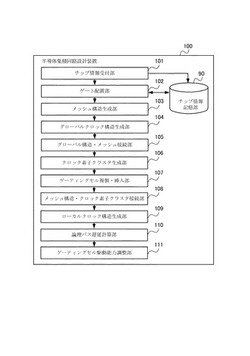

半導体集積回路の設計方法、設計装置およびプログラム

【課題】製造バラつきの下で、クロックスキューの最小化しつつ、クロック信号部での消費電力を最小化する半導体集積回路の設計方法、設計装置および、コンピュータプログラムを提供する。

【解決手段】メッシュ配線構造を駆動するバッファツリーを生成するグローバルクロック構造生成部104と、クロック素子の配置分布とクロックゲーティング構造を考慮してクラスタを生成するクロック素子クラスタ生成部106と、そのクラスタに含まれるクロック素子が属するゲーティッド回路にクロック信号を分配するゲーティングセルを複製して、クラスタを駆動するゲーティングセルとして挿入するゲーティングセル複製・挿入部107と、ローカルクロック構造生成部109と、タイミング解析結果に基づき、クロック素子クラスタを駆動するゲーティングセルの駆動能力を調整するゲーティングセル駆動能力調整部111と、を備える。

(もっと読む)

半導体集積回路の設計方法、設計支援プログラム、設計支援装置

【課題】レイアウト変更に有効利用できる空き領域を効率的に確保する。

【解決手段】本発明による半導体集積回路の設計方法は、事前に設計されたレイアウトパタンデータから縮小対象の第1セルを選択するステップと、第1セルに隣接する空き領域の面積を算出するステップと、空き領域の面積に応じて選択された一辺を固定し、前記一辺に対向する他の辺を変動させて前記第1セルを縮小するステップとを具備する。

(もっと読む)

セルライブラリ、レイアウト方法およびレイアウト装置

【課題】欠陥が発生しにくいレイアウト図を簡単な処理で作成する。

【解決手段】半導体集積回路のレイアウト設計に用いられる、単位機能を実現するセル毎の設計データのライブラリであるセルライブラリにおいて、セル毎の設計データは、セルが備える端部と、該端部を介して隣接するセルに欠陥を生じせしめやすいか否か、および隣接するセルから欠陥を生じせしめられやすいか否か、を示す属性値と、の対応付けである属性情報を夫々含む。

(もっと読む)

設計方法、露光用マスク、設計装置

【課題】疑似エラーの発生を抑制する。

【解決手段】設計装置は、設計データ21に含まれる回路パターンの光学的近接効果に対するアウターセリフパターンとインナーセリフパターンを生成し、それらを含む中間データ23を描画データ24に変換する。設計装置は、アウターセリフパターン,インナーセリフパターンを回路パターンと分離して配置した。そして、設計装置は、アウターセリフパターン,インナーセリフパターンを描画データ24から除去したチェック用描画データ26を生成し、そのチェック用描画データ26に含まれる描画用パターンの形状を検証ルールに従って検証する。

(もっと読む)

プリミティブセル及び半導体装置

【課題】従来のプリミティブセルでは、電源配線及び接地配線により構成される電流経路のループが大きく、当該電流経路のループに起因して発生するEMIノイズを十分に低減することができない問題があった。

【解決手段】本発明にかかるプリミティブセルは、内部回路10と、内部回路10に電源電圧を印加する電源配線12と、内部回路に接地電圧を印加する接地配線11と、を有し、電源配線12と接地配線11とがセルの外周辺のうちの一辺に偏在して配置される。

(もっと読む)

半導体集積回路のレイアウト設計方法、プログラム、及びレイアウト設計装置

【課題】チップサイズを縮小可能な半導体集積回路のレイアウト設計方法、プログラム、及びレイアウト設計装置を提供すること。

【解決手段】チップ内にY方向メタルデータを持つプリミティブセルが存在するか判定する工程(ステップB1)と、プリミティブセルが上下に隣接しているか判定する工程(ステップB3)と、各プリミティブセル内のY方向メタルデータを有する層が同じか判定する工程(ステップB4)と、各プリミティブセルのうち移動可能なスペースがあるプリミティブセルがあるか判定する工程(ステップB5)と、各判定を満たす場合に、各プリミティブセルの種類が同じか否かを判定する工程(ステップB6)と、各プリミティブセルの種類に応じてプリミティブセルのX座標の配置位置調整を行う工程(ステップB7、8)と、プリミティブセルの位置を固定する工程(ステップB9)と、を含む。

(もっと読む)

半導体集積回路のセル自動配置方法、装置、及びプログラム

【課題】製造工程の異なるセルを混在して配置する場合に、面積を大きくせずに配置する半導体集積回路のセル自動配置方法、自動配置装置、及びそれらのプログラムを提供する。

【解決手段】複数種類のセルの内、一種類のセルに同一種類のセルが隣接配置可能であり、異なる種類のセルの隣接配置が不可能な大きさの第1の外形を設定し、上記その他の種類のセルには、第1の外形が設定されるセルを含めセルの種類に係わらずセルを隣接配置することが可能なより大きい外形を設定するセル外形設定工程と、セル外形設定工程で設定した外形を有するセルを用いて複数種類のセルを自動配置するセル自動配置工程と、を備える。

(もっと読む)

ハードウェア支援配置を行うための方法および装置

標的デバイス上でシステムを設計するための方法を開示する。システム内の第1の複数の構成要素は、基準に基づいてコンピュータ支援設計(CAD)ツールによって配置されるように割り当てられる。システム内の第2の複数の構成要素は、基準に基づいてハードウェア配置ユニットによって配置されるように割り当てられる。CADツールおよびハードウェア配置ユニットからの配置結果は、標的デバイス上のシステムに対する配置解決法を生成するために使用される。他の実施形態が説明され、請求される。  (もっと読む)

(もっと読む)

半導体装置及びその設計方法並びに半導体装置の製造方法

【課題】良好な電気的特性を有する半導体装置及びその設計方法並びに半導体装置の製造方法を提供する。

【解決手段】第1のトランジスタが形成される第1の活性領域のパターンと、第2のトランジスタが形成される第2の活性領域のパターンとを配置するステップS2と、第1の活性領域及び第2の活性領域と交差するゲート配線のパターンを配置するステップS3と、第1の活性領域とゲート配線とが重なり合う領域である第1の領域を抽出するステップS4と、第1の活性領域を含む領域上に、圧縮応力膜のパターンを配置するステップS5とを有し、第2の活性領域を含む領域上に、圧縮応力膜に隣接する引っ張り応力膜のパターンを配置するステップS6とをコンピュータに実行させることにより、半導体装置のレイアウトパターンを取得する工程を有し、圧縮応力膜のパターンを配置するステップでは、第1の領域の縁部の位置に基づいて、圧縮応力膜のパターンの縁部の位置が設定される。

(もっと読む)

半導体装置

【課題】電源サブ幹線に接続された内部素子に異常電圧が印加される恐れを小さく

する。

【解決手段】VSSQ0パッド143と、静電耐圧非対応素子を含むセル配置領域1(301)と、静電耐圧非対応素子よりも高い耐圧性を有する静電耐圧対応素子を含むセル配置領域2(302)と、VSSQ0パッド143を介して外部から供給される電位を静電耐圧非対応素子に供給するVSSQサブ幹線351〜353と、VSSQ0パッド143とVSSQサブ幹線351〜353との最短距離よりも長い配線長を有し、VSSQ0パッド143に入力された電位をVSSQサブ幹線351〜353に対して印加する引き込み配線部(第1VSSQ引き込み配線331とVSSQメイン幹線321と第2VSSQ引き込み配線341とからなる配線部)とを備えている。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】トライアルレイアウトの結果を用いてフロアプランおよびセル配置の容易化を図ること。

【解決手段】モジュール1を例に挙げると、第1のネットリスト内のモジュール1と、第1のネットリストから改訂された第2のネットリスト内のモジュール1が、同一である。設計支援装置が、クロックツリーが未生成であり、かつ配置されたセル間が未配線である第1のネットリストに基づく第1のレイアウトデータ107から、モジュール1を特定する。そして、モジュール1をモジュール2として配置することで第1のレイアウトデータ107内のセル配置を流用して第2のレイアウトデータ600を生成する。また、第1のネットリスト内のモジュール2と第2のネットリスト内のモジュール2は、機能が同一であるが、機能を構成するセルが同一でないため、第1のレイアウトデータ107からモジュール2の配置領域が流用される。

(もっと読む)

設計支援プログラム、設計支援装置、設計支援方法、半導体素子、およびマクロ

【課題】マクロの向きが変更されても、マクロ内に配置されている複数のセルの向きおよびセル間の接続線が維持可能とし、向きの異なるマクロの生成の容易化を図ること。

【解決手段】設計支援装置は、複数の向きで配置されるマクロ内で用いられるセルのレイアウトデータから、セルの端子の配置位置を第1の端子の配置位置として検出する。設計支援装置は、複数の向きのうち、第1の端子が用いられる一の向きと異なる他の向きで用いられるセルの第2の端子の位置を、一の向きから他の向きへの変化量と第1の端子の配置位置に基づいて算出する。設計支援装置は、第1の端子の配置位置と、第2の端子の配置位置と、セルのレイアウトデータとを関連付ける。設計支援装置が、第2の端子の配置位置に端子を挿入する。具体的には、所定のビア層のビアが第2の端子の配置位置に挿入される。設計支援装置が、第1の端子と第2の端子とを接続する。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置のレイアウト方法

【課題】半導体装置の面積を大きくすることなくデカップリング容量を確保する。

【解決手段】機能ブロック12がPMOS領域14とNMOS領域16とに分割され、PMOS領域14には複数のP型のMOS−FET18、NMOS領域16には複数のN型のMOS−FET20が配置され、P型のMOS−FET18とN型のMOS−FET20とがそれぞれ対向して配置されており、P型のMOS−FET18及びN型のMOS−FET20が配置されていないPMOS領域14の空領域にデカップリング容量としてP型のMOS容量22を、NMOS領域16の空領域にN型のMOS容量24を、空領域の形状に応じた形状で形成して配置する。

(もっと読む)

設計方法

【課題】設計期間の短縮を図る。

【解決手段】設計装置11は、セルのレイアウト設計処理において、半導体装置のデザインに応じて、セルに含まれる端子に接続する信号配線を形成するための信号アクセストラック数を定量化した信号アクセス率を算出し、信号アクセス率に従って対応する端子のパターンを変更する。該信号アクセス率算出は、半導体装置の層数とロウ使用率に応じて設定された目標端子アクセス指数を記憶する記憶手段から、半導体装置に応じた目標端子アクセス指数を読み出し、前記セルの初期レイアウトデータを生成し、前記セルに含まれる端子を順次選択して着目端子とし、前記着目端子以外の端子のレイアウトをサイジングし、サイジングしたレイアウトの影響を受けない配線トラックを前記着目端子の信号アクセストラックとして抽出し、抽出した前記信号アクセストラックの数と前記目標端子アクセス指数とに基づいて、行う。

(もっと読む)

半導体装置の設計方法

【課題】TATを短縮すること。

【解決手段】本発明では、チップレイアウトデータ(22)に含まれる複数のゲートのうちの、アンテナ違反であるアンテナ違反ゲート群を表すアンテナ違反情報(20)をエラー残箇所ライブラリ(16)に格納する。チップレイアウトデータ(22)に対してリソグラフィシミュレーションを実施し、フォトレジスト露光後の予想レイアウトデータ(23)を生成する。エラー残箇所ライブラリ(16)を参照して、予想レイアウトデータ(23)に含まれる複数のゲートのうちの、アンテナ違反情報(20)が表すアンテナ違反ゲート群を選択する。アンテナ違反ゲート群の各々の面積に対して、そのアンテナ違反ゲート群に接続される配線の面積との比を示す算出値を算出する。その算出値が第1設定値から第2設定値の範囲である場合、アンテナ違反ゲート群の大きさを調整する。

(もっと読む)

半導体装置

半導体装置が半導体基板上のゲートを含む。ゲートの1つの側壁が少なくとも1つの突出部を含んでいてもよく、ゲートの反対側壁が少なくとも1つの凹部を含んでいてもよい。接触部が、ゲート上に配置された絶縁層を通して形成されている。接触部は、ゲートの少なくとも1つの突出部に少なくとも部分的に重なっている。金属層が絶縁層上に配置されている。金属層は、ゲートの第1の側に移動した第1の構造を含む。接触部が絶縁層を通して第1の構造をゲートに電気的に連結するように、第1の構造は接触部に少なくとも部分的に重なっている。 (もっと読む)

半導体デバイスのソフトエラー率の検証方法

【課題】半導体デバイスの宇宙線中性子に起因する故障に対する耐性を短期間で確保するための宇宙線中性子ソフトエラーの解析する半導体デバイスのソフトエラー率の検証方法を提供する。

【解決手段】ユニーク番号を設定した各セルに対して、セル毎(ごと)にセル個別パラメータを登録し、乱数に基づき中性子による核破砕反応発生座標の計算を行い、生成する2次イオンの核種・エネルギー・進行方向を計算し、セル内のセル種類毎パラメータに含まれる敏感領域情報と計算した2次イオンの核種・エネルギー・飛行方向から、2次イオンの飛跡計算に基づきセル単位での記憶ノード反転エラー発生とSETパルス発生を計算し、計算したセル単位での記憶ノード反転またはSETパルスが、半導体デバイス上のロジック回路全体でソフトエラーとして顕在化するかの判定を行い、ソフトエラーとして顕在化した場合に、エラー数としてカウントし、ソフトエラー率を計算する。

(もっと読む)

半導体装置

【課題】チャネル形成領域が素子分離領域から受けるストレスを、チャネル幅方向において均一化させる。

【解決手段】素子分離領域2と、素子分離領域2によって囲まれる、素子形成領域3とを具備する。素子形成領域3の外周形状は、第1方向に沿って延びる第1辺を有する。素子形成領域3は、第1トランジスタ領域6−1と、2方向において第1辺と第1トランジスタ領域6−1との間にあたる位置に配置された、第2トランジスタ領域6−2と、第1方向における第2トランジスタ領域6−2の側方に配置された、ダミー領域7とを備える。第1トランジスタ領域6−1は、第1チャネル形成領域4−1を有する。第2トランジスタ領域6−2は、第2チャネル形成領域4−2を有する。第1チャネル形成領域4−1は、第2チャネル形成領域4−2と非対向である非対向領域14を有する。ダミー領域7は、第2方向において非対向領域14と対向する。

(もっと読む)

集積回路装置及び電子機器

【課題】レイアウト面積の小面積化を図りながら表示制御用の信号を電気光学装置に供給できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置10は、集積回路装置10にスタックされる画像メモリー120のチップの第1のチップ辺SC1に沿って配置される第1のメモリーパッド群PMG1に接続される第1のパッド群PG1と、第3のチップ辺SC3に沿って配置される第2のメモリーパッド群PMG2に接続される第2のパッド群PG2と、電気光学装置の表示制御を行う制御部30と、表示制御用のデータ信号及び制御信号が出力される第3のパッド群PG3を含む。第1のパッド群PG1は、集積回路装置10の第1の辺SD1に沿って配置され、第2のパッド群PG2は、第1の辺SD1に対向する第3の辺SD3に沿って配置され、第3のパッド群PG3は、第1の辺SD1及び第3の辺SD3に交差する第2の辺SD2に沿って配置される。

(もっと読む)

半導体装置の設計方法及び半導体装置の製造方法

【課題】反射防止膜を形成せずとも、リソグラフィー時における下地からのハレーションの影響を除去し、所期の寸法のパターンを形成することを可能として、微細化の要請に応じた信頼性の高い半導体装置を実現する。

【解決手段】半導体装置の設計段階において、活性領域の第1のデータに対して、活性領域の少なくとも一部を露出する開口を有するレジストパターンの第2のデータを作成する際に、第2のデータの第1のデータと対向する部分について、予め作成された参照データを用いて、第1のデータとの対向辺の位置を補正する。

(もっと読む)

81 - 100 / 413

[ Back to top ]