Fターム[5F064DD14]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 素子、セル、ブロック等の配置、レイアウト (5,076) | 素子、セル、ブロックの位置、座標 (576)

Fターム[5F064DD14]の下位に属するFターム

対称性 (163)

Fターム[5F064DD14]に分類される特許

41 - 60 / 413

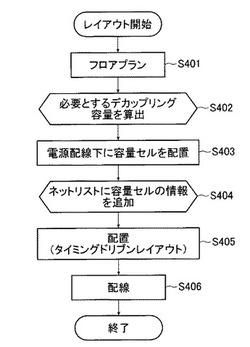

半導体集積回路の設計方法

【課題】設計フローの負荷を増大させることなく、それぞれの回路モジュールに必要十分な容量セルを、それぞれの回路モジュールに近接配置することができる半導体集積回路の設計方法を提供する。

【解決手段】本発明は、それぞれが複数の論理セルを含む複数の回路モジュールからなる半導体集積回路の設計方法であって、複数の回路モジュールのそれぞれの、複数の論理セルおよび複数の論理セルの端子間の接続の情報を記述するネットリストに、複数の論理セルに電源を供給する電源配線間に接続されるセルであり、複数の論理セルのいずれとも独立で、かつ、複数の論理セルの端子と接続される端子を持たない容量セルの記述を追加し、複数の論理セルおよび複数の容量セルのレイアウトデータが格納されたセルライブラリを備えた設計支援システムを利用して、回路モジュールのそれぞれに対応する、複数の論理セルおよび容量セルを配置する配置領域を設定し、複数の論理セルおよび容量セルを対応する配置領域内に配置する工程を含む。

(もっと読む)

半導体集積回路のレイアウト方法及びプログラム

【課題】パワードメインを自動作成する。

【解決手段】設計された回路が仕様を満たしているか否かを評価するための機能シミュレーション処理(9)と、上記機能シミュレーション処理の結果に基づいて、活性化タイミングが所定の範囲内で揃う論理ブロック毎にクラスタ分割することでパワードメインを得るクラスタ分割処理(10)とがコンピュータで行われる。これにより、パワードメインは、コンピュータで行われる処理によって得られるため、人手(設計者の手作業)によって求める場合に比べてパワードメインの最適化を図ることができる。

(もっと読む)

半導体集積回路のレイアウト設計方法、レイアウト設計装置及びレイアウト設計プログラム

【課題】長さが均一で直線的な配線を配置することができる半導体集積回路のレイアウト設計方法、レイアウト設計装置及びレイアウト設計プログラムを提供すること。

【解決手段】半導体集積回路のレイアウト設計方法は、第1の配線ピッチで配線を行う高速配線処理と、第1の配線ピッチより狭い第2の配線ピッチで配線を行う通常配線処理と、を有する。高速配線処理は、所定の高速バス配線上の複数のネットを第1の配線ピッチで略平行、かつ、略等長となるように自動配線を行う。通常配線処理は、高速配線処理より前に実行されない。

(もっと読む)

半導体集積回路、半導体チップ、及び半導体集積回路の設計手法

【課題】容易な設計により、小規模な構成でクロックスキューを抑制させる半導体集積回路を提供する。

【解決手段】ラッチ回路31〜316のデータ入力端子とデータビットの供給元PDとの間に、クロック信号CLLの供給元PCD及びラッチ回路のクロック入力端子間のクロック信号経路中に含まれている論理素子の個数と同一数だけ当該論理素子を直列に接続してなる第1遅延部51,52と、クロック信号経路中の配線の配線長に対応した配線遅延時間と同一長の遅延時間を有する第2遅延部53と、を備える。

(もっと読む)

集積回路内における、インターフェースデバイスの面積効率の良い配列

【課題】過度にシステムの中にスキューを増加させずに、増加した数の入力/出力デバイスを有するシステムを提供する。

【解決手段】論理回路を備えるコアと、処理コアからおよび処理コアへ信号を伝送するための、複数のインターフェースデバイスであって、2つのタイプのインターフェースデバイスを備える、複数のインターフェースデバイスと、コアに電力を送達するための、電力インターフェースデバイスである、1つのタイプと、コアと集積回路の外部のデバイスとの間で、データ信号を伝送するための信号インターフェースデバイスである、第2のタイプと、を備え、複数のインターフェースデバイスは、コアの外縁に向かう外側列、およびコアの中心により近い外側列の内側にある内側列の、2列に配設され、内側列は、2つのタイプのインターフェースデバイスのうちの一方を備え、外側列は、2つのタイプのインターフェースデバイスのうちの他方を備える、集積回路が開示される。

(もっと読む)

配線経路作成プログラム及び配線経路作成方法

【課題】ひとつのドライバと複数のドライバを配線するための配線経路を作成するプログラムに関して、総配線長が最小になるような配線経路を、それが複数存在する場合は、その中でも最大DR間配線長が一番小さくなるような配線経路を自動的に求める。

【解決手段】ドライバから各レシーバに向かう複数のベクトルに関して、任意の二つのベクトルからなるベクトルペアについて重複長さを求め、それが最大のものを選択ベクトルペアとする。その選択ベクトルペアについて、途中までを共通化する3種類の結合点を作ってベクトルを共通化し、3種類のベクトルパターンを得る。このような作業を繰り返し、ベクトルの共通化が終了した時点で、各ベクトルパターンを結線候補とする。結線候補の中で総配線長が最小のものを最適配線経路とする。それが複数ある場合は、最大DR間配線長が一番小さいものを最適配線経路とする。

(もっと読む)

集積回路のレイアウト設計方法、レイアウト設計装置、及び、プログラム

【課題】ACスペックの実現性を判断してからセル配置の処理に進むことにより、ACスペックを満たす為に再度セル配置をやり直す必要をなくす

【解決手段】レイアウト設計方法が、ACスペックとしてタイミング制約が定義された外部端子の配置を示す配置情報に基づいて、タイミングの基準となるクロック信号からの遅延時間の最小値である最小クロック遅延を、距離と遅延時間の対応関係を示す概略遅延算出テーブルを用いて見積もるステップ(S103)と、前記タイミング制約から、タイミング収束に必要な遅延時間の範囲である必要クロック遅延範囲の上限値を算出するステップ(S104)と、前記タイミング収束判定手段が、前記最小クロック遅延と前記必要クロック遅延範囲の上限値とから、前記ACスペックについてタイミング収束が可能かを、セル配置の前に判定するステップ(S105)とを具備している。

(もっと読む)

半導体装置

【課題】 データ保持回路を備えた半導体装置において、回路面積の低減及び動作速度の向上を図ること。

【解決手段】 本半導体装置100は、少なくとも1以上の不揮発性のメモリセルFCと、メモリセルFCへの書き込みデータ又はメモリセルFCからの読み出しデータを格納するラッチ回路30とを含み、メモリセルFC及びラッチ回路30がアレイ状に配置された複数の不揮発性メモリ回路20と、複数の不揮発性メモリ回路20におけるラッチ回路30のそれぞれに接続され、データを一時的に保持する複数のデータ保持回路10と、を備える。

(もっと読む)

半導体装置

【課題】電源分離領域内の配線密度を低下させる。

【解決手段】動作モードに応じて電源電圧が供給される電源線VVDDと、常に電源電圧が供給される電源線VDDと、通常モードで電源線VVDDを電源線VDDに接続するか、またはスリープモードで電源線VVDDを接地電位とするか、を切り替える電源切替回路(104、111、110が相当)と、電源線VVDDから電源供給されスリープモードでは動作を停止する第1回路ブロック101と、電源線VDDからの電源供給によって常に動作可能とする第2回路ブロック103と、電源線VVDDの電位が接地電位近傍にあるか否かにそれぞれ応じて、第2回路ブロック103の入力端をハイレベルにするか、第1回路ブロック101の出力信号を第2回路ブロック103に伝達可能とするか、を制御する入力制御回路(114、118が相当)と、を備える。

(もっと読む)

回路レイアウト設計システム、リーク対策セル、回路レイアウト設計方法及びプログラム

【課題】正規回路のタイミングを変えずに、未使用セル群の全てのセルのダイナミック電流及びチャンネルリーク電流を削減することができる回路レイアウト設計システムを提供する。

【解決手段】本発明の回路レイアウト設計システムは、レイアウトデータから、出力端子がオープン状態の未使用インバーターセルを検出する出力オープンセル検出部と、オープンセル検出部が検出した未使用インバーターセルの出力オープンセル情報を、出力オープンセル情報ファイルに格納する出力オープンセル情報抽出部と、レイアウトデータから、未使用インバーターセルを削除する出力オープンセル削除部と、出力オープンセル情報のセル名を、リーク対策セルに対応するセル名に変換した置換情報ファイルに格納するセル名変換部と、置換情報ファイルを参照して、レイアウトデータの未使用インバーターセルをリーク対策セルに置換する出力オープンセル置換部とを備える。

(もっと読む)

半導体装置

【課題】 半導体装置のレイアウト面積を大きくすることなく、内部電源回路の電流供給能力の向上を可能にする。

【解決手段】 半導体装置は、主領域12と、第1の方向に沿って主領域に形成された複数の第1の電源配線15と、第1の電源配線と交差しかつ電気的に接続されるように第2の方向に沿って主領域に形成された複数の第2の電源配線16と、第1の方向に関して主領域の一方の側に隣接する第1の隣接領域13に設けられ、第1の電源配線の一端にそれぞれ接続された第1の内部電源回路17と、第2の方向に関して主領域の一方の側に隣接する第2の隣接領域14に設けられ、複数の第2の電源配線のうち最も第1の電源配線の他端に近い電源配線の一端に接続された第2の内部電源回路18と、を備える。

(もっと読む)

プログラマブルゲートアレイおよびプログラマブルゲートアレイのプログラミング方法

【課題】配置配線をやり直す可能性を低減することができるプログラマブルゲートアレイおよびプログラマブルゲートアレイのプログラミング方法を提供する。

【解決手段】論理素子11を電源電位を供給するVCC12と接地電位を供給するGND13とに接続させる接続素子14を備え、論理素子11と接続素子14との間に、論理素子11と接続素子14とを接続可能な配線領域15が設けられ、配線領域15と接続素子14とを接続する専用ライン16が設けられていることを特徴とする。

(もっと読む)

半導体集積回路レイアウト設計装置、半導体集積回路レイアウト設計方法及びプログラム

【課題】半導体集積回路のレイアウト設計工程において、一定のセル配置品質を保証し、短時間でのセル配置を可能とする。

【解決手段】半導体集積回路を機能単位の各エリアに分解し、各エリアに含まれるセルを個別に配置することで半導体集積回路全体の配置を決定する。具体的には、回路情報から半導体集積回路内のセル間を接続する複数の信号線について、接続方向、入出力及び接続本数に関する信号線接続情報を抽出し、所定の規則に基づき、信号線接続情報からターゲットエリア内の全てのセルの配置を決定する。

(もっと読む)

半導体集積回路の設計方法

【課題】 半導体集積回路の電源EM及びスタティックIRドロップの解析と電源補強設計を改善する。

【解決手段】 一つの実施形態の半導体集積回路の設計方法では、電源配線のEM解析を行い、EM解析でEMエラーが発生した場合、EMエラーとなるレイヤ及び座標をチェックしてリストを格納し、半導体集積回路の抵抗網を抽出し、EMエラーとなるレイヤ及び座標を含む抵抗セグメントを全て削除してIRドロップ値が許容値を満足するかの第1の判定を行い、記第1の判定でIRドロップ値が許容値を満足する場合、EMによって半導体集積回路が動作不良とならない抵抗セグメントをレイアウトデータから削除する。

(もっと読む)

半導体チップおよびその設計方法

【課題】設計期間が短く、面積効率が高く、電源配線における電圧降下が小さな半導体チップと、その設計方法を提供する。

【解決手段】この半導体チップは、複数の電源ドメインD1〜D4に分割された内部回路2を備える。互いに異なる電流駆動能力を有する複数種類のレギュレータR1,R2を予め準備しておき、各電源領域毎に、当該電源領域の最大負荷電流を供給するために必要なレギュレータの種類と数を選択し、選択した1または2以上のレギュレータによって当該電源領域用の電源回路を構成する。したがって、設計期間が短くて済む。

(もっと読む)

クロック分配回路及びその回路を含む半導体回路装置

【課題】

半導体チップを製造する際の製造バラツキ又は半導体チップ内の半導体回路の動作条件による、複数の最終バッファから出力される複数のクロック間の位相差を軽減することが可能なクロック分配回路を提供することを目的とする。

【解決手段】

回路装置内に配置されたクロック分配回路であって、リング状のクロック配線と、前記クロック配線に接続し、自己発振により、前記クロック配線内に第1クロック信号を発生させる発振回路と、前記回路装置内において、2以上の場所それぞれに、配置され、第2クロック信号を出力する2以上の位相調整回路と、を備え、前記位相調整回路それぞれは、配置場所に応じた位相を有する前記第1クロック信号を受け取り、前記位相調整回路それぞれが受け取った前記第1クロック信号間の位相差よりも、前記位相調整回路それぞれが出力する前記第2クロック信号間の位相差を減じる調整を行うことを特徴とするクロック分配回路。

(もっと読む)

設計ライブラリデータベース

【課題】結晶化半導体薄膜に対して適正かつ効率的なフォトマスクの作成を可能にする。

【解決手段】1実施形態に係る設計ライブラリデータベースは、2次元的に区画して各々薄膜トランジスタのチャネル領域のサイズを超える複数の結晶粒規定領域が配置された結晶化半導体薄膜を用いる薄膜トランジスタ回路の設計ライブラリデータベースであって、各々のチャネル領域が単一の前記結晶粒規定領域内の固定位置に配置される2個以上の薄膜トランジスタおよび前記2個以上の薄膜トランジスタを相互接続する配線を含む様々な論理ゲート回路をそれぞれ表す複数のスタンダードセル、並びに前記様々な論理ゲート回路の様々な組み合わせをそれぞれ表す複数のマクロセルの少なくとも一方のセルのライブラリ、および前記複数の結晶粒規定領域が配置された結晶化アレイパターンのスタンダードセルのライブラリを含みハードディスクに登録される。

(もっと読む)

半導体集積回路装置

【課題】制御信号の系統を整理して、不定信号伝播防止回路等の検討漏れの危険性を回避し、さらに、自動化ツールへの搭載へ向けた検討を容易にし、また、チップ内部での電源遮断制御を容易化することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置において、各独立した電源領域AreaA〜AreaIごとに電源遮断の優先順を設け、優先順の高い回路がONしている場合にはそれより優先順の低い電源領域はOFFにできないという規則を設けて、設計方法の容易化を図る。また、各独立した電源領域AreaA〜AreaI内において、さらに別の電源を印加できる領域を設け、その領域に中継バッファ(リピータ)やクロックバッファ、情報退避用の情報保持ラッチを集積する。レイアウト上は、電源線の電流を分散させる目的でセルがロウ方向に並ぶ方向と垂直な方向にまとめてレイアウトすればよい。

(もっと読む)

半導体装置、電源スイッチの制御方法及びその設計方法

【課題】従来の半導体装置では、電源制御領域への突入電流の発生を抑制するためにチップ面積が増大する問題があった。

【解決手段】本発明にかかる半導体装置は、オン抵抗が大きな第1のスイッチトランジスタSWLと、オン抵抗が小さな第2のスイッチトランジスタSWSと、を有し、第1、第2のスイッチトランジスタSWL、SWSは、異なる領域に電流を供給し、第1のスイッチトランジスタSWSは、制御信号CONTを直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLは、前記制御信号を直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLのうち初段に配置される第2のスイッチトランジスタSWLは、第1のスイッチトランジスタSWSのうち最も後ろに配置される第1のスイッチトランジスタSWSが出力する制御信号CONTが入力される。

(もっと読む)

スタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法

【課題】複数のスタンダードセルを有する半導体装置のチップ面積をさらに小さくする。

【解決手段】半導体装置SD1は第1および第2スタンダードセルSC1,SC2を備える。第1スタンダードセルSC1は、拡散領域An11、拡散領域An11に対向する機能素子領域FE1、および金属層MT11を有する。第2スタンダードセルSC2は、拡散領域An11に連続する拡散領域An21、拡散領域An21に対向する機能素子領域FE2、ならびに拡散領域An21および機能素子領域FE2の間に形成された拡散領域CR21を有する。金属層MT11および機能素子領域FE2は、拡散領域An11、拡散領域An21、および拡散領域CR21通して電気的に接続される。

(もっと読む)

41 - 60 / 413

[ Back to top ]