Fターム[5F064DD41]の内容

ICの設計・製造(配線設計等) (42,086) | ICの構造(配線を除く) (6,653) | 付加的要素に関する構造 (884)

Fターム[5F064DD41]の下位に属するFターム

ボンディングパッドに関するもの (728)

識別マーク (32)

パッシベーション、保護膜 (111)

Fターム[5F064DD41]に分類される特許

1 - 13 / 13

半導体装置および半導体装置設計方法

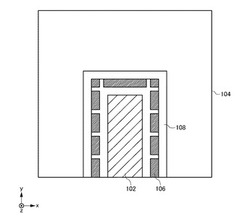

【課題】半導体基板においてダミーパターンの配置密度を高める。

【解決手段】半導体基板104には、配線パターン102とダミーパターン106がレイアウトされる。配線パターン102の周囲にはマージン領域がレイアウトされ、マージン領域の周囲にダミー領域がレイアウトされる。このダミー領域に、複数のダミーパターン106がレイアウトされる。ダミーパターン106は、ダミー領域の延伸方向に配列される。マージン領域とダミー領域は、配線パターン102を基準として交互にレイアウトされる。

(もっと読む)

半導体集積回路装置

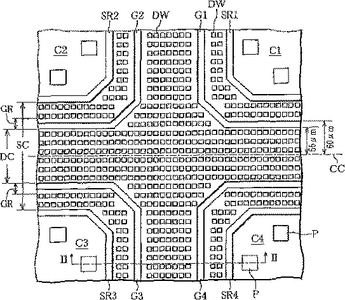

【課題】設計工数をほとんど掛けないで、CMP対策及び短時間光アニール対策の両対策に最適化されたダミーパターンを有する半導体集積回路装置を提供すること。

【解決手段】基板上に、メモリマクロ領域10及び機能回路領域20を有する半導体集積回路装置1において、機能回路領域20間、及び、メモリマクロ領域10と機能回路領域20との間に配置されるとともにダミーパターン41を含むダミーパターン領域40を備え、ダミーパターン41は、前記メモリセルアレイ領域におけるメモリセルパターン11の拡散層12、13及びゲート電極14と同等のパターンであり、ダミーパターン領域40におけるダミー拡散層42、43及びダミーゲート電極44の面積率は、メモリセルアレイ領域における拡散層12、13及びゲート電極14の面積率と同等以上である。

(もっと読む)

固体撮像装置

【課題】ブルーミング発生を抑え、かつ動作電圧を低電圧化することが可能な固体撮像装置を提供する。

【解決手段】固体撮像装置は、半導体基板に形成されたCCD型の固体撮像装置であって、オーバーフロードレイン構造のオーバーフローバリアの高さを規定する基板電圧Vsubを半導体基板に印加するVsub電圧発生回路26を備え、Vsub電圧発生回路26は、直列接続された複数の抵抗素子を含み、電圧分割により基板電圧を出力する抵抗回路と、前記複数の抵抗素子のいずれかに並列に接続されたポリシリコンのパターンであるヒューズ6とを含み、ヒューズ6は、コンタクト2が設けられた2つのジョイント基部1と、2つのジョイント基部1に挟まれて位置し、コンタクト2を介して電圧が印加されることにより電流が流れて溶断する溶断部10とを含み、溶断部10は、W方向の長さがジョイント基部1より小さく、W方向の長さが異なる領域を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】配線層の平坦性を維持しつつ、配線とインダクタとの間に生じる寄生容量を低減させた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に形成された第1の層間絶縁膜506と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた配線106と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた第1のダミーパターン107と、第1の層間絶縁膜506のうちインダクタ領域内に位置する部分に埋め込まれた第2のダミーパターン108と、第1の層間絶縁膜506の上方に形成された第2の層間絶縁膜と、第2のダミーパターン108の上方であって、第2の層間絶縁膜のうちインダクタ領域内に位置する部分に埋め込まれたインダクタ111とを備える。第2のダミーパターン108として金属が形成されていない。

(もっと読む)

半導体装置及びその配置配線方法

【課題】プリミティブセルに用いる金属配線層を増やすことなくプリミティブセルを小型化する。

【解決手段】素子形成領域に複数の回路素子によってプリミティブセルを構成する場合に、素子形成領域に前記プリミティブセルを構成するために必要な第1導電型の第1半導体ウェル領域及び第2導電型の第2半導体ウェル領域を並列的に複数個形成し、その上に前記素子形成領域の延在方向に一定ピッチで規則的に複数のゲート配線を配置したとき、形成された前記第1半導体ウェル領域及び前記第2半導体ウェル領域にL字型に屈曲された形状があるとき、これをL字形の屈曲部分を隣のウェル領域に延長してT字形の形状とし、延長した部分に、ソース電極とドレイン電極が共に電源ライン又はグランドラインに接続するダミーMOSトランジスタを構成し、プリミティブセルを構成する素子の接続を一層の金属配線層の金属配線を用いて行う。

(もっと読む)

半導体集積回路および半導体集積回路設計方法

【課題】チップサイズを縮小化すること。

【解決手段】第1領域に形成される活性領域1と第2領域に形成されるウェル領域2とトランジスタゲート電極3とダミーゲート電極5と、コンタクト8とを備えている。活性領域1とトランジスタゲート電極3とは、トランジスタを形成している。トランジスタゲート電極3とダミーゲート電極5とは、互いに平行である複数の直線にそれぞれ沿うように形成されている。ダミーゲート電極5は、その第2領域とその第1領域との両方に配置されるように形成されている。コンタクト8は、その第2領域に形成され、ウェル領域2に同電位である配線層6にダミーゲート電極5を電気的に接続している。このような装置は、活性領域1とウェル領域2とが配置される領域のレイアウトサイズを小さくすることができ、その結果、チップサイズを縮小化することができる。

(もっと読む)

設計支援装置、設計支援方法及び設計支援プログラム

【課題】複数のゲートが同一の拡散領域内に並列に配置されている場合において、トランジスタにおける、機械的応力による移動度の変動を見積もることを目的とする。

【解決手段】開示の装置は、回路データ生成手段と、パラメータ決定手段と、を備える。回路データ生成手段は、半導体集積回路における回路素子のレイアウト情報を基に、当該回路素子の物理特性を反映した回路データを生成する。パラメータ決定手段は、同一の拡散領域内に複数のゲートが設けられている場合において、ゲート電極として機能するゲートを有するトランジスタにかかる機械的応力に関するパラメータを、複数のゲートのレイアウト形状に応じて一意に決定する。ここで、回路データ生成手段は、当該パラメータを用いて、トランジスタにおける、機械的応力の影響を反映した移動度を求め、求められた移動度を回路データに反映する。

(もっと読む)

半導体集積回路装置のレイアウト検証方法

【課題】ランプアニール工程において温度のばらつきが発生しないように素子分離層の露出部の局所面積率を自動的に最適化すること。

【解決手段】本発明の一態様は、半導体集積回路装置のレイアウトを複数の局所領域に分割し、前記半導体集積回路装置を形成する半導体ウェハー表面おいて素子分離層が露出した領域の面積が、前記局所領域の面積に占める比率を、前記局所領域毎に計算し、前記比率に基づいて前記半導体集積回路装置のレイアウトを検証する半導体集積回路装置のレイアウト検証方法である。

(もっと読む)

半導体装置

【課題】半導体集積回路を構成するトランジスタの特性ばらつきを増大させずに、トランジスタの駆動力を向上できるようにする。

【解決手段】半導体装置は、基板の上に、複数のp型電界効果型トランジスタ、複数のn型電界効果型トランジスタ、P型基板コンタクト領域6及びN型基板コンタクト領域5を備えた集積回路からなる。PMOS活性領域1とNMOS活性領域2との間のウェル分離7、隣接するPMOS活性領域1同士の間の第1素子分離8a、隣接するNMOS活性領域2同士の間の第2素子分離8b、PMOS活性領域1とN型基板コンタクト領域5との間の第1素子基板コンタクト分離9a、NMOS活性領域2とp型基板コンタクト領域6との間の第2素子基板コンタクト分離9bは、それぞれ所定の幅を有する。

(もっと読む)

マーク設計装置および位置検出装置

【課題】 位置検出用のマークを設計する際の担当者の人為的なパラメータの設定ミスを防止し、人為的ミスによる歩留まり低下や稼動率の低下を防止する。

【解決手段】 基板上に形成され且つ位置検出装置によって検出されるマークを設計するマーク設計装置において、マークの種類やマークを構成する線の幅や本数を含むパラメータを編集する手段と、それらパラメータにより決まるマークのイメージを形成する手段と、前記パラメータを編集するための要素と前記形成されたマークのイメージとを1つの画面でGUI表示する表示手段とを設ける。

(もっと読む)

半導体集積回路の設計方法および半導体集積回路

【課題】

アンテナ基準を満足するMOSFETとダミーのMOS容量素子を形成することにより、アンテナ効果による素子破壊を防止する半導体集積回路の設計方法および半導体集積回路に関する。

【解決手段】

半導体基板4上に形成されたゲート配線層2と、トランジスタ形成領域上の前記ゲート配線層2下部に形成されたゲート酸化膜5と、半導体基板4上の前記ゲート配線層2下部に形成されたダミーゲート酸化膜13とを有し、前記ゲート酸化膜5と前記ダミーゲート酸化膜13を合わせた電荷許容量が、予め設定された値以上であることを特徴とする半導体集積回路である。

(もっと読む)

半導体装置の製造方法、半導体ウエハおよび半導体装置

歩留まり良く、スクライブ領域をダイシングできる半導体装置の製造方法を提供する。 半導体装置の製造方法は、(a)半導体素子を形成した複数のチップ領域と、前記複数のチップ領域を分離し、切断用ダイシング領域を内包するスクライブ領域とを有し、前記スクライブ領域内のダイシング領域より外側に各チップ領域を囲む様に溝形成領域が画定された半導体ウエハを準備する工程と、(b)前記半導体ウエハの上方に、層間絶縁膜と配線層とを交互に形成した多層配線構造とダミー配線を配置する工程と、(c)前記多層配線構造を覆って、パッシベーション層を含むカバー層を形成する工程と、(d)前記溝形成領域において、前記複数のチップ領域の各々を取り囲む溝を上方から、少なくとも前記パッシベーション層を貫通して形成する工程と、を含む。  (もっと読む)

(もっと読む)

ヒューズ及びヒューズの書き込み方法

【課題】 書き込み電圧低減のためにヒューズのジョイントを低抵抗化し又は溶断部を短くすると、書き込み電流増加のため、駆動用トランジスタのセル面積の増大が必要となり、チップ面積が大きくなる。

【解決手段】

ポリシリコンヒューズ100は、電圧印加により溶断される溶断部101aと、溶断部101aの一端に接続された+端子側ジョイント104aと、溶断部101aの他端に接続された−端子側ジョイント104bとを備え、前記電圧印加の際に高電圧となる+端子側ジョイント104aは、−端子側ジョイント104bに比べて低い抵抗と高い熱伝導性とを有している。

また、ポリシリコンヒューズ100の+端子側ジョイントに対して直列に電流制限抵抗を接続し、該電流制限抵抗を介して電圧パルスを印加することにより、溶断部101aの溶断の際にポリシリコンヒューズ100流れる電流を所定の範囲に制限しながら書き込みを行なう。

(もっと読む)

1 - 13 / 13

[ Back to top ]